(54) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Умножитель частоты | 1984 |

|

SU1238070A1 |

| Умножитель частоты | 1984 |

|

SU1257642A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Умножитель частоты следования периодических импульсов | 1980 |

|

SU980094A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Умножитель частоты | 1984 |

|

SU1179334A1 |

| Цифровой умножитель частоты | 1984 |

|

SU1192106A1 |

| Цифровой умножитель частоты | 1980 |

|

SU930575A2 |

| Умножитель частоты | 1979 |

|

SU811250A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в частотно-измерительной аппаратуре.

Известен умножитель частоты, содержащий реверсивный счетчик, преобразователь коднапряжение, управляемый генератор и счетчик обратной связи 1.

Недостатком данного умножителя является малый диапазон изменения коэффициента умножения, низкое быстродействие в результате изменения козффивдента деления счетчика обратной связи и возникновения при этом дополнительного переходного процесса.

Наиболее близким по технической сущности к, данному изобретению является устройство, содержащее счетчик полупериода, соединенный через первую группу поразрядных вентидей, управляющие входы которых связаны с блоком управления, с входами регистра памяти, выходы которого через вторую группу поразрядных вентилей подключены к соответствующим разрядным входам дополнительного счетчика, выход которого чефез элемент ИЛИ соединен с выходом устройства и управляющими входами

второй группы поразрядных вентилей, нуль-Орган, вход которого соединен с источником умножаемой частоты, а выход - со счетным входом первого триггера, подключенного к первому входу блока управления и генератор опорной частоты 2.

Недостатком известного устройства является низкая точность умножения.

Целью изобретения является повьщ ение точности умножения.

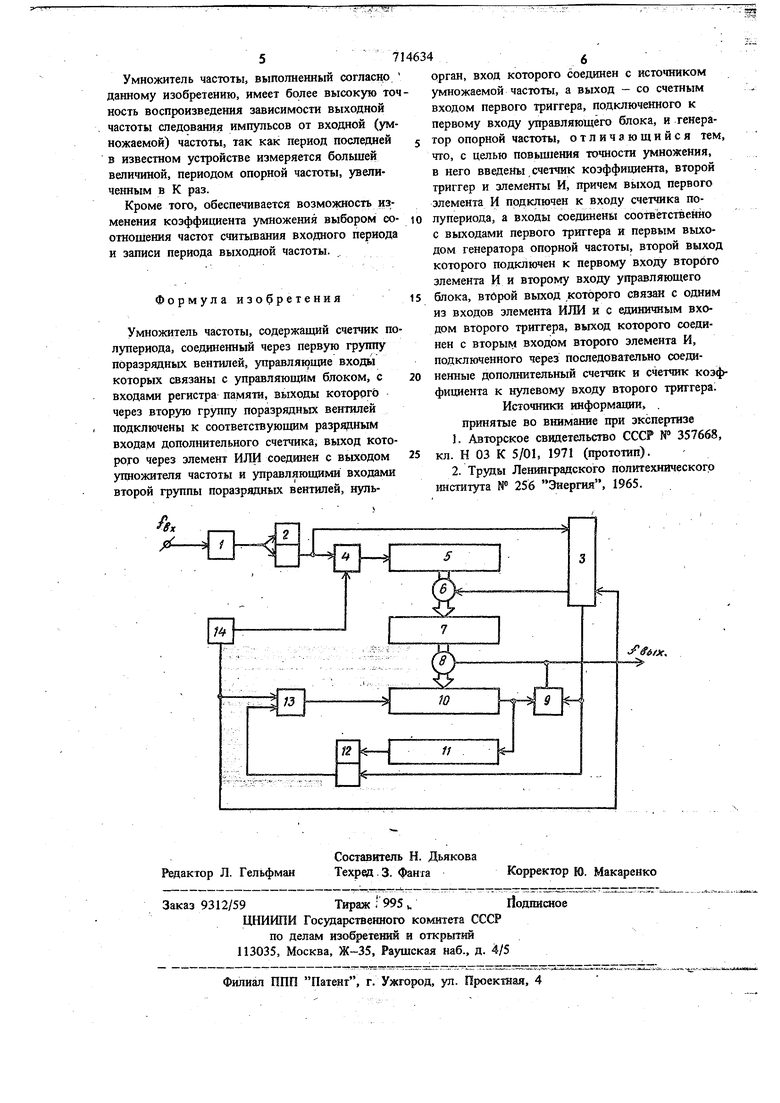

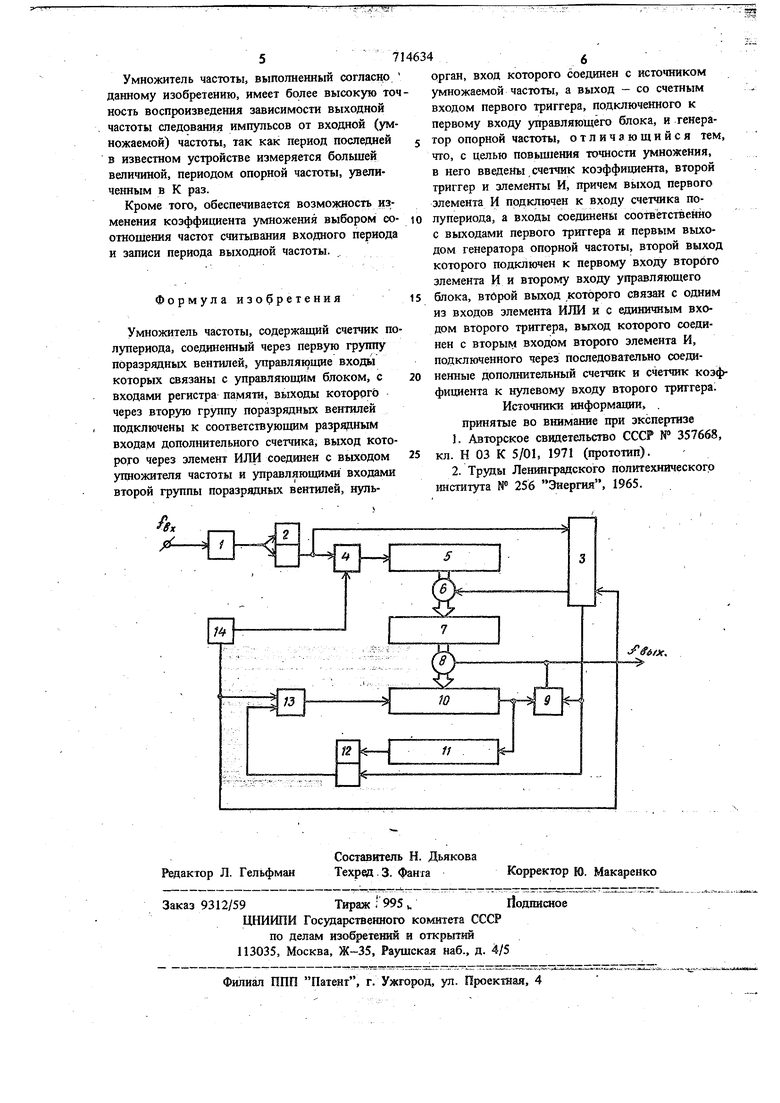

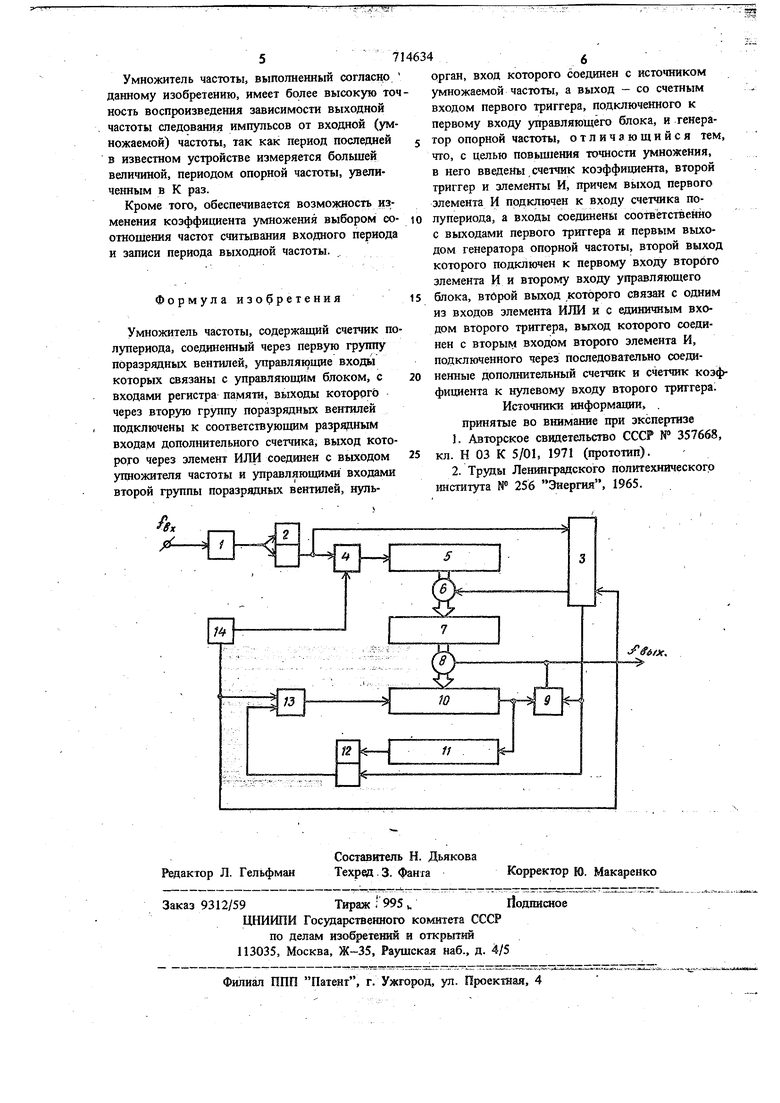

Для дрсшжения поставленной цели в устройство, содержащее счетчик полупериода, соединенный через первую группу поразрядных вентилей, управляющие входы которых связаны с управляющим блоком, с входами регистра памяSти, выходы которого через вторую группу поразрядных вентилей подключены к соответствующим разрядным входам дополнительного счетчака, выход которого через элемент ИЛИ шединен с выходом умножителя частоты и управляющими входакш второй группы цоразрядных вентилей, нуль-орган, вход которого соединен с источником умножаемой частоты, а выход со счетным входом первого триггера, подклю-: ченного к первому входу управляющего блока, и генератор опорной частоты, введены счетчик коэф фициента, второй триггер и элементы И, Причем выход первого элемента И подключен k входу счетчика Полупериода, а входы соединеШ соответственно с выходами первого триггера и первым выходом генератора опорной частоты, 1второй вйход которого подключен к первому входу второго элемента И и второму (вховд управляющего блока, второй выход кото рого связан с одним из входом, элемента ИЛИ 1Г с единичным входом второго триггера, выЯоД которого соединен с вторым входом второго элемента И, подключенного через последовательно соединенные дополнительный счетчик и счетчик коэффициента к нулевому входу второго триггера. На чертеже представлена структурная электрическая схема устройствам Умножитель частоты содержит нуль-орган 1, . первый триггер 2, выход которого соединен с ртравляющим блоком 3 и через элемент И 4 с входом счетчика полупериода 5 (умножаемой частоты). Выходы разрядов счетчика полупериода 5 через первую группу поразрядных вентилей 6 соединены с регистром памяти 7, который через вторую группу поразрядных вентилей 8, управляемых с выхода элемента ИЛИ 9, соединены с дополнительным счетчиком 10, соединенным выходом с входом счетчика коэф фициента 11, подключенного через второй триггер 12 к одному из входов элемента И 13 второй Вход которого подключен к генератору опорной частоты 14, а выход - к входу допол нительного счетчика 10. Второй выход генерато ра опорной частоты 14 соединен с элементом Устройство умножения частоты работает следуйдим образом. Сигнал умножаемой синусоидальной частоты fgx поступает на нуль-орган 1, который выделяет момент прохождения входного сигнала через нуль и формирует ймпульсы, период повторениякоторых равен периоду частотьт вх одного сигнала. Импульсы с нуль-органа поступают на счетный вход первого триггера 2, который делит частоту на два. выходной сигнал первого триггера 2 поступа ет на вход элемента И 4 и управляющий блок 3. -Элемент И 4, заправляемый по одному входу первым триггером 2, а по другому входу импульсами с генератора опорной частоты 14 с частотой заполнения fgan формирует на свое . выходе пачку импульсов N эаг1 вх Управляющий блок 3 по сигналу: первого триггера 2 форгаируьтуп|5 ляйЩйе сигналы «1 и tfj. Пачка импульсов, сформированная на элементе И 4, поступает на вход счетчика полупериода 5, на разрядных выходах которого образуется код, эквивалентный полупериоду умножаемой частоты с точностью до периода частоты заполнения f3an- Этот код парафазно (принудительно) переписывается через первую группу поразрядных вентилей 6, управляемых с выхода управляющего блока 3, в регистр памяти 7, где хранится в течение периода умножаемЪй частоты. Сигналом ofj с другого выхода управляющего блока 3, который прохоДИ1 на выход через элемент ИЛИ 9, информация из регистра памяти 7 переписывается обратным кодом в дополнительный счетчик 10. Этим же импульсом производится запуск второго триггера 12, который открывает элемент И 13, разрешая прохождение частоты считывания fc4HT ™ вход дополнительного счётчика 10. К записанному в дополнительный счетчик IP коду добавляются импульсы до его переполнения, и выделивщийся на выходе импульс вновь через элемент ИЛИ 9 списьшает с регистра памяти код, эквивалентный полупериоду . умножаемой частоты, в дополнительный счетчик 10. Сигнал переполнения дополнительного счетчика 10 поступает на вход счетчика коэффициента (умножения) 11, который, отсчитав число импульсов, равное двойному коэффициенту умножения, опрокидывает второй триггер 12, а тот в свою очередь запрещает поступле считывания а вход дополни тельного счетчика 10. В рассмотренном варианте отнощение частот считывания и записи должно быть равно коэффициенту умножения Например, при умножении частотыч fg 1 кГц, коэффициент умножения К 4 вых 4 МГц . Частота считывания выбирается из условия необходимой точности умножения. Допустим счит 250 кГц, следовательно зап мГц, емкость счетчика коэффициента умножения в этом случае будет равна 3 разрядам. Если необходимо повысить К, не изменяя соотнощение частот записи fgan и считьюания fсчит следует организовать перепись из регистра памяти в дополнительный счетчик со сдвигом влево (в сторону младщего разряда), тогда число сдвигов определит деление на 2. Счетчик коэффициента умножения в этом случае необходимо увеличить на п разрядов. Относительная ощибка умножения при описанном методе равна и меньще чем в известНь1Х схемах, где гу длительность периода умножения частоты.

Авторы

Даты

1980-02-05—Публикация

1973-12-29—Подача