Изобретение относится к автоматике и вычислительной технике и может быть использовано в аппаратуре для моделирования устройств с динамически изменяемыми параметрами.

Цель изобретения - расширение функциональных возможностей за счет обеспечения умножения частоты на динамически изменяемый коэффициент.

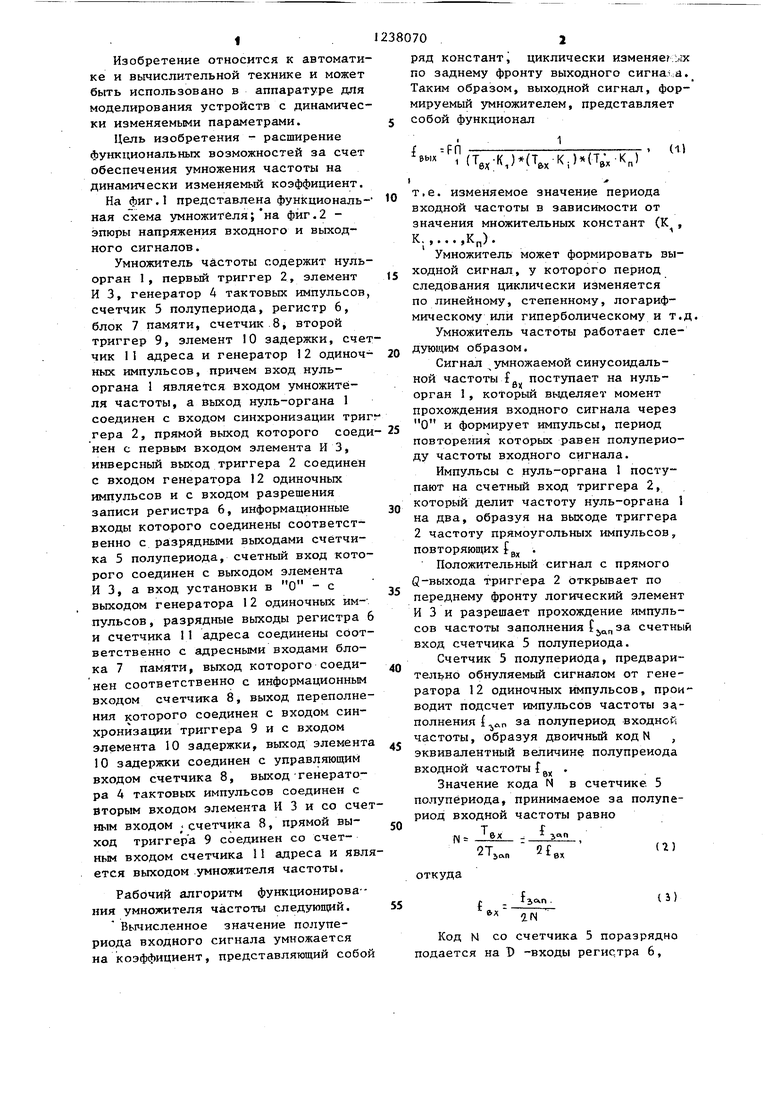

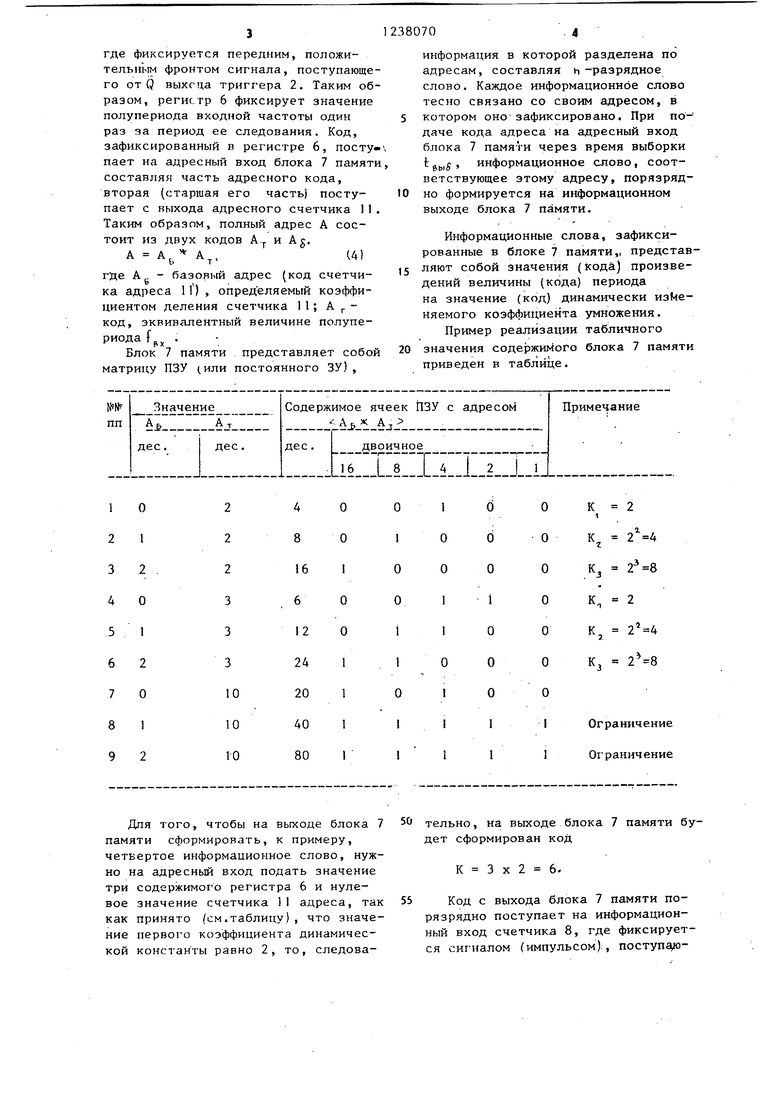

На фиг.1 представлена функциональная схема умножителя; на фиг.2 - эпюры напряжения входного и выходного сигналов.

Умножитель частоты содержит нуль- орган I, первый триггер 2, элемент ИЗ, генератор 4 тактовых импульсов, счетчик 5 полупериода, регистр 6, блок 7 памяти, счетчик.8, второй триггер 9, элемент 10 задержки, счетчик 11 адреса и генератор 12 одиноч- ных импульсов, причем вход нуль- органа 1 является входом умножителя частоты, а выход нуль-органа 1 соединен с входом синхронизации триг гера 2, прямой выход которого соеди нен с первым входом элемента ИЗ, инверсный выход триггера 2 соединен с входом генератора 12 одиночных импульсов и с входом разрешения записи регистра 6, информационные входы которого соединены соответственно с разрядными выходами счётчика 5 полупериода, счетный вход которого соединен с выходом элемента И 3, а вход установки в О - с выходом генератора 12 одиночных импульсов , разрядные выходы регистра 6 и счетчика I1 адреса соединены соответственно с адресными входами блока 7 памяти, выход которого соеди- нен соответственно с информационным входом счетчика 8, выход переполнения которого соединен с входом синхронизации триггера 9 и с входом элемента 10 задержки, выход элемента 10 задержки соединен с управляющим входом счетчика 8, выход генератора 4 тактовых импульсов соединен с вторым входом элемента И 3 и со счетным входом -счетчика 8, прямой вы- ход триггера 9 соединен со счетным входом счетчика 11 адреса и является выходом умножителя частоты.

Рабочий алгоритм функционирова-- ния умножителя частоты следуюа ий.

Вычисленное значение полупериода входного сигнала умножается на коэффициент, представляющий собой

ряд констант i циклически изменяе ;:,. х по заднему фронту выходного сигнал.а. Таким образом, выходной сигнал, формируемый умножителем, представляет собой функционал

1

b,x ; (T,,;K,)(T,,-Ki)(T,

(И

т.е. изменяемое значение периода входной частоты в зависимости от значения множительных констант (К , К, ,... ,Kpj) .

Умножитель может формировать выходной сигнал, у которого период следования циклически изменяется по линейному, степенному, логарифмическому или гиперболическому и т.д.

Умножитель частоты работает следующим о б ра 3 ом.

Сигнал умножаемой синусоидальной частоты fg поступает на нуль- орган 1, который выделяет момент прохождения входного сигнала через О и формирует импульсы, период повторения которых равен полупериоду частоты входного сигнала.

Импульсы с нуль-органа 1 поступают на счетный вход триггера 2, который делит частоту нуль-органа 1 на два, образуя на выходе триггера 2 частоту прямоугольных импульсов, повторяюпщх f g. .

Положительный сигнал с прямого Q-выхода триггера 2 открьшает по переднему фронту логический элемент И 3 и разрешает прохождение импульсов частоты заполнения , за счетный вход счетчика 5 полупериода.

Счетчик 5 полупериода, предварительно обнуляемый сигналом от генератора 12 одиночных импульсов, прои водит подсчет импульсов частоты заполнения I дп за полупериод входной частоты, образуя двоичный код N , эквивалентный величине полупреиода входной частоты f ц

Значение кода N в счетчике 5 полупериода, принимаемое за полупериод входной частоты равно

ex

V„ 2

ex

(2)

откуда

f

f.

(3)

лх.

1злп .

ам

Код N со счетчика 5 поразрядно подается на D -входы регистра 6,

где фиксируется передним, положи- тельиьгм фронтом сигнала, поступающего отQ выхсца триггера 2. Таким образом, регистр 6 фиксирует значение полупериода входной частоты один раз за период ее следования. Код, зафиксированный в регистре 6, посту« пает на адресный вход блока 7 памяти составляя часть адресного кода, вторая (старшая его часть) поступает с выхода адресного счетчика 11. Таким образом, полный адрес А состоит из двух кодов А. и Ag.

А А,(4)

где А - базовый адрес (код счетчика адреса 1f), определяемый коэффициентом деления счетчика 11; А - код, эквивалентный величине полупериода fр .

Блок 7 памяти представляет собой матрицу ПЗУ (ИЛИ постоянного ЗУ) ,

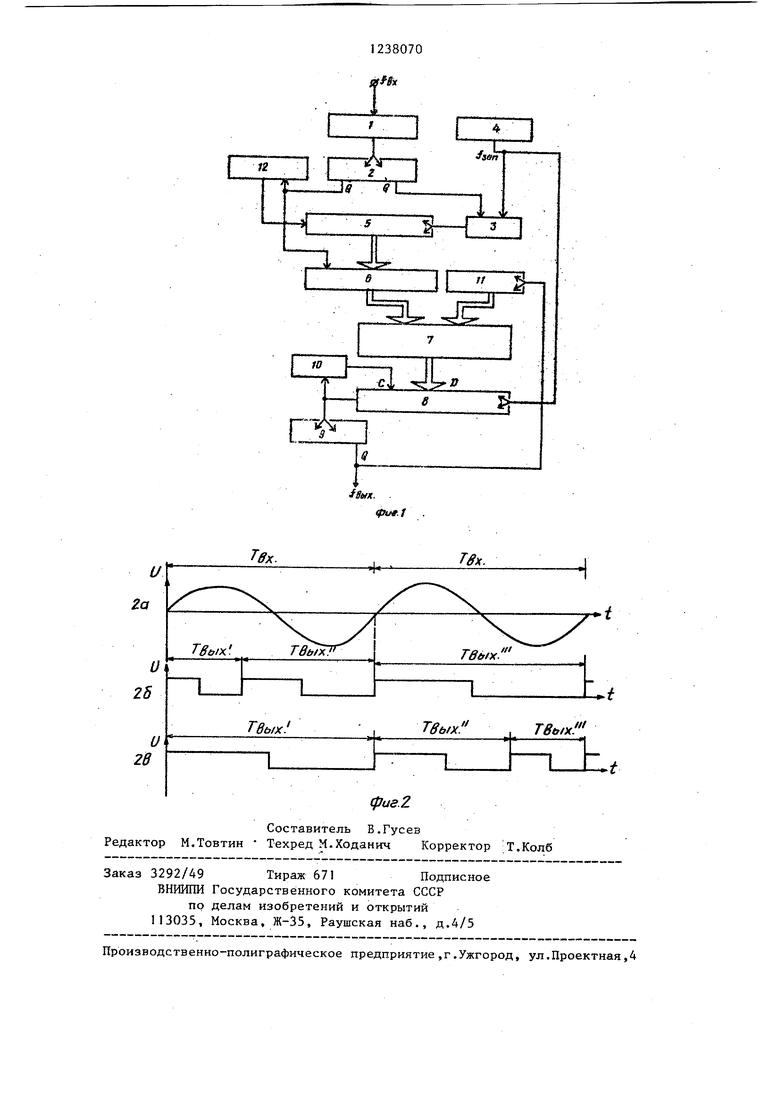

Для того, чтобы на выходе блока 7 памяти сформировать, к примеру, четвертое информационное слово, нужно на адресный вход подать значение три содержимого регистра 6 и нулевое значение счетчика 11 адреса, так как принято (см.таблицу), что значение первого коэффициента динамической константы равно 2, то, следова38070.4

информация в которой разделена по адресам, составляя h-разрядное слово. Каждое информационное слово тесно связано со своим адресом, в 5 котором ОНО зафиксировано. При по- даче кода адреса на адресный вход блока 7 памяти через время выборки информационное слово, соответствующее этому адресу, порязряд- tO но формируется на информационном выходе блока 7 памяти.

Информационные слова, зафиксированные в блоке 7 памяти,, представ- (5 ляют собой значения (кода) произведений величины (кода) периода на значение (код) динамически изйе- няемого коэффициента умножения. Пример реализации табличного 20 значения содержимого блока 7 памяти приведен в таблице.

тельно , на выходе блока 7 памяти будет сформирован коД

К 3 X 2 6.

Код с выхода блока 7 памяти по- рязрядно поступает на информационный вход счетчика 8, где фиксируется сигналом (импульсом), поступаю

щим с выхода элемента 10 задержки на управляющий вход счетчика 8.

Счетчик 8 может быть выполнен ка вычитающим, так и суммирующим. При этом, если счетчик 8 выполнен суммирующим, то с выхода блока 7 памяти должна сниматься информация в инверном коде, если счетчик В выполнен вычитающим, то информация должна считываться в прямом коде.

Импульс с выхода переполнения счетчика 8 поступает через элемент 10 задержки на управляющий вход счетчика 8 и фиксирует в последнем содержимое блока 7 памяти, подаваемое на его информационный вход. По переднему фронту сигналов триггера 9, счетчик 11 адреса меняет свое состояние, меняя тем самым на еле- дующий коэффициент динамической константы. Таким образом-, в следующем цикле будет обрабатываться значение (см.таблицу, П.5).

К 3 X А 12,

На фиг.2 приведены эпюры входного и выходного сигналов умножител частоты с динамическим коэффициентом умножения, на фиг.2о- изменения периода Tg входной частоты, на фиг.2s - эпюра изменения периода ТО.У выходного сигнала при умножении

на динамический коэффициент с динам .ческими константами:

I

3

г

к 1.

При этом, согласно выражению (1) ,

t.

1

вьи 3 т,,.. я 1 ,5 Т,., ж Т

0Х в

На фиг.2в представлен тот же выходной сигнал, но в коэффициенте умножения которого представлены динамические константы

1

T«v 1,5 Т., жЗ Т,

ex

Это можно осуществить двумя путями - перепрограммированием блока 7 памяти или изменением фазы счета адресного счетчика 11. Количество периодов полного (результирующего) выходного сигнала зависит от коэффициента счета адресного счетчика 1I.

10

j20

25

Q

5

0

5

0

5

Таким образом, умножитель частоты обеспечивает умножение на динамический коэффициент умнржения, состоящих из двух или нескольких вычислительных констант.

Формула изобретения

Умножитель частоты, содержащий блок памяти, генератор тактовых импульсов, нуль-орган, первый триггер, счетчик полупериода, генератор одиночных импульсов, элемент И и буферный регистр, информационные входы которого соединены соответственно с разрядными выходами счетчика полупериода, счетный вход которого соединен с выходом элемента И, первый вход элемента И соединен с прямым выходом первого триггера, вход синхронизации которого соединен с выходом нуль-органа, вход которого является входом умножителя, второй вход элемента И соединен с выходом генератора тактовых импульсов, а инверсный выход пе,рвого триггера соединен с управляющим входом буферного регистра и с входом генератора одиночных импульсов, выход которого соединен с входом установки в О счетчика полупериода, о т л и- чающийся тем, что, с целью расширения функциональных возможностей за счет обеспечения умножения частоты на. динамически изменяемый коэффициент умножения, в него введены счетчик, второй триггер, счетчик адреса и элемент задержки, причем разрядные входы адреса блока памяти соединены соответственно с разрядными выходами буферного регистра и счетчика адреса, разрядные вькоды блока памяти соединены соответственно с информационными входами счетчика, выход переполнения которого соединен с входом синхронизации второго триггера и с входом элемента задержки, выход которого соединен с управляющим входом счетчика, прямой выход второго триггера соединен со счетным входом счетчика адреса и является выходом умножителя, .а выход генератора тактовых импульсов соединен со счетным входом счетчика.

10

г:

Тех.

1 JL

8

fSMX. .

фи.Г

.

га

TBt,iK(

Твь7)Г.

25

Tffff/x.

i

и

2В

Твых

Редактор М.Товтин

(риг.2

Составитель В.Гусев

Техред М.Ходанич Корректор Т.Колб

Заказ 3292/49 Тираж 671 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие.г.Ужгород, ул.Проектная,4

Т8ых .

Ill

I/ t/слгл.

F4IL.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Умножитель частоты | 1984 |

|

SU1257642A1 |

| Умножитель частоты | 1973 |

|

SU714634A1 |

| Устройство для сопряжения цифровой и аналоговой вычислительных машин | 1983 |

|

SU1128273A1 |

| Генератор линейного напряжения | 1986 |

|

SU1354403A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Генератор функциональных зависимостей | 1983 |

|

SU1130853A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Генератор последовательности импульсов | 1983 |

|

SU1231583A1 |

| Устройство для формирования характеристических матриц | 1988 |

|

SU1596334A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в преобразующей аппаратуре для аппаратного моделирования устройств с динамически изменяемыми параметрами. Целью изобретения является расширение функциональных возможностей за счет обеспечения умножения частоты на динамически изменяемый коэффициент умножения . Период входной частоты умножается последовательно на коэффи-- циенты, представляющие собой ряд констант, циклически изменяемых под воздействием выходного сигнала. купность этих констант идентифицируется с динамическим коэффициентом умножения. 2 ил., 1 та0л. (Л to О9 00

| Станок для изготовления гибких металлических шлангов с гофром по винтовой линии | 1945 |

|

SU71463A1 |

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-10-15—Подача