выходы блока памяти микропрограмм соединены с входами соответствующих элементов И первой группы, выходы которых соединены соответственно с входами упраВлейия реядамом записи старших и младших разрядов буферного

регистра, восьмой, девятый, десятый И одиннадцатый выходы блока памяти микропрограмм соединены соответственно с адресными входами первого и второго блоков памяти и первого и второго мультиплексоров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1367013A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее табличный блок умножения и табличный блок суммирования, о тличающееся тем, что, с целью сокращения оборудования, в него введены два блока памяти, два мультиплексора, буферный регистр и блок микропрограммного управления, который содержит триггер, управляемый генератор импульсов, счетчик, блок памяти микропрограмм и две группы элементов И, причем входы множимого и множителя устройства соединены с первыми информационными входами первого и второго мул.ьтиплексоров соответственно, вторые информационные входы которых соединены с выходом пер-, вого блока памяти, первый информаци- онньм вход которого соединен с выходом табличного блока умножения и с первым информационным входом второго блока памяти, второй информационный вход которого соединен с вторым информационным входом первого блока памяти и выходом табличного блока суммирования, информационный вход которого соединен с информационным входом .табличного блока умножения, выходом произведения устройства и выходом буферного регистра, первый информационный вход которого соединен с выходом первого мультиплексора, третий информационный вход которого соединен с выходом второго блока памяти и третьим информационным входом второго мультиплексора, выход которого соединен с вторым информационным входом буферного регистра, а в блоке микропрограммного управления тактовый вход устройства со- с единен с установочным входом, триггера, прямой выход которого (Л соединен с управляюпи1м входом управляемого генератора импульсов, прямой выход которого соединен с управляющим входом элементов И первой группы и счетным входом счетчика, вход сброса которого соединен с инверсным выходом триггера, а выходы Vj с адресными входами блока памяти микО) ропрограмм, первый, второй, третий и четвертый выходы которого соединены 00 1C с входами соответствующих элементов И второй группы, управляющий вход коел торых соединен с инверсным выходом управляемого генератора импульсов, выходы элементов И второй группы входами соединены соответственно с управления режимом записи первого и второго блоков памяти, с входом сброса триггера и выходом управления выводом результата умножения устрой- ства, пятый вькод блока памяти микропрограмм соединен с управляющими входами табличных блоков умножения и суммирования, шестой и седьмой

1

Изобретение относится к вьгчисли тельной технике и может быть использовано в универсальных вычислительных машинах.

Целью изобретения является сокращение оборудования.

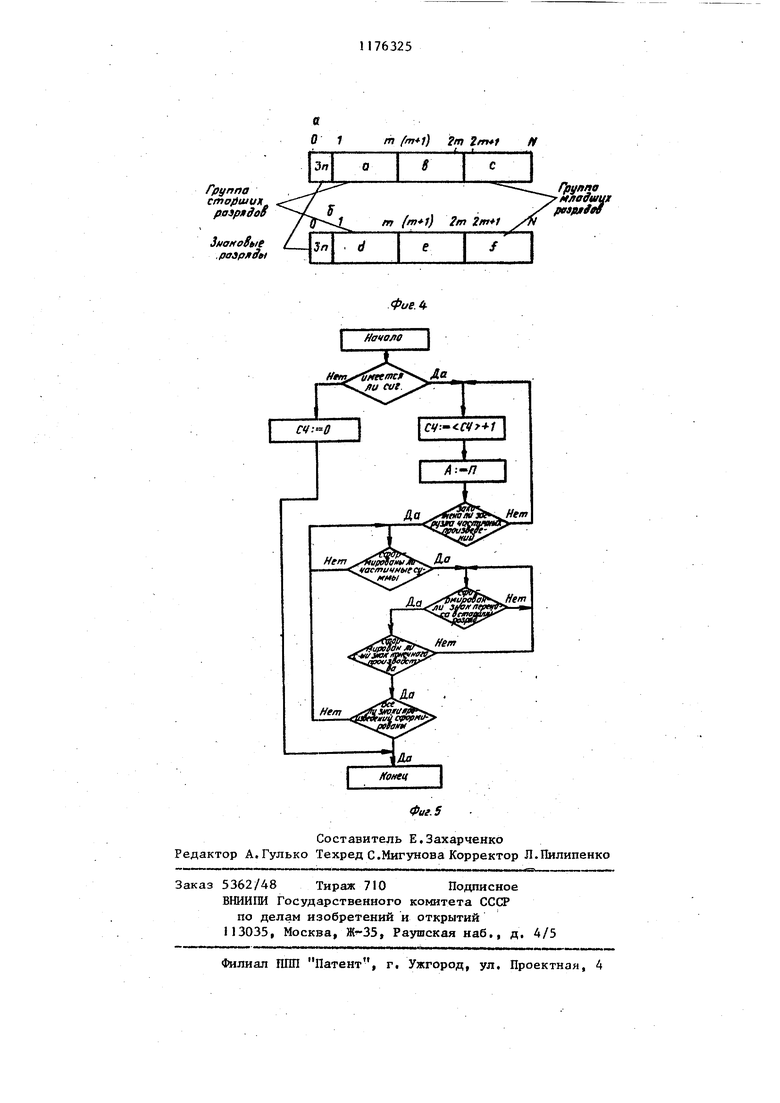

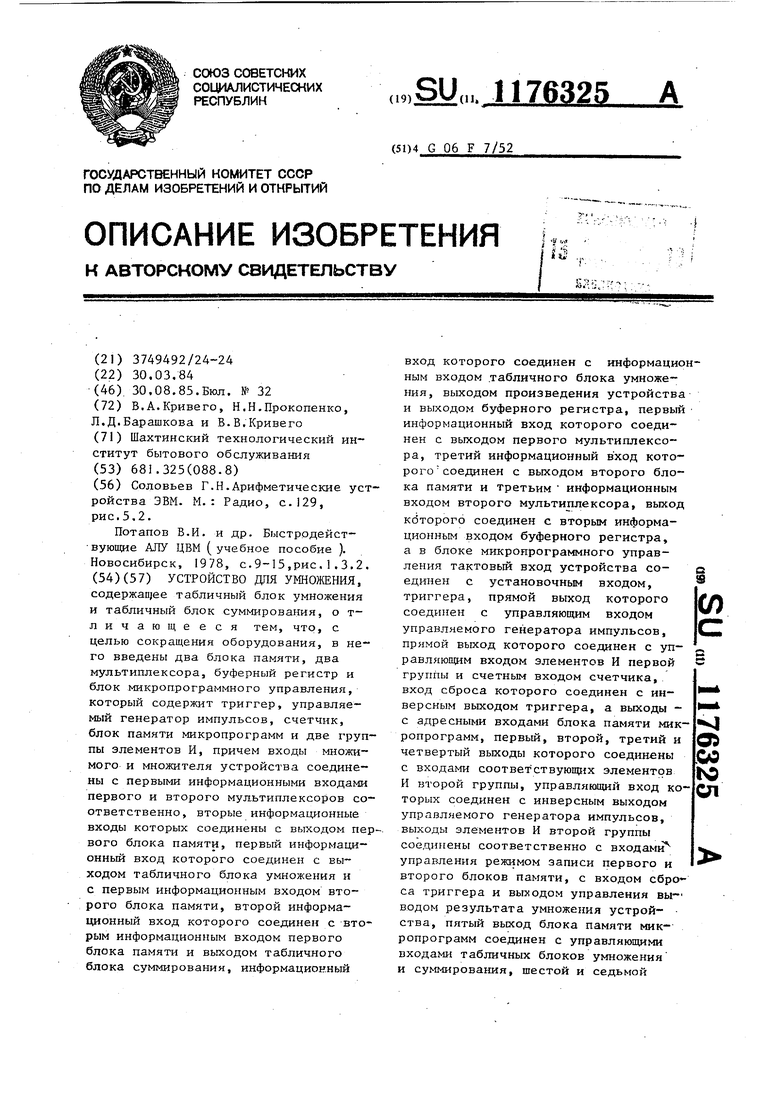

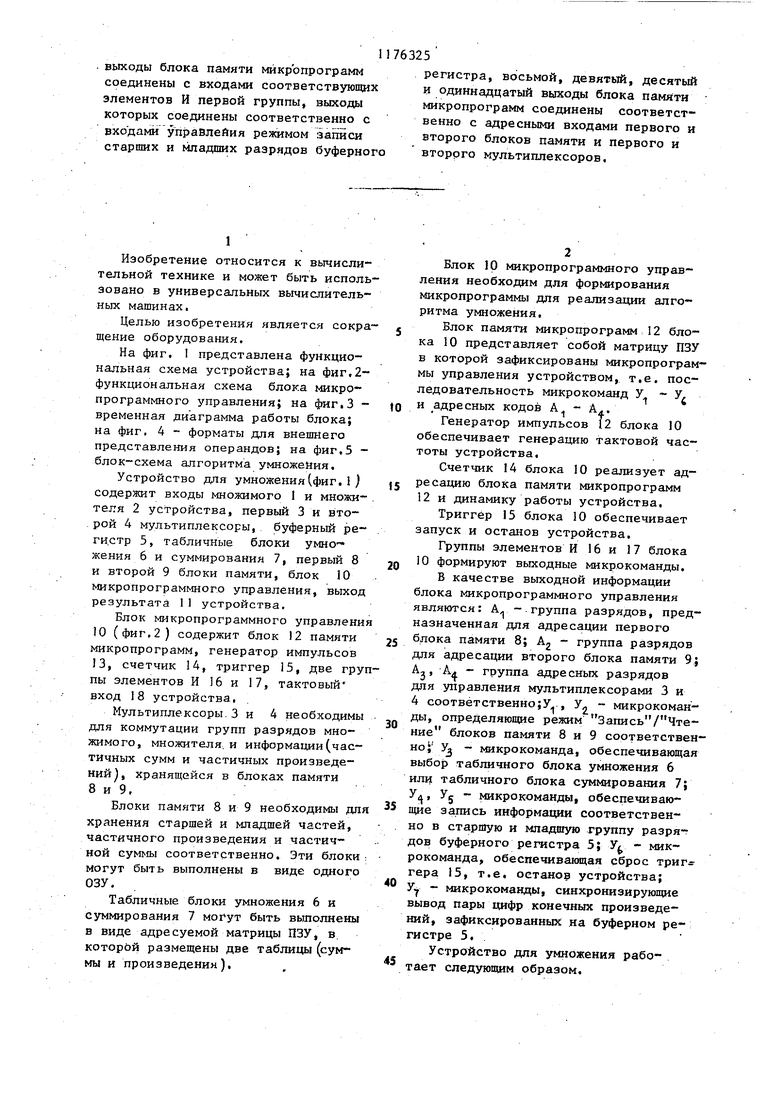

На фиг, I представлена функциональная схема устройства; на фиг,2функциональная схема блока микропрограммного управления; на фиг.З временная диаграмма работы блока; на фиг, 4 - форматы для внешнего представления операндов; на фиг,5 блок-схема алгоритма умножения.

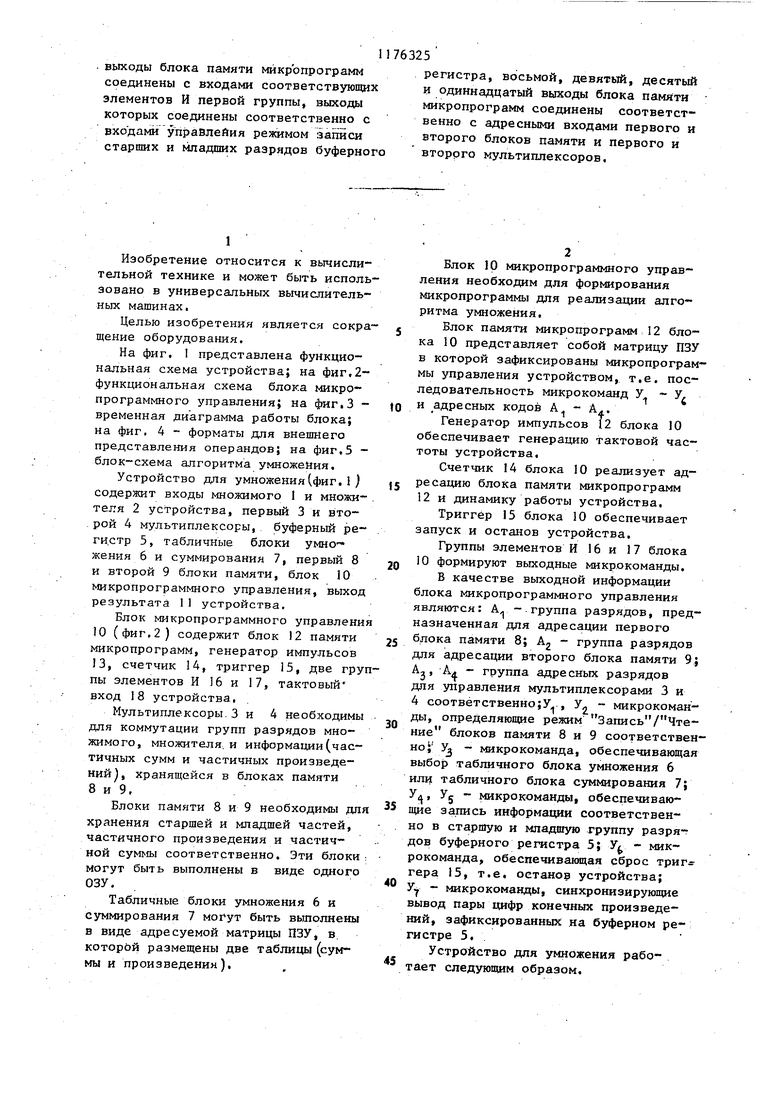

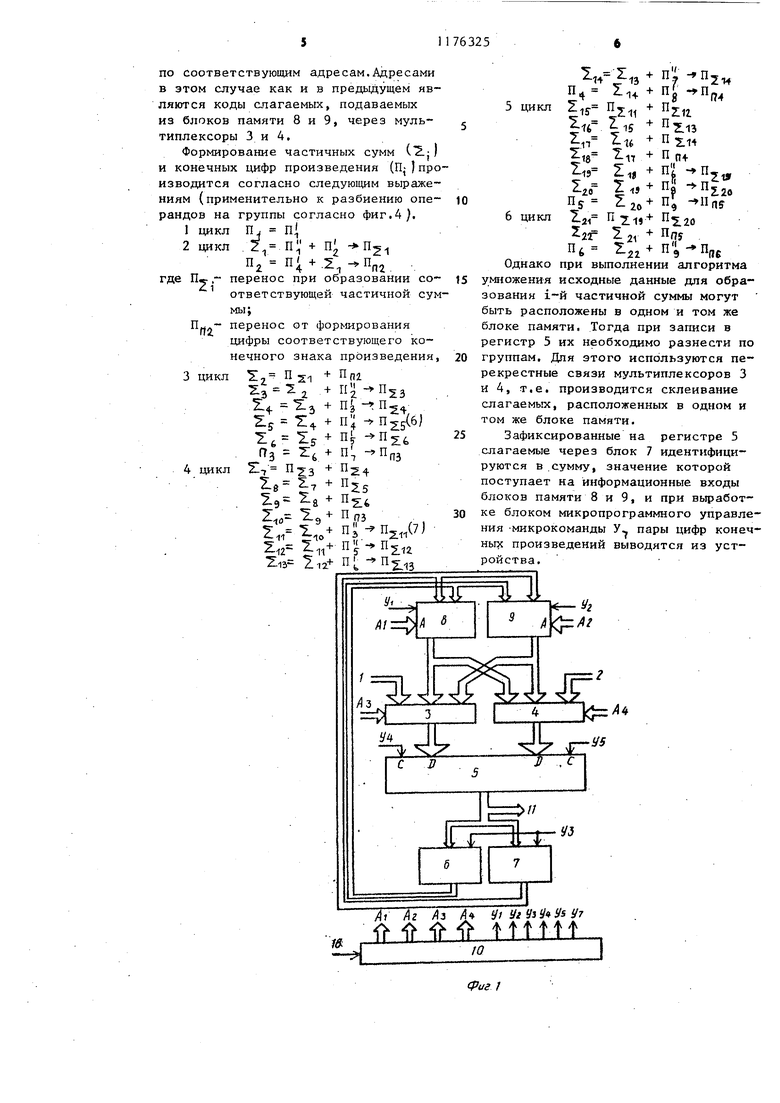

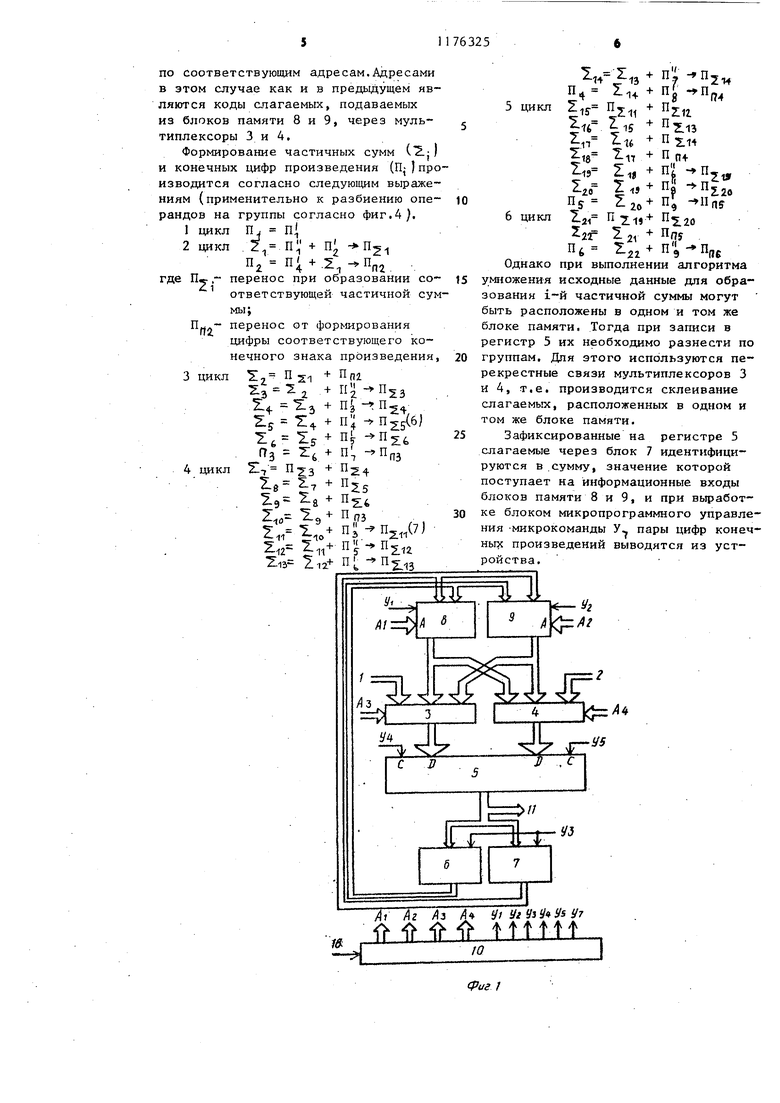

Устройство для умножения(фиг.1 ) содержит входы множимого 1 и множителя 2 устройства, первый 3 и второй 4 мультиплексоры, буферный реги.стр 5, табличные блоки умно™ жения 6 и суммирования 7, первый 8 и второй 9 блоки памяти, блок 10 микропрограммного управления, выход результата 11 устройства.

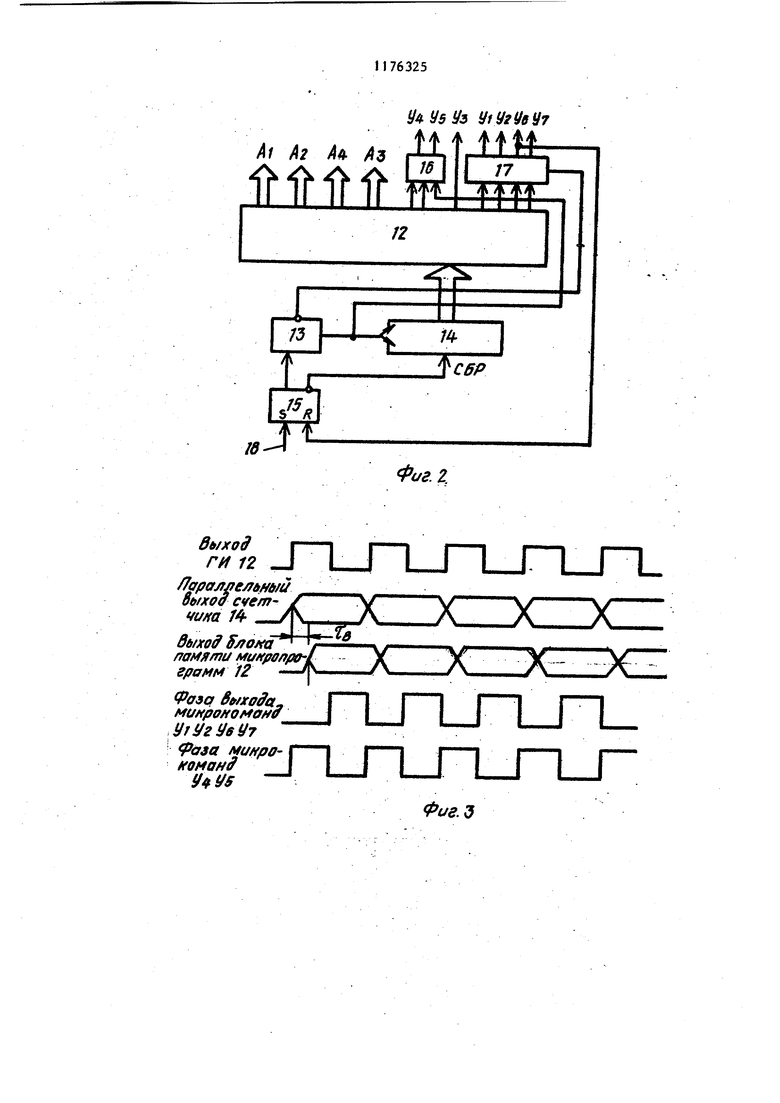

Блок микропрограммного управлени 10 (фиг,2) содержит блок 12 памяти микропрограмм, генератор импульсов 13, счетчик 14, триггер 15, две групы элементов И 16 и 17, тактовый вход 18 устройства.

Мультиплексоры.3 и 4 необходимы для коммутации групп разрядов множимого, множителя, и информации (частичных сумм и частичных произведений, хранящейся в блоках памяти 8 и 9,

Блоки памяти 8 и 9 необходимы дп хранения старшей и младшей частей, частичного произведения и частичной суммы соответственно. Эти блоки могут быть выполнены в виде одного ОЗУ,

Табличные блоки умножения 6 и суммирования 7 могут быть вьтолнены в виде адресуемой матрицы ПЗУ, в. которой размещены две таблицы (суммы и произведения).

Блок 10 микропрограммного управления необходим для формирования микропрограммы для реализации алгоритма умножения,

Блок памяти микропрограмм 12 блока 10 представляет собой матрицу ПЗУ в которой зафиксированы микропрограммы управления устройством, т.е, последовательность микрокоманд У., У/ и адресных кодоё А. - А..

Генератор импульсов 12 блока 10 обеспечивает генерацию тактовой частоты устройства.

Счетчик 14 блока 10 реализует ад- ресацию блока памяти микропрограмм 12 и динамику работы устройства.

Триггер 15 блока 10 обеспечивает запуск и останов устройства.

Группы элементов И 16 и 17 блока 10 формируют выходные микрокоманды,

В качестве выходной информации блока микропрограммного управления являются: А, - группа разрядов, предназначенная для адресации первого блока памяти 8; Aj - группа разрядов для адресации второго блока памяти 9; А,, АЛ - группа адресных разрядов для управления мультиплексорами 3 и 4 соотвётственно;У.., У„ - микрокоманды, определяющие режим Запись / Чтение блоков памяти 8 и 9 соответственно i 5 - микрокоманда, обеспечивающая выбор табличного блока умножения 6 или табличного блока суммирования 7; Уд, У - микрокоманды, обеспечивающие запись информации соответственно в старшую и младшую группу разрядов буферного регистра 5; У - микрокоманда, обеспечивающая сброс триг гера 15, т,е, останов устройства;

У - микрокоманды, синхронизирующие вывод пары (ИФР конечных произведений, зафиксированных на буферном регистре 3.

Устройство для умножения работает следующим образом. На вход устройства подаются чис ленные значения множимого и множите ля, предварительно приведенные к по ложительному знаку Поступление опе рандов синхронизируется поступлением синхроик:пульсов СИ, передним фро том которого устанавливается в единичное состояние триггер 15, сигналом с прямого выхода которого производится запуск генератора импульсов 13,-а сигналом с инверсного выхода снимается блокировка со счетчика 14. . Серия тактирующих импульсов с прямого выхода генератора импульсо 13 поступает на счетный вход счетчика 14 и путем подсчета их на счет чике 14 производится перебор (в естественном порядке/ адресных кодо блока памяти микропрограммы 12, который осуществляется до тех пор, по ка из блока памяти микропрограмм; на вход триггера 15 не поступит №1крокоманда У, которая обнуляет триггер, а он в свою очередь обнуляет содержимое счетчика 14. За.время полного перебора на выходах блока микропрограммного управления формируется микропрограмма Всю микропрограмму можно условно разбить на несколько циклов. На пер вом цикле производится запись операндов ( множимого и множителя ) в блоки памяти с одновременным вычислением частичных произведений. Количество шагов N в этом цикле равно: -(Г где п - разрядность операндов; m - разрядность групп(а,Ь,с и т.д., на которые они раз делены. Согласно фиг.4 частичные произведения (п )будут записаны в следую щей форме: П cf п;п;; nj bf ; П| af П«Пз Il4 се ЩЦ П| be ,(2) П ае П2Щ; П7 cd ПтП;; П| bd I,, ad где Ilj - старшие разряды частичного произведения; младщие разряды частичного произведения. Следовательно, в цикле записи операндов согласно выражениям (И и: (2) блоков микропрограммного управления будет выполнено N одинаковых шагов, на каждом из которых счетчиком 14 сформируется соответствующий адрес микрокомандного слова. По зтому адресу из блока памяти микропрограмм 12 выбираются соответствующие коды А, и А, которые скоммутируют мулцЕятиплексоры 3 и 4. Содержимое соответствующих групп разрядов множимого и множителя с выхода мультиплексора поступит на информационные входы регистра 8, где будут зафиксированы микрокомандами Уд и У по задним их фронам. Причем микрокоманда У записывает содержимое m разрядов, поступающих от мультиплексора 3, а микрокоманда УС m разрядов, поступающих от мультиплек-t сора 4, Таким образом, в регистре 5 зафиксированы цифры исходных операндов, которые по мере поступления подаются на входы табличного блока умножения 6, на адресный вход которого пода- ется микрокоманда У, 1, Частичные произведения на выходе табличного блока умножения 6 удерживаются до тех пор,-пока на его входе удерживаются операнды (адрес), Затем формируются микрокоманды У. и УЗ, означающие режим записи в блоки памяти 8 и 9 по адресам А и А сформированные синфазно с А и А блоком памяти микропрограмм 12, приЧем высокий потенциал микрокоманд У и У обозначает (для блоков памяти 8 и 9) запись, низкий - считывание по соответствующим адресам(А , А,). После проведения цикла записи частичных произведений в блоки памяти 8 и 9 информация с входов 1 и 2 может быть снята, а блок микропрограммного управления сформирует NV циклов частичных сумм, каждый из которых заканчивается вычислением соответствующей цифры конечного произведения. (3) Вычисление частичных сумм производится с помощью табличного блока суммирования 7, на адресный вход которого подается микрокоманда , по соответствуюищм адресам.Адресам в этом случае как и в предыдущем я ляются коды слагаемых, подаваемых из блоков памяти 8 и 9, через муль типлексоры 3 и 4. Формирование частичных сумм (Z и конечных цифр произведения (П-)п изводится согласно следую1цим выраж ниям (применительно к разбиению on рандов на группы согласно фиг.4), 1 цикл П П1 J - Ч 2, п; 2 цикл П2 n;+.Z, ,, где П«..- перенос при образовании с ответствующей частичной с мы; П..- перенос от формирования цифры соответствующего ко нечного знака произведени 3 цикл Ппг г П21 3 2 1::1ь п, -П Zv 4 цикл 1в 7 9 а + п Z..- . п Z Vo ПГ-П,(7) .п5:,, Zi3 Iiz+ nl .-,3

/dS

Ai Аг Аз А У/ /г Уз /s j/j

1 1 1 ff tttttt

fO Н Jl3 5 цикл 12:11 |i5 + 1t + 1i7 + П П4 Г П -П + П ,, Г I п1 6 дикп 121 П 1,.-)- 421 Пп5 Г,, nV Однако при выполнении алгоритма умг ожения исходные данные для образования i-й частичной суммы могут быть расположены в одном и том же блоке памяти, Тогда при записи в регистр 5 их необходимо разнести по группам. Для этого используются перекрестные связи мультиплексоров 3 и 4, т.е. производится склеивание слагаемых, расположенных в одном и том же блоке памяти. Зафиксированные на регистре 5 слагаемые через блок 7 идентифицируются в .сумму, значение которой поступает на информационные входы блоков памяти 8 и 9, и при выработке блоком микропрограммного управления -микрокоманды У пары цифр конечHbqc произведений выводятся из устройства. 6ь/хоЗ г и 12 /Japajfffe/JMd/u ootxoo w/fa 1 дь/xoff памяти Muffponpoграмм 12 азс вмжоЗо. MUffpOffO/ O/fff УгУгУбУ7 aja MUffpoifОмане

ytygyey

Фиг. I

Фиг.Ъ

JW . (/

| Соловьев Г.Н.Арифметические устройства ЭВМ | |||

| М.: Радио, с.129, рис.5.2 | |||

| Потапов В.И | |||

| и др | |||

| Быстродейст- вующие АПУ ЦВМ (учебное пособие ) | |||

| Новосибирск, 1978, с.9-15,рис.1.3.2 |

Авторы

Даты

1985-08-30—Публикация

1984-03-30—Подача