Изобретение относится к цифровой вычислительной технике и может быть использовано в ЭВМ и цифровых системах с повьшенной достоверностью.

Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей с различной очередностью поступления .

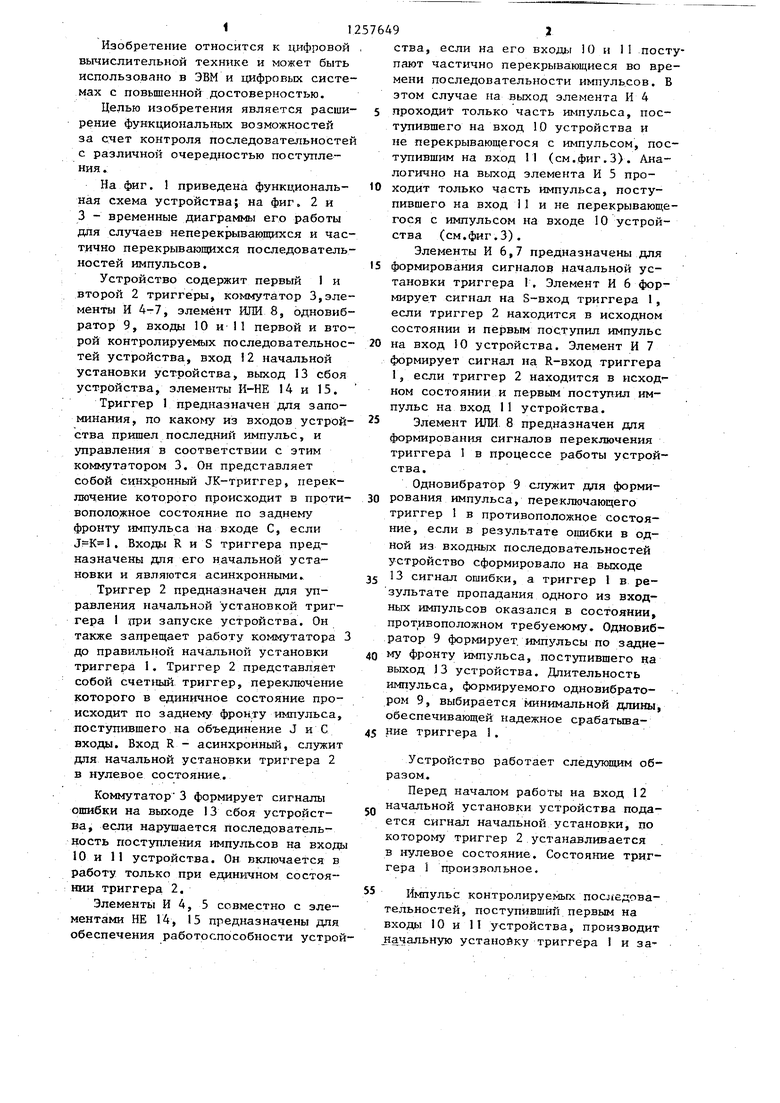

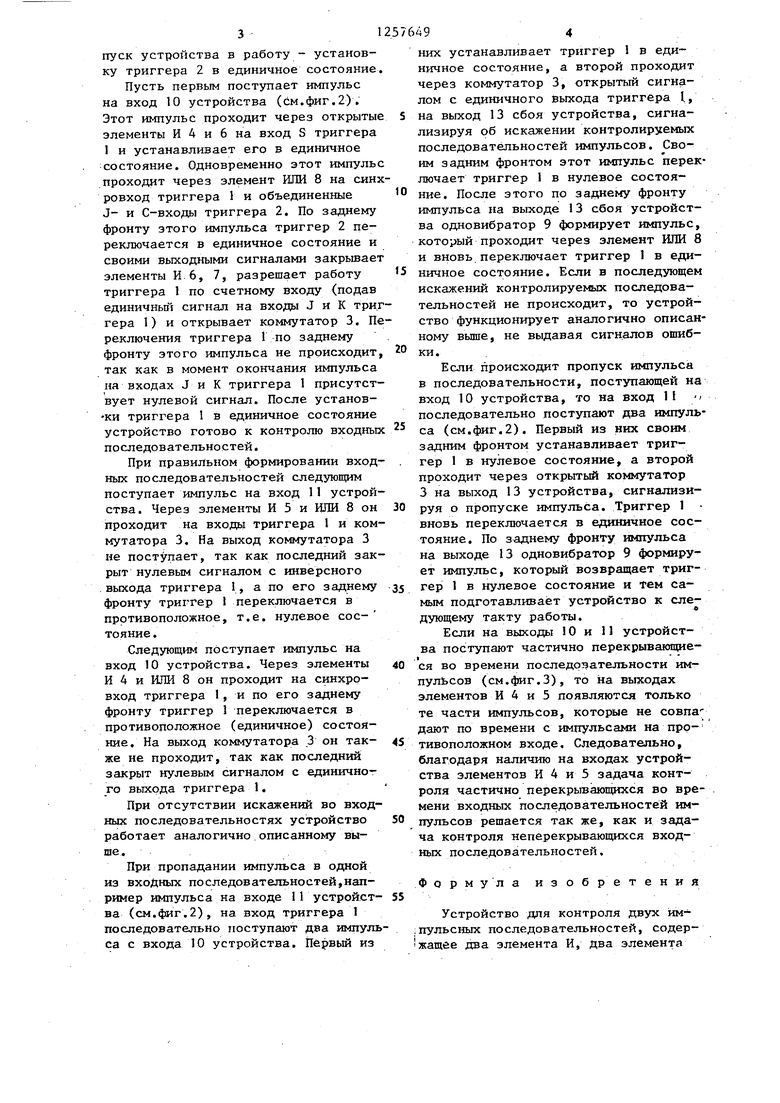

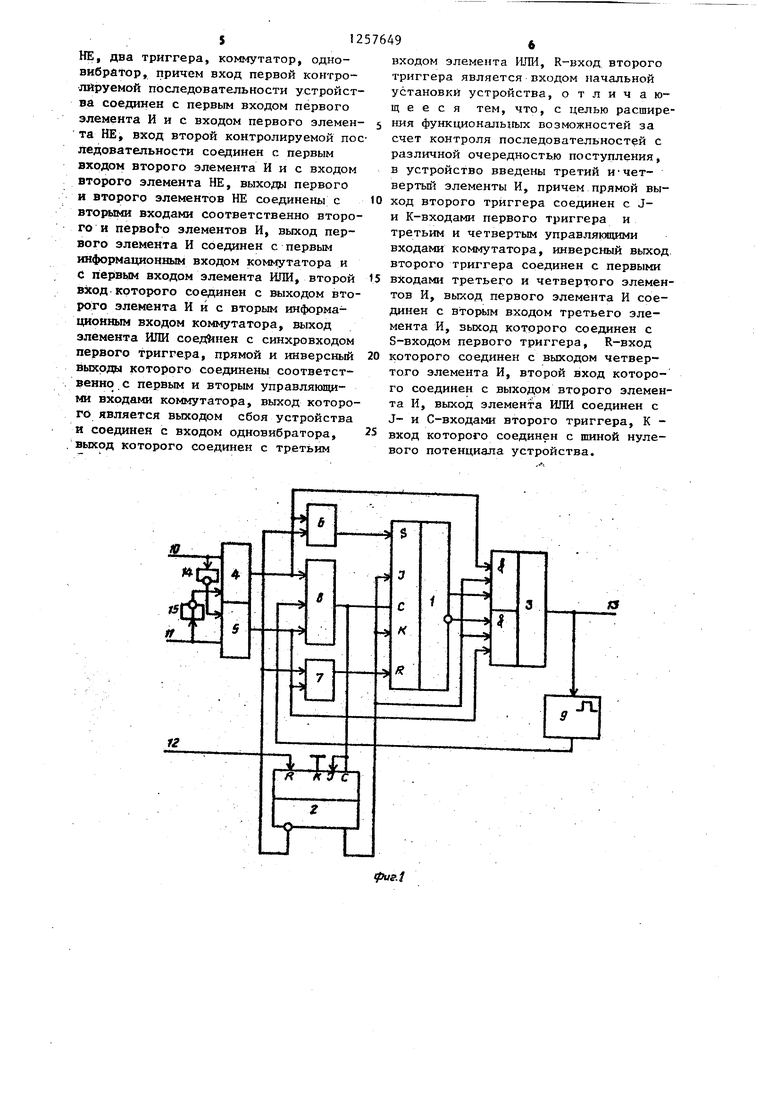

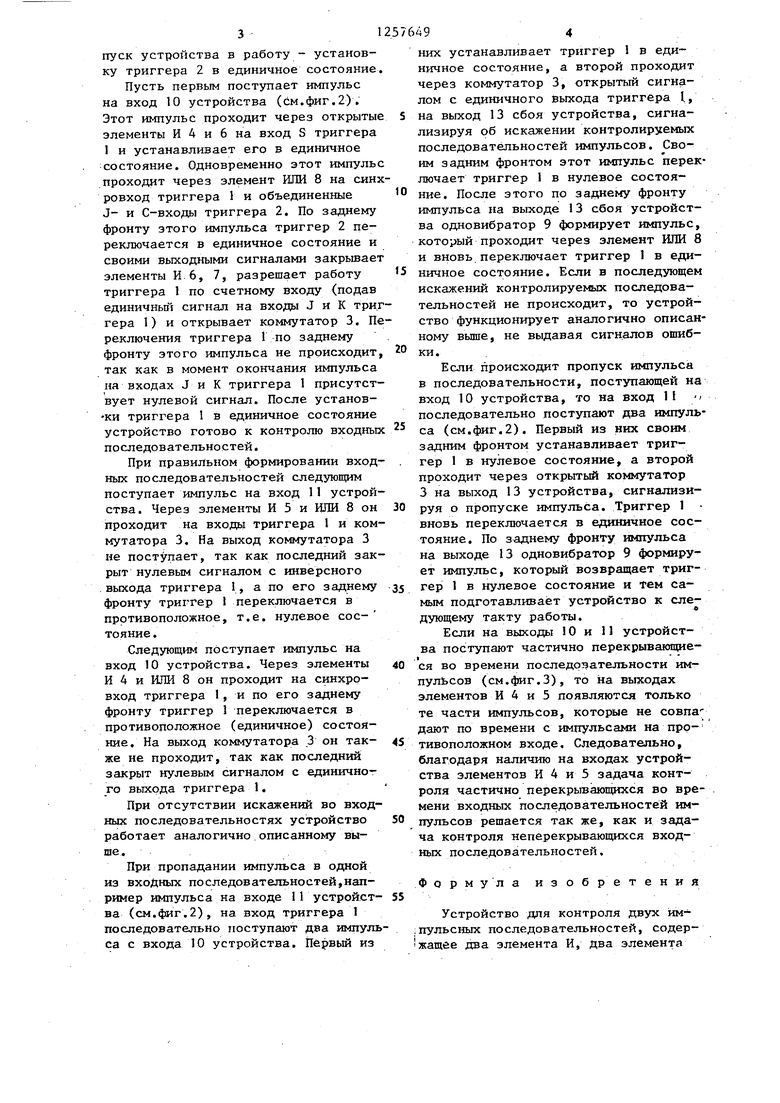

На фиг. 1 приведена функциональная схема устройства; на фиг, 2 и 3 - временные диаграммы его работы для случаев неперекрывающихся и частично перекрывающихся последовательностей импульсов.

Устройство содержит первый 1 и второй 2 триггеры, коммутатор 3,элементы И 4-7, элемент ИЛИ 8, одновиб- ратор 9, входы 10 и 11 первой и второй контролируе1« 1х последовательностей устройства, вход 12 начальной установки устройства, выход 13 сбоя устройства, элементы И-НЕ 14 и 15.

Триггер 1 предназначен для запоминания, по какому из входов устройства пришел последний импульс, и управления в соответствии с этим коммутатором 3. Он представляет собой синхронный JK-триггер, переключение которого происходит в противоположное состояние по заднему фронту импульса на входе С, если . Входы R и S триггера предназначены для его начальной установки и являются асинхронными.

Триггер 2 предна;значен для управления начальной установкой триггера 1 цри запуске устройства. Он также запрещает работу коммутатора 3 до правильной начальной установки триггера 1. Триггер 2 представляет собой счет1Ш1й триггер, переключение которого в единичное состояние происходит по заднему фрон.ту импульса, поступившего на объединение J и С входы. Вход R - асинхронный, служит для начальной установки триггера 2 в нулевое состояние.

Коммутатор 3 формирует сигналы ошибки на выходе 13 сбоя устройства, если нарушается последовательность поступления импульсов на входы 10 и 11 устройства. Он включается в работу только при единичном состоянии триггера 2.

Элементы И 4, 5 совместно с элементами НЕ 14, 15 предназначены для обеспечения работоспособности устройства, если на его входы 10 и 11 поступают частично перекрывающиеся во времени последовательности импульсов. В этом случае на выход элемента И 4

проходит только часть импульса, поступившего на вход 10 устройства и не перекрывающегося с импульсом, поступившим на вход 11 (см.фиг.3). Аналогично на выход элемента И 5 проходит только часть импульса, поступившего на вход 11 и не перекрывающегося с импульсом на входе 10 устройства (см.фиг.3).

Элементы И 6,7 предназначены для

формирования сигналов начальной установки триггера 1. Элемент И 6 фор мирует сигнал на S-вход триггера 1, если триггер 2 находится в исходном состоянии и первым поступил импульс

на вход 10 устройства. Элемент И 7 формирует сигнал на R-вход триггера 1, если триггер 2 находится в исходном состоянии и первым поступил импульс на вход I1 устройства.

Элемент ИЛИ 8 предназначен дпя формирования сигналов переключения триггера 1 в процессе работы устройства.

Одновибратор 9 сггужит для формирования импульса, переключающего триггер 1 в противоположное состояние, если в результате оишбки в одной из входных последовательностей устройство сформировало на выходе

13 сигнал ошибки, а триггер 1 в результате пропадания одного из входных импульсов оказался в состоянии, противоположном требуемому. Одновибратор 9 формирует, импульсы по задне фронту импульса, поступившего на выход 13 устройства. Длительность импульса, формируемого одновибрато- ром 9, выбирается минимальной длины, обеспечивающей надежное срабатьшание триггера 1.

Устройство работает следующим образом.

Перед началом работы на вход 12

начальной установки устройства подается сигнал начальной установки, по которому триггер 2 устанавливается в нулевое состояние. Состояние триггера i произвольное.

55 Импульс контролируемых: последовательностей, поступивший первым на входы 10 и И устройства, производит jHa4anbHyTo установку триггера I и за

пуск устройства в работу - установку триггера 2 в единичное состояние

Пусть первым поступает импульс на вход 10 устройства (см.фиг.2), Этот импульс проходит через открыты элементы И 4 и 6 на вход S триггера 1 и устанавливает его в единичное ;состояние. Одновременно этот импуль проходит через элемент ИЛИ 8 на син ровход триггера 1 и объединенные J- и С-входы триггера 2. По заднему фронту этого импульса триггер 2 переключается в единичное состояние и своими выходными сигналами закрьшае элементы И 6, 7, разрешает работу триггера 1 по счетному входу {подав единичньй сигнал на входы J и К тригера 1) и открывает коммутатор 3. Преключения триггера 1 по заднему фронту этого импульса не происходит так как в момент окончания импульса на входах J и К триггера 1 присутствует нулевой сигнал. После установ- ки триггера 1 в единичное состояние устройство готово к контролю входных последовательностей.

При правильном формировании входных последовательностей следующим поступает импульс на вход 11 устройства. Через элементы И 5 и ИЛИ 8 он проходит на входы триггера 1 и коммутатора 3. На выход коммутатора 3 не поступает, так как последний закрыт нулевым сигналом с инверсного выхода триггера 1, а по его заднему фронту триггер 1 переключается в противоположное, т.е. нулевое сое- тояние.

Следующим поступает импульс на вход 10 устройства. Через элементы И 4 и ИЛИ 8 он проходит на синхро- вход триггера 1, и по его заднему фронту триггер 1 переключается в противоположное (единичное) состояние. На выход коммутатора 3 он также не проходит, так как последний закрыт нулевым сигналом с единичного выхода триггера 1.

При отсутствии искажений во входных последовательностях устройство работает аналогично описанному выше.

При пропадании импульса в одной из входных последовательностей,например импульса на входе 11 устройст- ва (см.фиг.2), на вход триггера 1 последовательно поступают два импульса с входа 10 устройства. Первый из

15

го

25

55

10

2576А94

них устанавливает триггер 1 в единичное состояние, а второй проходит через коммутатор 3, открытый сигналом с единичного выхода триггера I, на выход 13 сбоя устройства, сигнализируя об искажении контролируемых последовательностей импульсов. Своим задним фронтом этот импульс переключает триггер 1 в нулевое состоя ние. После этого по заднему фронту импульса на выходе 13 сбоя устройства одновибратор 9 формирует импульс, который проходит через элемент ИЛИ 8 и вновь переключает триггер 1 в единичное состояние. Если в последующем искажений контролируемых последовательностей не происходит, то устройство функционирует аналогично описанному выше, не выдавая сигналов ошибки.

Если происходит пропуск импульса в последовательности, поступающей на вход 10 устройства, то на вход П ч последовательно поступают два импульса (см.фиг.2). Первый из них своим задним фронтом устанавливает триггер 1 в нулевое состояние, а второй проходит через открытый коммутатор 3 на выход 13 устройства, сигнализируя о пропуске импульса. Триггер 1 вновь переключается в единичное состояние. По заднему фронту импульса на выходе 13 одновибратор 9 формирует импульс, который возвращает триггер 1 в нулевое состояние и тем самым подготавливает устройство к следующему такту работы.

Если на выходы 10 и П устройства поступают частично перекрывакшще- I

ся во времени последовательности им-

пульсов (см.фиг.3), то на выходах элементов И 4 и 5 появляются только те части импульсов, которые не совпа дают по времени с импульсами на противоположном входе. Следовательно, благодаря наличию на входах устройства элементов И 4 и 5 задача контроля частично перекрьшающихся во времени входных последовательностей импульсов решается так же, как и задача контроля неперекрывающихся входных последовательностей.

30

35

40

45

50

Формула изобретения

Устройство для контроля двух йм- :пульсных последовательностей, содер- жащее два элемента И, два элемента

НЕ, два триггера, коммутатор, одно- вибрйтор, причем вход первой контролируемой последовательности устройства соединен с первым входом первого элемента И и с входом первого элемента НЕ, вход второй контролируемой последовательности соединен с первым входом второго элемента И и с входом второго элемента НЕ, выходы первого и второго элементов НЕ соединены с вторыми входами соответственно второго и nepBoho элементов И, выход первого элемента И соединен с первым информациомньш входом коммутатора и С первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с вторым информационным входом коммутатора, выход элемента ИЛИ с синхровходом первого триггера, прямой и инверсный выходы которого соединены соответственно с первым и вторым управляющими входами коммутатора, выход которого является выходом сбоя устройства и соединен с входом одновибратора, .выход которого соединен с третьим

to

12576496

входом элемента ИЛИ, R-вход второго триггера является входом начальной установки устройства, отличающееся тем, что, с целью расширения функ1щоналы1ьгх возможностей за счет контроля последовательностей с различной очередностью поступления, в устройство введены третий И чет- вертьй элементы И, причем прямой выход второго триггера соединен с J- и К-входами первого триггера и третьим и четвертым управлякяцими входами коммутатора, инверсный выход второго триггера соединен с первыми 15 входами третьего и четвертого элементов И, выход первого элемента И соединен с вторым входом третьего элемента И, выход которого соединен с S-входом первого триггера, R-вход 20 которого соединен с выходом четвертого элемента И, второй вход которого соединен с выходом второго элемента И, выход элемента ИЛИ соединен с J- и С-входами второго триггера, К - 25 вход которого соединен с шиной нулевого потенциала устройства.

jpeдиктор И Рыбченко

Составитель Е.Торопов Техред Л.Сердюкова

Заказ 4958/48Тираж 671Подписное

ВНИИПИГосударствейного комитета СССР по делам изобретений и открытий 113035 Москва, Ж-35, Раушская наб.,д,4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Черни

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1298721A1 |

| Устройство для контроля двух импульсных последовательностей | 1984 |

|

SU1223232A1 |

| Устройство для контроля генераторов импульсов | 1984 |

|

SU1261097A1 |

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1986 |

|

SU1322288A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1636846A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в ЭВМ и цифровых системах с повышенной дос- . товерностью. Отличительной особенностью устройства является то, что оно может использоваться для контроля пар последовательностей нмпуль- сов, для которых заранее неизвестно, на какой из входов импульс поступит первым, либо в тех случаях, когда требуется Подключение устройства для контроля в произвольный, заранее неизвестный момент времени. Это существенно расширяет область применения устройства. Целью изобретения является расширение функциональных возможностей за счет контроля последовательностей с различной очередностью поступления. Поставленная цель достигается введением третьего и четвертого злементов И, 3 ил. (Л с: ю ел SI О 4 ;о

| Устройство для контроля импульсов | 1982 |

|

SU1045373A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля двух импульсных последовательностей | 1984 |

|

SU1223232A1 |

Авторы

Даты

1986-09-15—Публикация

1984-08-13—Подача