Изобретение относится к области автоматики и цифровой техники и предназначе- но для проверки сложных блоков синхронизации, контроллеров, датчиков информации, используемых в автоматизированных системах управления, обработки информации, связи.

Цель изобретения - расширение области применения устройства путем обеспече- ния возможности агрегатирования устройств при увеличении числа контролируемых последовательностей и повышение достоверности контроля,

Сущность изобретения состоит в обеспечении возможности наращивания числа входов контролируемых последовательностей путем соединения однотипных агре- гатированных устройств контроля последовательностей импульсов без введения схемных изменений внутри устройства

и без использования дополнительных элементов, а также повышении достоверности контроля за счет обеспечения обнаружения и фиксации номера входа, по которому поступил ложный сигнал.

Введение в устройство приоритетного шифратора и его связей обеспечивает определение номера входа, по которому поступил ложный сигнал.

Введение второго одновибратора, буферного элемента и их связей позволяет сформировать импульс записи номера входа, по которому поступил ложный импульс в регистр, а также импульс на сигнальном выходе устройства.

Введение регистра и его связей позволяет зафиксировать номер входа, по которому поступил ложный сигнал, и выдать его на информационный выход устройства.

XI

ND СЛ СО

XI

со

В ведение третьего, четвертого и пятого элементов ИЛИ и их связей обеспечивают агрегатирование устройств с целью наращивания числа входов контролируемых последовательностей без введения схемных изменений внутри устройства и без изменения внешних дополнительных элементов.

Введение группы одновибраторов позволяет обеспечить надежную запись номера канала, по которому поступил ложный сигнал независимо от его длительности.

Введение триггера м его связей позволяет четко выделить интервал контроля последовательности.

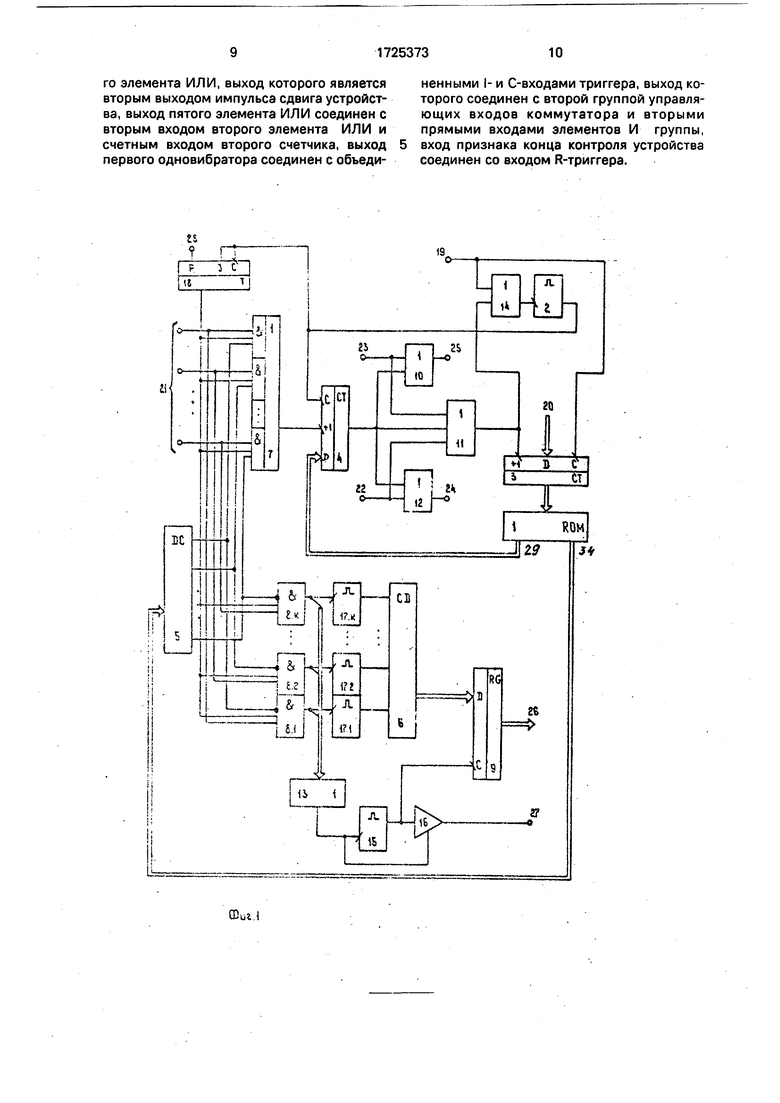

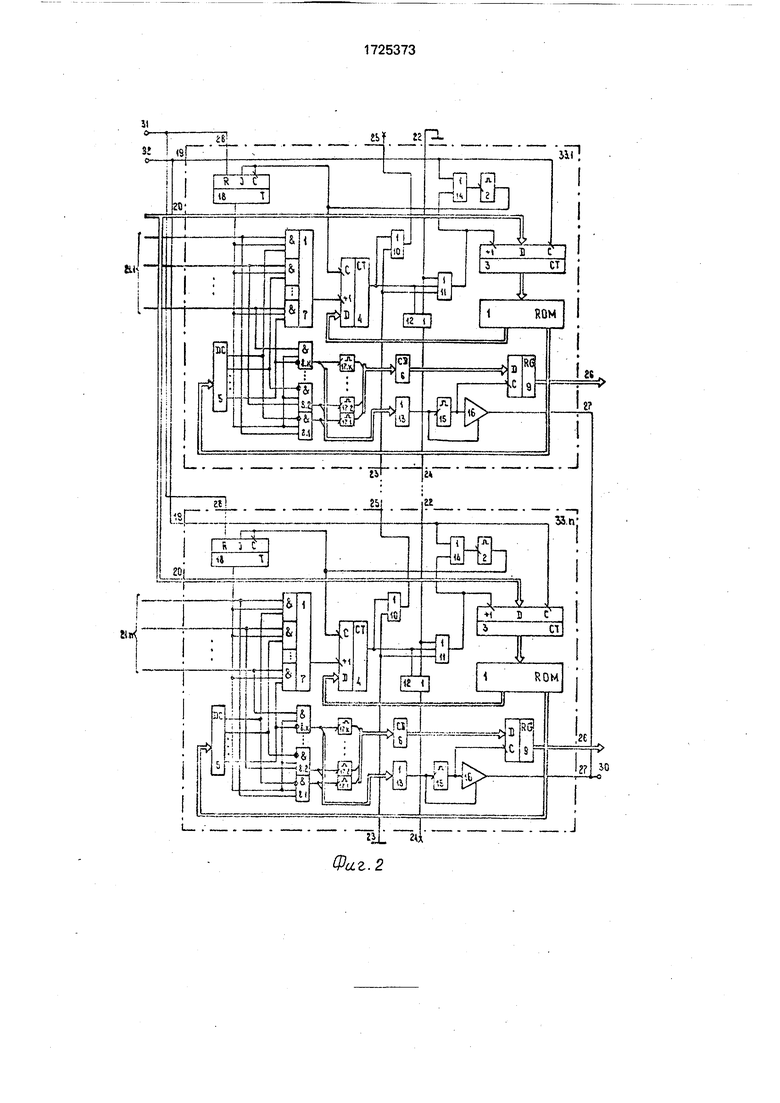

На фиг.1 приведена функциональная схема устройства: на фиг.2 - функциональная схема устройства контроля n x К последовательностей, реализованного объединением n предлагаемых устройств для контроля К-входовых последователь- ностей; на фиг.З - пример размещения ин- формации для контро ля одной последовательности в блоках памяти устройств-модулей (при ).

Устройство для контроля последова- тельностей импульсов (фиг.1) содержит блок 1 памяти, первый одновибратор 2, первый 3 и второй 4 счетчики, дешифратор 5, шифратор 6, коммутатор 7, группу элементов И 8, регистр 9, третий 10, пятый 11, четвертый 12, первый 13 и второй 14 элементы ИЛИ, второй одновибратор 15, буферный элемент 16, группу одновибраторов 17.1 - 17.п, триггер 18, вход 19 синхронизации устройства, вход 20 кода номера последовательности устройства.

Одновибратор 2 формирует на своем выходе импульс, длительность которого превышает время переходных процессов в счетчике 3 и блоке 1 памяти, Он запускается по заднему фронту импульса, сформированного на выходе элемента ИЛИ 14.

Счетчик 3 служит для записи, хранения, модификации и выдачи адреса для блока 1 памяти. Запись начального адреса контро- лируемой последовательности, поступающего на D-вход счетчика 3 с входа 20 устройства, осуществляется по заднему фронту синхроимпульса, поступающего на вход синхронизации счетчика 3 с входа 19 устройства. Модификация адреса осуществляется путем увеличения предыдущего адреса на единицу по заднему фронту импульса, поступающего с выхода элемента ИЛИ 11 на счетный вход счетчика 3.

Счетчик 4 предназначен для подсчета числа импульсов в i-м пакете контролируе- мой последовательности. Код (N-v)(rfle N- число переполнения), поступающий на D-вход счетчика 4 с второго выхода 29 блока

1 памяти, записывается по заднему фронту импульса, поступающего на его синхровход с выхода одновибратора 2. При поступлении импульса с выхода коммутатора 7 на счетный вход счетчика 4 он увеличивает свое состояние на единицу.

Дешифратор 5 в соответствии с кодом, поступившим с первого выхода 34 ПЗУ 1, формирует управляющие сигналы на входы коммутатора 7 и группы элементов И 8, что позволяет различать импульсы, принадлежащие и не принадлежащие контролируемой последовательности.

Приоритетный шифратор 6 предназначен для формирования кода номера ложного сигнала,-поступившего на входы 21 устройства. При одновременном поступлении двух или более сигналов на его входы (что маловероятно) он формирует код номера сигнала, которому установлен наибольший приоритет.

Коммутатор 7 служит для формирования импульса на счетный вход счетчика 4, если поступивший на вход 21 устройства импульс соответствует контролируемой последовательности пакетов импульсов.

Группа элементов И 8 предназначена для выделения ложных импульсов, поступающих на входы 21 контролируемых последовательностей. Все элементы И 8 группы, которые соответствуют запрещенным в данном цикле импульсам, открыты нулевыми сигналами с выхода дешифратора 5, поэтому любой ложный импульс, поступивший на входы 21, пройдет на выходы элементов И 8.

Регистр 9 предназначен для записи, хранения и выдачи на выход 26 устройства кода номера входа, по которому поступил ложный сигнал. Запись информации в регистр 9 осуществляется по заднему фронту импульса с выхода одновибратора 15.

Элемент ИЛИ 10 формирует импульс на первом выходе 25 импульса сдвига устройства, если он сформирован внутри устройства, либо поступил на его вход 23.

Элемент ИЛИ 11 формирует сигнал на счетный вход счетчика 3 и элемент ИЛИ 14 при переходе к контролю очередного пакета импульсов по одному из входов 21.

Элемент ИЛИ 12 формирует импульс на втором выходе 24 импульса сдвига устройства, если он сформирован внутри устройства либо поступил на его вход 22.

Элемент ИЛИ 13 формирует сигнал при поступлении любого ложного сигнала на один или несколько входов 21.

Элемент ИЛИ 14 формирует импульс запуска одновибратора 2, если в счетчик 3 поступил новый адрес.

Одновибратор 15 формирует короткий импульс, который через буферный элемент 16 поступает на сигнальный выход устройства, а также записывает код номера входа, по которому поступил ложный сигнал в ре- гистр 9. Длительность импульса, формируемого одновибратором 15, превышает время переходных процессов в приоритетном шифраторе 6, но меньше длительности сигнала на выходе шифратора 6.

Буферный элемент 16 обеспечивает пропуск сигнала на выход 27 устройства.

Группа одновибраторов 17.1-17. К предназначена для формирования сигналов заданной длительности, которая обес- печивает надежную запись информации в регистр 9. Запускаются одновибраторы 17.1-17. К передними фронтами импульсов, поступающих с выходов элементов И 8.1- S.K соответственно.

Триггер 18 обеспечивает четкое выделение интервала контроля последовательности импульсов. Он переключается в единицу по заднему фронту импульса, поступающего на его объединенные I- и С-входы. Уста- новка триггера 18 в нуль осуществляется единичным сигналом, поступающим на вход R.

Устройство работает следующим образом.

Для построения устройства, обеспечивающего контроль последовательностей, поступающих на m К входов, группа устройств объединяется так, как это показано на фиг.2. При этом число п объединяемых устройств, которые в дальнейшем будем называть модулями 33.1 -ЗЗ.п, выбирается из условия h-К т.

Перед началом функционирования элементы памяти всех модулей устанавливают- ся в исходное состояние. Цепи начальной установки на фиг.1 и 2 условно не показаны.

В счетчике3 модулей33.1 -ЗЗ.п е входа (фиг.2) записывается начальный адрес контролируемой последовательности по синхро- импульсу, поступившему на вход 32 и далее на входы 19 всех модулей.

Из счетчиков 3 начальный адрес поступает на входы блоков 1 памяти каждого модуля и на их выходах появляются записанные в ячейках коды. Если первый пакет импульсов должен поступить на один из входов, подключенных к i-му модулю, например j-й вход i-й группы входов, то на первом выходе блока 1 памяти модуля 33.i появится код номера этого входа, который поступит на вход дешифратора 5 этого модуля, а с второго выхода блока 1 этого модуля будет считан код N- v, который поступит

на вход D счетчика 4. В остальных модулях 33.р(р 1,п, (р по поступившему адресу из блоков 1 памяти будут считаны нулевые коды.

Одновременно с записью адреса в счетчик 3 синхроимпульс с входа 32 пройдет через элементы ИЛИ 14 модулей 33.1 -ЗЗ.п и запустит своим задним фронтом одновибраторы 2. Одновибраторы 2 сформируют импульсы, длительность которых превышает максимальное время переходных процессов в последовательно соединенных счетчике 3 и блоке 1 памяти. В результате этого после того, как на входе счетчика 4 модуля 33.i появится код числа N- V, по заднему фронту импульса с выхода одновибратора 2 он запишется в счетчик I модуля 33.i. В остальных модулях счетчики останутся в нуле. Одновременно переключается в единицу триггер 18 модулей 33.1-33.п и откроет коммутаторы 7 и элементы И-8 своих модулей.

В соответствии с кодом, поступившим на вход дешифратора 5 модуля 33.i , он сформирует единичный сигнал на i-м выходе и нулевые - на остальных выходах. В результате i-й выходной сигнал дешифратора 5 откроет i-й информационный вход коммутатора 7 модуля 33.i и закроет элемент И 8.L В остальных модулях на входы дешифраторов 5 поступят нулевые коды, поэтому коммутаторы 7 этих модулей будут закрыты, а элементы-И 8.1 - 8.К открыты. При правильной реализации контролируемой последовательности на j-й .информационный вход группы входов 21 будет поступать пакет импульсов. Импульсы будут проходить через коммутатор 7 на счетный вход счетчика 4 модуля 33.i, увеличивая каждый раз его состояние на единицу. При поступлении последнего -го импульса пакета на выходе счетчика 4 сформируется импульс переполнения/который пройдет через элемент ИЛИ 11 на счетный вход счетчика 3 и увеличит его состояние на единицу, а также запустит одновибрато.р 2 модуля 33.i. Одновременно импульс переполнения через элемент ИЛИ 10 пройдет на выход 25 модуля 33.i и в результате этого поступит во все модули 33.i 33.1-1, а через элемент ИЛИ 12 пройдет на выход 24 и поступит в модули 33.1+1 - ЗЗ.п.

Таким образом, по импульсу переполнения, сформированному счетчиком 4 модуля 33.i, увеличат свое состояние на единицу все счетчики 3 модулей 33.1 - ЗЗ.п. Считанные по новому адресу, коды с выходов блоков памяти 1 поступят на входы дешифраторов 5 и счетчиков 4 своих модулей и по импульсам, сформированным одно- вибраторами 2, запишутся в счетчики 4, В

результате устройство перейдет к контролю поступления очередного пакета импульсов. В дальнейшем устройство будет функционировать аналогично описанному выше.

По окончании контролируемой прследо- вательности с выходов блоков 1 памяти всех модулей 33.1 - 33.п будут считаны нулевые коды, В результате на всех выходах дешифраторов 5 (кроме нулевых, которые не используются) будут присутствовать нулевые сигналы и коммутаторы 7 всех модулей будут закрыты, а все элементы И 8 будут открыты. Поэтому любой импульс, поступивший на выход 21 модулей 33.1 -ЗЗ.п, сформирует сигнал ошибки на выходе 30 устройства. По окончании интервала контроля на вход 31 устройства поступит импульс, который пройдет на вход 28 всех модулей и сбросит триггеры 18 в нуль. Устройство прекратит функционирование до момента начала контроля очередной последовательности.

Рассмотрим более подробно процесс формирования сигнала ошибки и кода номера канала, по которому он поступил.

Если контролируемая последовательность будет искажена в любой момент интервала контроля, то очередной импульс поступит на один из входов 21 модулей 33.1-33.п. Так как этот импульс не принад- лежит контролируемой последовательности, то он пройдет через один из элементов И 8 (например, элемента И 8,т модуля 33.1) и своим передним фронтом запустит одно- вибратор 17.m и одновибратор 15 модуля 33. В результате этого на выходе шифратора 6 появится код номера входа, по которому поступил ложный импульс, который по заднему фронту импульса с выхода одновиб- ратора 15 запишется в реристр 9 модуля 33.1. Одновременно импульс с выхода одно- вибратора 15 откроет буферный элемент 16 и пройдет через него на выход 30 устройства, сигнализируя об ошибке.

Код номера входа, по которому посту- пил ложный импульс, будет выдан на выходе 26 модуля 33.1.

Если в дальнейшем на входы этого же модуля поступит еще один ложный импульс, то номер выхода вновь запишется в регистр 9, а на выход 27 модуля и далее на выход 30 устройства поступит сигнал ошибки.

Если на входы одного из модулей 33.1 - ЗЗ.п одновременно поступят несколько ложных импульсов, то шифратор 6 выделит код номера входа, которому присвоен наибольший приоритет (среди поступивших ложных импульсов) и его номер запишется в регистр 9 и поступит на выход 26.

Формул а изобретения Устройство для контроля последовательностей импульсов, содержащее блок памяти, первый и второй счетчики, дешифратор, коммутатор, группу элементов И, первый и второй элементы ИЛИ, первый одновибратор, причем входы контролируемой последовательности устройства соединены с группой информационных входов коммутатора и первыми прямыми входами элементов И группы, первый выход блока памяти соединен с входом дешифратора, выходы которого соединены с первой группой управляющих входов коммутатора и инверсными входами элементов И, группы выходов которых соединены с входом первого элемента ИЛИ, выход коммутатора соединен со счетным входом первого счетчика, второй выход блока памяти соединен с информационным входом первого счетчика, вход синхронизации устройства соединен с первым входом второго элемента ИЛИ и входом синхронизации второго счетчика, выход которого соединен с адресным входом блока памяти, выход второго элемента ИЛИ соединен через первый одновибратор с синхровходом первого счетчика, вход кода номера последовательностей устройства соединен с информационным входом второго счетчика, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения возможности агрегатирования устройств при увеличении числа контролируемых последовательностей и повышения достоверности контроля, в него дополнительно введены шифратор, регистр, второй одно- вибратор, третий, четвертый и пятый элементы ИЛИ, группа одновибраторов, триггер, причем выходы элементов И группы соединены с входами одновибраторов группы, выходы которых соединены с входами приоритетного шифратора, выход которого соединен с информационным входом регистра,.выход первого элемента ИЛИ соединен через второй одновибратор с синхровходом регистра и является выходом ошибки устройства, выход регистра является выходом кода номера входа ложного сигнала устройства, выход переполнения первого счетчика соединен с первыми входами третьего, четвертого и пятого элементов ИЛИ, первый выход импульса сдвига устройства соединен с вторым входом пятого элемента ИЛИ и вторым входом третьего элемента ИЛИ, выход которого является первым выходом импульса сдвига устройства, второй вход импульса сдвига устройства соединен с третьим входом пятого лемента ИЛИ и с вторым входом четвертого элемента ИЛИ, выход которого является вторым выходом импульса сдвига устройства, выход пятого элемента ИЛИ соединен с вторым входом второго элемента ИЛИ и

ненными I- и С-входами триггера, выход которого соединен с второй группой управляющих входов коммутатора и вторыми прямыми входами элементов И группы,

счетным входом второго счетчика, выход 5 вход признака конца контроля устройства первого одновибратора соединен с объеди- соединен со входом R-триггера.

ненными I- и С-входами триггера, выход которого соединен с второй группой управляющих входов коммутатора и вторыми прямыми входами элементов И группы,

U.I

ТАЛ

«.S

Л.

Si-S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для контроля хода программы | 1988 |

|

SU1663612A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1667080A1 |

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| МУЛЬТИМИКРОКОНТРОЛЛЕРНАЯ СИСТЕМА | 1997 |

|

RU2120135C1 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчиков информации, используемых в автоматизированных системах управления, обработки информации, связи. Цель изобретения - расширение области применения устройства путем обеспе- чения возможности агрегатирования устройств при увеличении числа контролируемых последовательностей и повышения достоверности контроля. Цель достигается введением в устройство шифратора, регистра, второго одновибратора, буферного элемента, третьего, четвертого и,пятого элементов ИЛИ, группы одновибраторов, триггера и их связей. Достоверность достигается за счет обеспечения обнаружения и фиксации номера входа, по которому поступил ложный сигнал. 3 ил. (/ С

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1501064A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1619277A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1992-04-07—Публикация

1990-06-04—Подача