Изобретение относится к вычислительной технике и может быть исполь- эовано в отказоустойчивых многопроцессорных системах для распределения задач между процессорами.

Целью изобретения является повышение производительности за счет определения ютказавшего процессора одновременно с повторным решением за дачи.

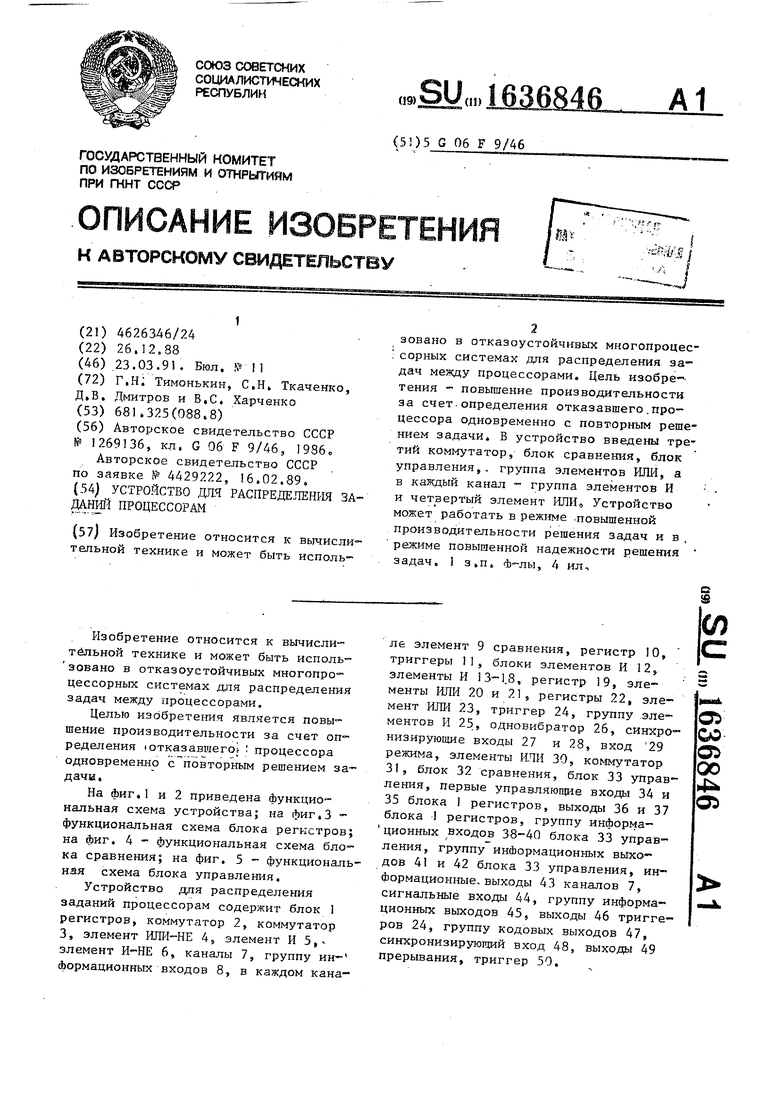

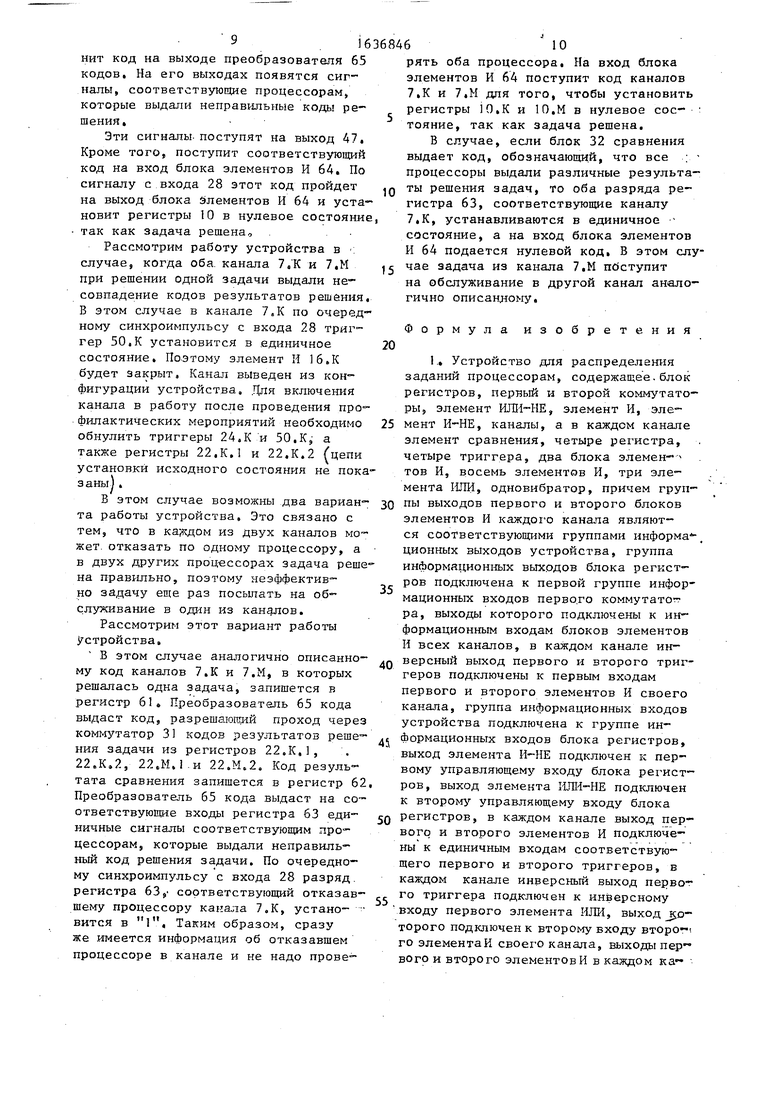

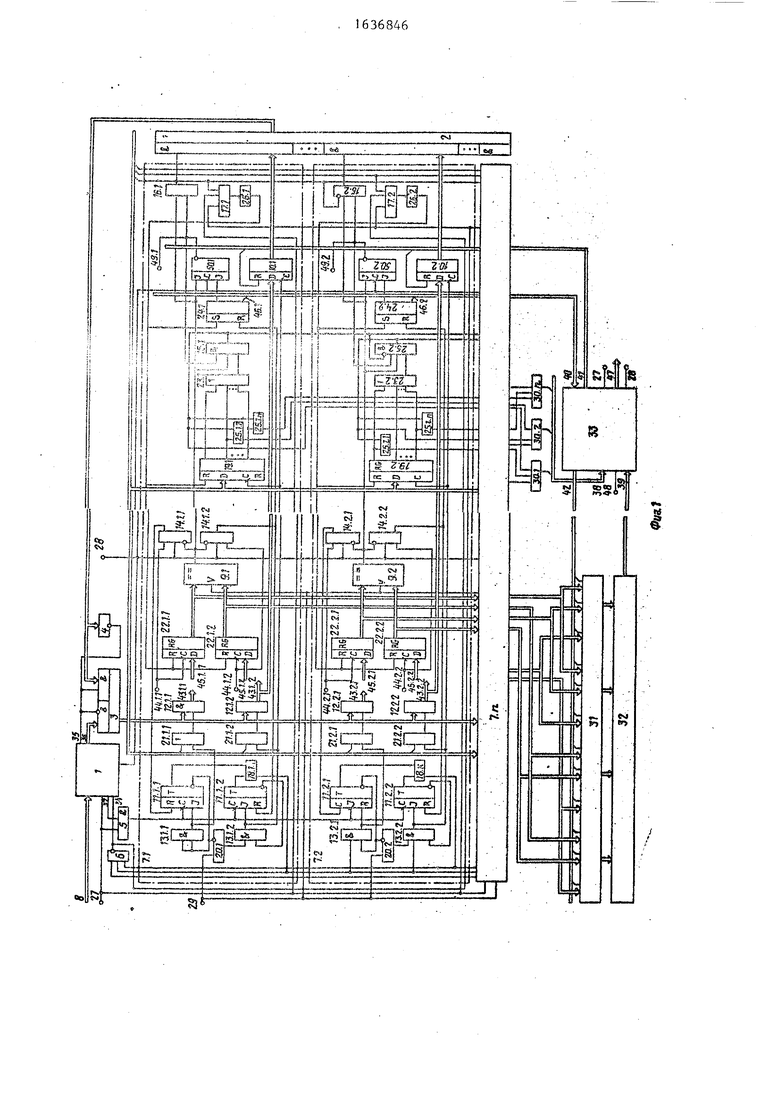

На фиг.1 и 2 приведена функциональная схема устройства; на фиг.З - функциональная схема блока регистров; на Лиг. 4 - функциональная схема блока сравнения; на фиг. 5 - функциональная схема блока управления.

Устройство для распределения заданий процессорам содержит блок 1 регистров, коммутатор 2, коммутатор 3, элемент ИЛИ-НЕ 4S элемент И 5,-- элемент И-НЕ 6, каналы 7, группу ин-1 (Ьормационньгх входов 8, в каждом канале элемент 9 сравнения, регистр 10, триггеры 11, блоки элементов И 12, элементы И 13-1.8, регистр 19, элементы ИЛИ 20 и 21, регистры 22, элемент ИЛИ 23, триггер 24, группу элементов И 25, одновибратор 26, синхронизирующие входы 27 и 28, вход 29 режима, элементы ИЛИ 30, коммутатор 31, блок 32 сравнения, блок 33 управления, первые управляющие входы 34 и 35 блока 1 регистров, выходы 36 и 37 блока 1 регистров, группу информа- 1ционных входов 38-40 блока 33 управления, группу информационных выходов 41 и 42 блока 33 управления, информационные, выходы 43 каналов 7, сигнальные входы 44, группу информационных выходов 45, выходы 46 триггеров 24, группу кодовых выходов 47, синхронизирующий вход 48, выходы 49 прерывания, триггер 50.

(Л

сэ со оэ оо

4 О

Блок 1 регистров (Фиг.З) содержит каналы и в каждом регистр 51, блок 52 элементов ИЛИ, элементы ИЛИ 53 и 54, элемент И 55, триггер 56, элементы И 57 и 58, блок элементов И 59.

Блок 32 сравнения (Ьиг.4) содержит элементы 60 сравнения,

Блок 33 управления (фиг,5) содержи регистры 61-63, блок элементов И 64, преобразователь 65 кода.

Блок 33 управления (фиг, 5) пред« назначен для выдачи управляющих сигналов на входы коммутатора 31 и для

Триггер 50 в каждом канале предназначен для фиксации момента отказа соответствующего канала 7. Триггер 50 имеет два входа, связанные конъюнк- тивно. Установка его в единицу осуществляется по заднему фронту импульса на входе синхронизации, если на обоих входах присутствуют единичные сигналы Установка триггера 50 в единичное состояние осуществляется в случае повтор ного несравнения результатов решения;

управления сбросом регистров 10. Блок задачи в данном канале. В этом случае

33 управления содержит преобразователь 65 кода. Преобразователь кода преобразует код, поступающий с выходов регистров 61 и 62. В регистр 61 код записывается с выхода элементов ИЛИ 30 по переднему фронту импульса с входа 48, В соответствии с этим кодом преобразователь кода выдает управляющие сигналы на входы коммутатора 31.

триггер 24 уже установлен в единичное состояние и на выходе элемента 9 сравнения присутствует единичный сигнал, по заднему фронту импульса с 20 входа 28 триггер 50 устанавливается в единичное состояние. Установка триггера 50 в нулевое состояние осуществляется после проверки процессоров соответствующего канала 7 внеш-

триггер 24 уже установлен в единичное состояние и на выходе элемента 9 сравнения присутствует единичный сигнал, по заднему фронту импульса с 20 входа 28 триггер 50 устанавливается в единичное состояние. Установка триггера 50 в нулевое состояние осуществляется после проверки процессоров соответствующего канала 7 внеш-

В блоке 32 сравнения выполняется срав1 25 ним сигналом (цепи установки на фиг.1

некие кодов, результаты сравнения ПО ступают на вход регистра 62. В регистр 62 этот код записывается по заднему Фронту импульса с входа 48, Таким образом, длительность импуль - са на входе 48 должна быть больше дли-4 тельности переходных процессов при последовательном срабатывании коммутатора 31 и блока 32 Сравнения,В соот- ветствии с кодами, поступившими на входы, преобразователь 65 кода выдает другой код, который поступает на информационные входы регистра 63 и блока элементов И 64.

В устройстве через выходы 43 коды задач поступают для решения. Работа процессоров синхронизируется импульсами с входов 27 и 28 На входы 45 выдаются коды результатов решения задачи, причем код выставляется после прохождения заднего фронта импульса с входа 28, но до поступления пе- реднего фронта импульса на вход 48.- На входах 44 появляются сигналы после того, как соответствующий процессор решит задачу. Сигналы на этих выходах должны появляться после прохождения заднего фронта импульса с входа 28 и сниматься после прохождения заднего Фронта следующего импульса с этого же входа. Если хоть один из процессоров во время решения задачи дал сбой или отказ в режиме повышенной достоверности решения

30

35

40

не показаны).

Устройство работает следующим образом

В начальный момент все элементы памяти находятся в нулевом состоянии. Ёлок 1 регистров не содержит информации. На выходах элементов И-НЕ 6 и ИЛИ-НЕ 4 присутствуют единичные сигналы (цепи установки в исходное состояние не показаны).

Устройство может работать в режиме Т повышенной производительности решения задач и в режиме II повышенной надежности решения задач.

Рассмотрим работу устройства в режиме I. В этом режиме на входе 29 при сутствует нулевой сигнал. Он обеепе-- чивает поступление задачи для решения в один процессор. Задачи, пришедшие де на вход 8 устройства, поступают в бло

Iрегистров, откуда последовательно через коммутатор 3 поступают на информационные входы блоков элементов

И 12. Однако, код задачи пройдет только на выход 43, так как только на выходе элемента ИЛИ 21 присутствует единичный сигнал. После поступления за- дачи в процессор очередной синхроим- пульс с входа 27, пройдя через открытый элемент И 5, установит триггер

I1в единичное состояние. Нулевой сигнал с инверсного выхода этого триггера через ; элемент ИЛИ 20 откроет элемент И 13, поэтому вторая за50

55

16368464

задачи, то оба процессора переводя1 1-

ся в режим контроля.

Триггер 50 в каждом канале предназ начен для фиксации момента отказа соответствующего канала 7. Триггер 50 имеет два входа, связанные конъюнк- тивно. Установка его в единицу осуществляется по заднему фронту импульса на входе синхронизации, если на обоих входах присутствуют единичные сигналы Установка триггера 50 в единичное состояние осуществляется в случае повтор ного несравнения результатов решения;

задачи в данном канале. В этом случае

триггер 24 уже установлен в единичное состояние и на выходе элемента 9 сравнения присутствует единичный сигнал, по заднему фронту импульса с входа 28 триггер 50 устанавливается в единичное состояние. Установка триггера 50 в нулевое состояние осуществляется после проверки процессоров соответствующего канала 7 внеш-

ним сигналом (цепи установки на фиг.1

ним сигналом (цепи установки на фиг.1

не показаны).

Устройство работает следующим образом

В начальный момент все элементы памяти находятся в нулевом состоянии. Ёлок 1 регистров не содержит информации. На выходах элементов И-НЕ 6 и ИЛИ-НЕ 4 присутствуют единичные сигналы (цепи установки в исходное состояние не показаны).

Устройство может работать в режиме Т повышенной производительности решения задач и в режиме II повышенной надежности решения задач.

Рассмотрим работу устройства в режиме I. В этом режиме на входе 29 присутствует нулевой сигнал. Он обеепе-- чивает поступление задачи для решения в один процессор. Задачи, пришедшие на вход 8 устройства, поступают в блок

Iрегистров, откуда последовательно через коммутатор 3 поступают на информационные входы блоков элементов

И 12. Однако, код задачи пройдет только на выход 43, так как только на выходе элемента ИЛИ 21 присутствует единичный сигнал. После поступления за- дачи в процессор очередной синхроим- , пульс с входа 27, пройдя через открытый элемент И 5, установит триггер

I1в единичное состояние. Нулевой сигнал с инверсного выхода этого триггера через ; элемент ИЛИ 20 откроет элемент И 13, поэтому вторая за

дача с выхода коммутатора 3 поступит, через блок элементов И 12 во второй процессор. По очередному синхроимпульсу с входа 27 триггер 11 уста- новится в единичное состояние. После этого появится, единичный сигнал на выходе элемента И 18. Этот сигнал откроет элемент И 13 и на его выходе появится управляющий сигнал для приема очередной задачи в соответствующий процессор. Задача в процессор поступит аналогично описанному. После того, как все процессоры включатся в, работу, на выходе элемента И-НЕ 6 появится нулевой сигнал. Этот сигнал поступит в блок 1 регистров и последний перестанет выдавать задачи для распределения Если какой-нибудь процессор выполнил поступившую на его вход задачу, то на входе 44 появится единичный сигнал.

, Для нормальной работы устройства (необходимо, чтобы сигналы на входах J44 выставлялись в паузах между импульсами с входов 28 и 27 и снимались после прохождения импульса с входа 28 но до импульса с входа 27. Задачи на вход 8 устройства должны поступать в паузах между импульсами с входов 28 и 27 и сниматься после прохождения очередного импульса с входа 27, но до импульса с входа 28.

Так как на входе 29 действует ну- левой сигнал, который запрещает работу элементов 9 сравнения, то на выходе элемента 9 сравнения.будет нулевой сигнал. Этот сигнал открывает элементы И 14.К,1 и 14.К.2. Поэтому очередной импульс с входа 28 пройдет через открытый элемент И 14 и установит триггер И в нулевое состояние. Соответствующий процессор вновь готов принять задачу для обслуживания.

Рассмотрим работу устройства в режиме II, Сущность этого режима заключается в следующим.. Пусть необходимо решить пакет задач с повышен ной надежностью получения достоверного результата, Если учесть, что во время решения задачи процессор может дать сбой или отказать, то на выход, поступит неверный результат решения. Чтобы этого избежать, в данном устройстве каждая задача решается на двух процессорах одновременно, После решения задачи в процессорах сравнение результатов решения позволяет определить, правильно решена за846«

дача или нет. В случае несовпадения кодов результата задача передается другой паре процессоров, которая дала несравнение с целью определения причины несовпадения (сбой или отказ). В режиме II на входе 29 постоянi

5

0

0

но присутствует единичный сигнал. Этот сигнал, поступая на входы элемента. ИЛИ 20, позволяет вырабатывать управляющие сигналы, разрешающие поступление очередной задачи одновременно на выходы двух блоков элементов И 12. Поэтому каждая задача будет поступать для решения одновременно в два процессора. Сигнал с входа 29 разрешает работу элементов 9 сравнения.

При распределении задач по процессорам устройство в режиме II работает аналогично режиму I, за исключением, того, что одна задача поступает в два процессора. При выполнении задачи процессоры одного канала выставляют коды результатов решения задачи 5 на выходы 45, По переднему фронту

импульсов, сигнализирующих об оконча-. нии решения задачи, эти коды записываются в регистры 22,

Далее возможно несколько вариантов работы устройства.

Рассмотрим самый простой случай, когда коды решения задачи,выданные процессорами, совпали. В этом случае на выходе элемента 9 сравнения будет нулевой сигнал. Этот сигнал откроет элементы И 14. Следовательно, синхронизирующий сигнал с входа 28 пройдет через элементы И 14 на установочное входы триггеров 11 соответственно, В результате канал вернется в исходное положение и будет готов к приему очередной задачи.

Рассмотрим случай, когда коды решения задач, поступившие на выходы 45, 5 не совпали. В этом случае на выходе элемента 9 сравнения будет единичный сигнал. Этот сигнал закроет элементы И I4 и поэтому сигнал с входа 28 не пройдет на сброс триггеров 11. Единич- сигнал с выхода элемента 9 (сравнения поступит на вход элемента -И 16, на выходе которого появится единичный сигнал. Единичный сигнал появится только в том случаеэ если нет аналогичной ситуации в канале с меньшим порядковым номером, который обладает-/большим приоритетом. Сигнал с выхода элемента И 16 откроет коммутатор 2 для прохода кода задачи t

5

0

5

выхода регистра 10 (код задачи ъ ре гистр 10 записывается одновременно с поступлением задачи в процессор для обслуживания по заднему фронту импульса с выхода соответствующего элемента И 13), Задача с выхода коммутатора 2 через коммутатор 3 поступит для распределения в каналы 7 где она распределится в свободный ка- нал для решения Одновременно с этим задача повторно поступит в канал 7. Повторное поступление задачи обеспечит единичный сигнал с выхода элемен- та И 16, который через элементы ИЛИ 21 откроет блоки элементов И 12. Код отказавшего канала запишется в ре- гистр 19 канала, взявшего на обслуживание задачу отказавшего канала. Пр появлении единичного сигнала на выходе элемента и 16 открывается элемент-И 17 для прохождения синхро- импульсов с входа 27. Элемент И 17 от кроется, если в устройстве есть сво-i бодные каналы.Если свободных кана- лов нет, то нерешенная (отказавшая) задача ожидает освобождения процессоров в регистре 10, При освобождении процессоров появляется единичный сигнал на выходе элемента ИННЕ 6. Очередной синхроимпульс с входа 27 трот идет через открытый элемент И 17 и задним фронтом запустит одновибра- тор 26. Импульсом с выхода одновибра- тора 26 процессоры данного канала устанавливаются в нулевое состояние. Импульс с выхода одновибратора 26 установит триггер 24 в единичное состояние и сбросит регистры 22 в ноль,

На выходе элемента 9 сравнения появится нулевой сигнал. На выходе элемента И I 6 также установится нулевой сигнал.

После решения задачи в каналах 7 в регистры 22 записываются коды ее решения. На выходах элементов 9 сравнения появляются соответствующие сигналы. Если задача решена правильно 4 в обоих каналах, то аналогично описан ному триггеры 11 устанавливаются в нулевое состояние, Кроме того, в канале 7 триггер 24 устанавливается в нулевое состояние импульсом с выхода элемента И 14. Каналы 7 готовы к

50

выдает сигнал несовпадения кодов, а элемент 9К сравнения - сигнал совпа дения кодов. В этом случае единичный сигнал с выхода Кто разряда регистра 19 поступает на вход элемента ИЛИ 23. Единичный сигнал с выхода, элемента ИЛИ 23 откроет элемент И 15, на выходе которого появится единичный сигнал. Этот сигнал поступит на вход элемента ИЛИ 30 и откроет элементы И 25, Так как в регистре 19 единица записа на только в К-м разряде, то, следова тельно, появится единичный сигнал - только на выходе элемента И 25. Таки образом, появляются единичные сигналы на выходах элементов ИЛИ 30, Эти сигналы поступают на входы регистра блока 33 управления. По переднему фронту импульса с входа 48 коды двух каналов,, решающих одну задачу, запишутся в регистр 61, т.е. в регистр 6 запишется код, содержащий единицы только в разрядах К и М. На выходе преобразователя 65 кодов появится ко который разрешит проход через четыре коммутатора 31 кодов результатов реш ния задач с выходов регистров 22 соответственно, Коды результатов решения задачи в процессорах каналов 7 поступят в блок 32 сравнения, где пр изойдет сравнение каждый с каждым. Результат сравнения по заднему фронту импульса с входа 48 запишется в регистр 62. Длительность импульса на входе 48 должна быть больше длительности переходных процессоров в

принятию новых задач. При этом делает- 3 цепочке последовательного срабатыва- 5 8468

Если элемент 9 сравнения выдает4 сигнал несовпадения кодов, а элемент 9 сравнения выдает сигнал совпадения кодов, то устройство работает следующим образом. По очередному синхроим-- пульсу с входа 28 триггер 50 устанавливается в единичное состояние. Сигнал с его инверсного выхода закрывает элемент И 16, На его выходе не будет единичного сигнала. Таким образом, делается вывод, что один или оба процессора канала отказали, о чем выдается информационный сигнал на выход 49 устройства. Канал 7 в этом случае работает без изменений. ,

Рассмотрим вариант работы устройства, когда элемент 9М сравнения

выдает сигнал несовпадения кодов, а элемент 9К сравнения - сигнал совпадения кодов. В этом случае единичный сигнал с выхода Кто разряда регистра 19 поступает на вход элемента ИЛИ 23. Единичный сигнал с выхода, элемента ИЛИ 23 откроет элемент И 15, на выходе которого появится единичный сигнал. Этот сигнал поступит на вход элемента ИЛИ 30 и откроет элементы И 25, Так как в регистре 19 единица записана только в К-м разряде, то, следовательно, появится единичный сигнал - только на выходе элемента И 25. Таким образом, появляются единичные сигна лы на выходах элементов ИЛИ 30, Эти сигналы поступают на входы регистра 61 блока 33 управления. По переднему фронту импульса с входа 48 коды двух каналов,, решающих одну задачу, запишутся в регистр 61, т.е. в регистр 61 запишется код, содержащий единицы только в разрядах К и М. На выходе преобразователя 65 кодов появится код, который разрешит проход через четыре коммутатора 31 кодов результатов решения задач с выходов регистров 22 соответственно, Коды результатов решения задачи в процессорах каналов 7 поступят в блок 32 сравнения, где произойдет сравнение каждый с каждым. Результат сравнения по заднему фронту импульса с входа 48 запишется в регистр 62. Длительность импульса на входе 48 должна быть больше длительности переходных процессоров в

цепочке последовательного срабатыва

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1988 |

|

SU1569831A1 |

| Многопроцессорная система | 1989 |

|

SU1695318A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| Многопроцессорная система | 1989 |

|

SU1741144A1 |

| Многопроцессорная вычислительная система | 1991 |

|

SU1837309A1 |

| Многопроцессорная система | 1990 |

|

SU1783538A1 |

| Устройство для распределения заданий процессорам | 1988 |

|

SU1543404A1 |

| Многопроцессорная система | 1987 |

|

SU1494005A1 |

| Устройство приоритета | 1990 |

|

SU1742820A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1277111A1 |

Изобретение относится к вычисли- тельной технике и может быть использовано в отказоустойчивых многопроцессорных системах для распределения задач между процессорами. Цель изобретения - повышение производительности за счет определения отказавшего.процессора одновременно с повторным решением задачи. В устройство введены третий коммутатор, блок сравнения, блок управления,, группа элементов ИЛИ, а в каждый канал - группа элементов И и четвертый элемент ИЛИ, Устройство может работать в режиме повышенной производительности решения задач и в , режиме повышенной надежности решения задач. 1 з.п, , 4 ил.

ся вывод, что в канале 7 при первом цикле решения задачи произошел сбой и процессоры исправны.

ния коммутаторов 31 и блока 32 сравнения. Поступив на вход преобразователя 65, результат сравнения изменит код на выходе преобразователя 65 кодов. На его выходах появятся сигналы, соответствующие процессорам, которые выдали неправильные коды решения.

Эти сигналы поступят на выход 4. Кроме того, поступит соответствующий код на вход блока элементов И 64. По сигналу с входа 28 этот код пройдет на выход блока Элементов И 64 и установит регистры 10 в нулевое состояние так как задача решена,

Рассмотрим работу устройства в случае, когда оба канала 7 «К и 7.М при решении одной задачи выдали несовпадение кодов результатов решения, В этом случае в канапе 7,К по очередному синхроимпульсу с входа 28 триггер 50,К установится в единичное состояние. Поэтому элемент И 16.К будет закрыт, Канал выведен из конфигурации устройства, Для включения канала в работу после проведения профилактических мероприятий необходимо обнулить триггеры 24.К и 50,К, а также регистры 22,К,1 и 22.К.2 (цепи установки исходчого состояния не пока заны).

В этом случае возможны два варианта работы устройства. Это связано с тем, что в каждом из двух каналов может отказать по одному процессору, а в двух других процессорах задача решена правильно, поэтому неэффективно задачу еще раз посылать на обслуживание в один из каналов.

Рассмотрим этот вариант работы Устройства.

В этом случае аналогично описанному код каналов 7.К и 7.М, в которых решалась одна задача, запишется в регистр 61 Преобразователь 65 кода выдаст код, разрешающий проход через коммутатор 31 кодов результатов решения задачи из регистров 22.К.1, 22.К.2, 22.М.1 и 22.М.2. Код результата сравнения запишется в регистр 62 Преобразователь 65 кода выдаст на соответствующие входы регистра 63 единичные сигналы соответствующим процессорам, которые выдали неправильный код решения задачи. По очередному синхроимпульсу с входа 28 разряд регистра 63, соответствующий отказавшему процессору канала 7.К, установится в 1, Таким образом, сразу же имеется информация об отказавшем процессоре в канале и не надо прове-

0

5

рять оба процессора. На вход блока элементов И 64 поступит код каналов 7.К и 7.М для того, чтобы установить регистры 10.К и 10.М в нулевое состояние, так как задача решена.

В случае, если блок 32 сравнения выдает код, обозначающий, что все процессоры выдали различные результаты решения задач, то оба разряда регистра 63, соответствующие каналу 7,К, устанавливаются в единичное состояние, а на вход блока элементов И 64 подается нулевой код, В этом случае задача из канала 7.М поступит на обслуживание в другой канал аналогично описанному.

Формула изобретения

0

0

5

0

5

0

5

П 16

нале подключены к первым входам соответственно второго и третьего элементов ИЛИ, выходы которых подключены к управляющим входам -соответственно первого и второго блоков элементов И, в каждом канале выходы второго блока элементов И подключены к информационным входам первого регистра, выходы которого подключены к соответствую- щим информационным входам второго коммутатора, выходы второго коммутатора подключены к второй группе информа- ционных входов первого коммутатора, .в каждом канале выход второго элемента И подключен к входам синхронизации первого и второго регистров, в каждом канале сигнальные входы устройства подключены к входам синхронизации третьего и четвертого регистров и к первым прямым входам третьего и чет- вертого элементов и своего канала, выходы которых подключены к входам сброса соответственно первого и второго триггеров своего канала, в

каждом канале выход четвертого элемен та И подключен к первому входу сброса второго регистра и к входу сброса третьего триггера своего канала, вы- ход которого подключен к первому установочному входу четвертого триггера своего канала, инверсный выход четвертого триггера в каждом канале подключен к первому входу пятого элемента И своего канала, выход которого подключен к вторым входам второго и третьего элементов ИЛИ своего канала, к первому входу шестого элемента И своего канала, к информационным входам вторых регистров всех каналов, к инверсным входам пятых элементов И каналов с большим порядковым номером и к соответствующему управляющему входу второго коммутатора, кодовые входы устройства в каждом канале подключены к информационным входам третьего и четвертого регистров, выходы которых подключены к входам элемента сравнения своего канала, выход элемента сравнения в каждом канале подключен к инверсным входам третьего и четвертого элементов И, к второму установочному входу четвертого триггера, к второму входу пятого элемента И и к первому входу седьмого элемента И, прямые выходы первого и второго триггеров в каждом канале подключены соответственно к первому и второму входам восьмого элемен12

Т,

5

0

та И своего канала, выход восьмого элемента И подключен к второму входу первого и к третьему входу второго элемента И каналов с большим порядковым номером, в каждом канале выход шестого элемента И через одновибратор подключен к входу установки в l третьего триггера и к второму входу сброса второго и к входам сброса третьего и четвертого регистров своего канала, первый синхронизирующий вход устройства подключен Гк первому синхронизирующему входу блока регистров, к первому входу элемента И, к вторым входам шестых элементов И всех каналов, второй синхронизирующий вход устройства подключен к второму синхронизирующему входу блока регистров, к вторым прямым входам третьего и четвертого элементов И всех каналов, к тактовым входам четвертых , триггеров всех каналов, вход режима устройства подключен к прямым вхо5 Дам первых элементов ИЛИ всех каналов и к входам разрешения элементов срав- нения всех каналов, выходы восьмых элементов каналов соединены с входами элемента И-НЕ, выход элемента И-НЕ

Q подключен к третьим входам шестых элементов И всех каналов, инверсные выходы четвертых триггеров каналов являются выходами прерывания устройства, выход элемента ИЛИ-НЕ подключен к прямому и инверсному управляющим входам первого ко ммутатора, сигнальный выход блока регистров подключен к второму входу элемента И, выход которого подключен к тактовым входам первого и второго триггеров всех каналов, входы элемента ИЛИ-НЕ соединены с выходами второго коммутатора, о т- личающееся тем, что, с целью повышения производительности за счет определения отказавшего процессора одновременно с повторным решением задачи, в устройство дополнительно введены третий коммутатор, блок сравнения, блок управления, группа элементов ИЛИ, а в каждый канал - , группа элементов И и четвертый элемент ИЛИ, причем в каждом канале выходы второго регистра подключены к входам четвертого элемента ИЛИ, выход которого подключен к второму входу седьмого элемента И, в каждом канале выход седьмого элемента И подключен кУинверсиым входам седьмых элементов И каналов с большими порядковыми но5

0

5

0

5

13

мерами, выход седьмого элемента И каждого канала подключен к первым входам элементов И группы, к первому входу одноименного элемента ИЛИ группы, в каждом канале выходы второго ре

гистра подключены к вторым входам элементов И группы,выходы которых подключены к соответствующим входам одноименных элементов ИЛИ группы, выходы третьего и четвертого регистров всех каналов подключены к соответствующим информационным входам третье- го коммутатора, выходы которого подключены к входам блока сравнения, выход блока сравнения подключен к первой группе информационных входов блока управления, выходы группы элементов ИЛИ подключены к второй группе информационных входов блока управления, каждый выход первой группы информационных выходов которого подключен к входу сброса первого регистра одноименного канала, а вторая труп- па информационных выходов блока управ-25 двоичного кода в позиционныйfвходы

ления подключена к управляющим входам третьего коммутатора, выходы третьих триггеров всех каналов подключены к третьей группе информационных входов блока управления, второй и тре-эп тий входы синхронизации устройства подключены соответственно к первому и второму входам синхронизации блока управления, вход сброса которого соединен с первым входом синхронизации

35

которого соединены с выходами первого и второго регистров, установоч ные входы третьего регистра соедине с его выходами, с выходами преобраз вателя двоичного кода в позиционный и с второй и третьей группами инфор ционных выходов блока, первая групп информационных выходов которого сое динена с группой выходов блока элементов Ив

1636846

14

5

10

15

20

устройства, группа кодовых выходов которого соединена с третьей группой информационных выходов блока управления.

2, Устройство по п. отличающееся тем, что блок управления содержит три регистра,преобразователь двоичного кода в позиционный и блок элементов И, причем группы информационных входов первого, второго и третьего регистров соединены соответственно с первой, второй и третьей группами информацоинных входов блока соответственно, входы синхронизации и входы сброса первого и второго регистров соединены соответственно с вторым входом синхрониза- ции и входом сброса блока, вход синхронизации третьего регистра соединен с первым входом синхронизации блока и с управляющим входом блока элементов И, информационные входы которого соединены с выходами преобразователя

которого соединены с выходами первого и второго регистров, установочные входы третьего регистра соединены с его выходами, с выходами преобразователя двоичного кода в позиционный и с второй и третьей группами информационных выходов блока, первая группа- информационных выходов которого соединена с группой выходов блока элементов Ив

9t789Ј9l

#0

Г

ГЈ5

IIS

a

o- ZЈ

iis

TiS

TbS

X-

v

ЙТ

2 гл

Г

H SS

т

u bS

w

JЈ. /7ф

я

TO

r

ISS

fl

TbS

Jl

гк

j

; i

MS9

81 &

M

a

U SS

i 6

8

J

Ј91

ПИ

riii

47 i

| Устройство для распределения заданий процессорам | 1985 |

|

SU1269136A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-23—Публикация

1988-12-26—Подача