фаг.1

Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчиков информации, используемых в автоматизированных систе- мах управления, обработки информации связи.

Цель изобретения - повышение оперативности функционирования.

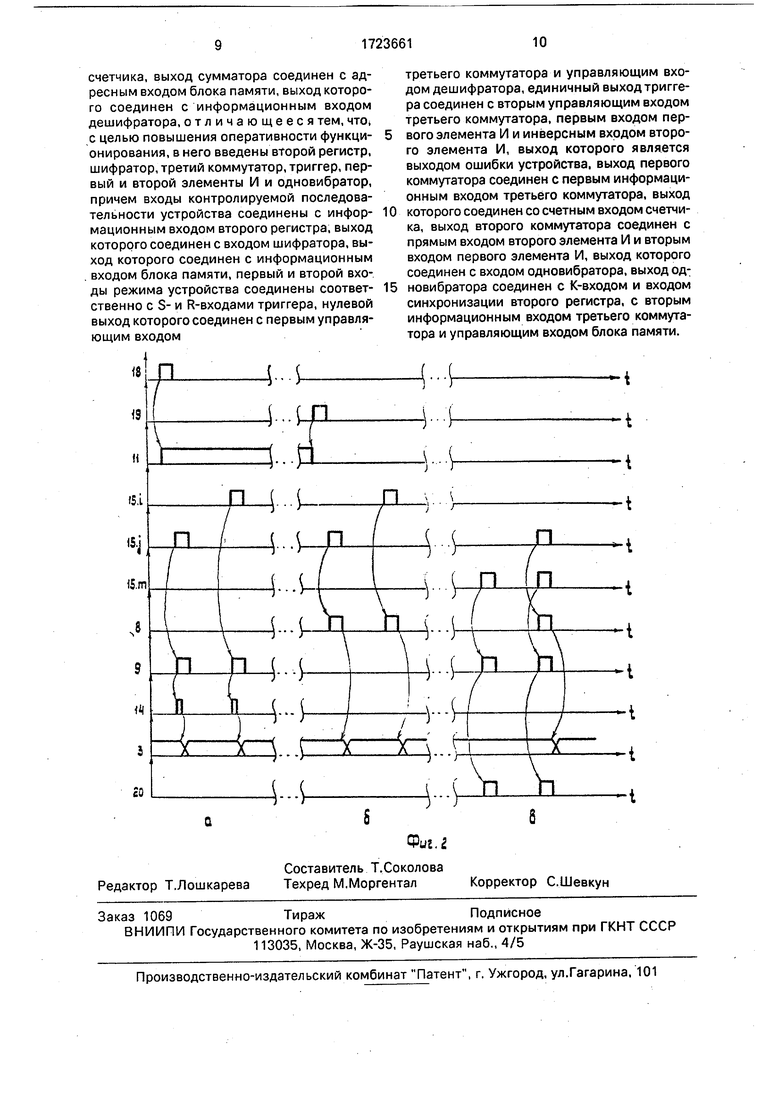

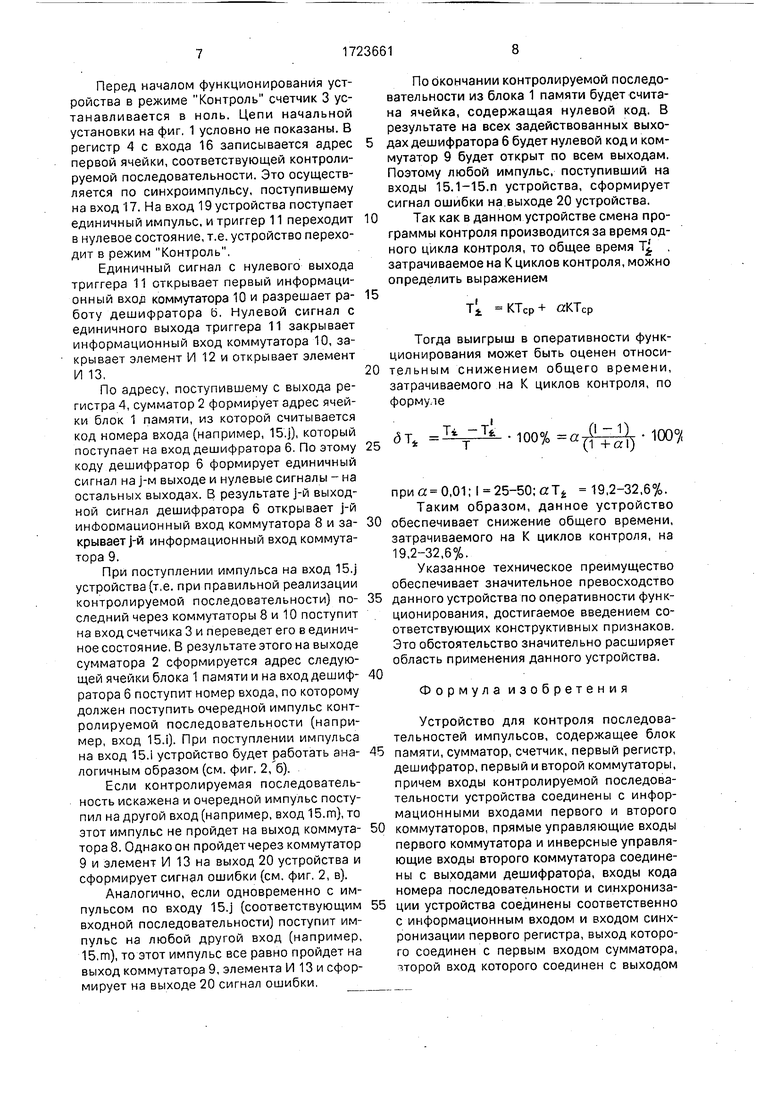

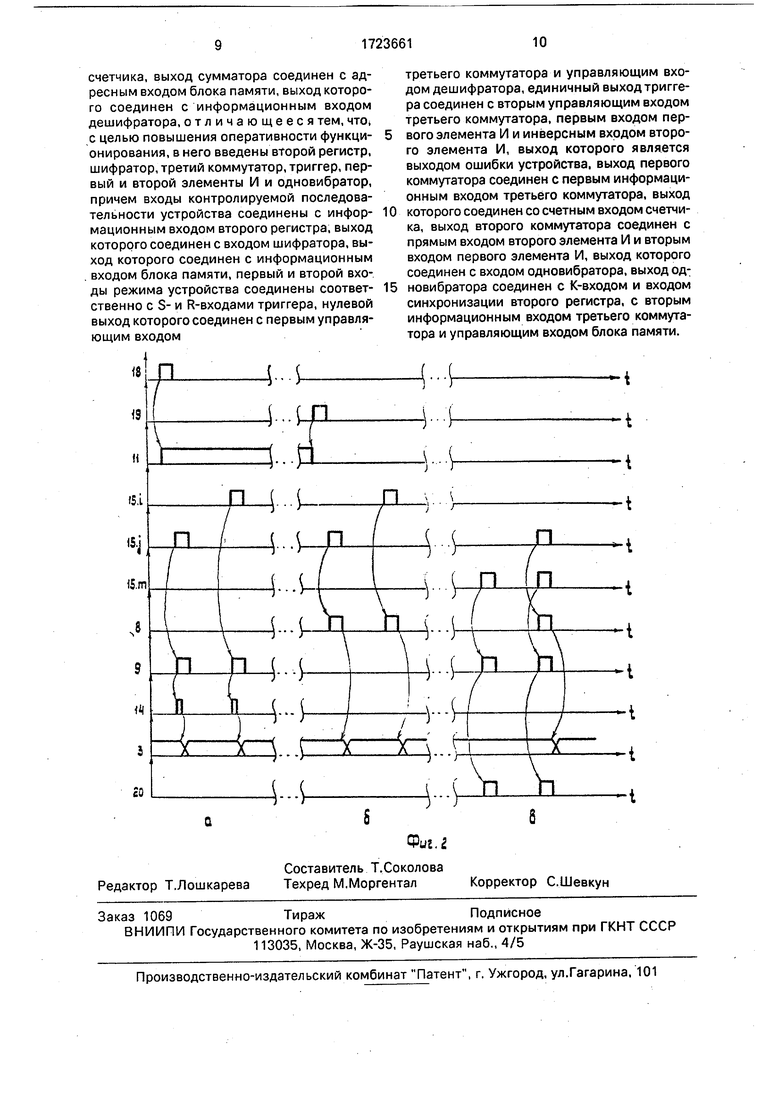

На фиг. 1 приведена электрическая фун- кциональная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство для контроля последовательностей импульсов содержит блок 1 па- мяти, сумматор 2, счетчик 3, регистры 4 и 5, дешифратор 7, первый 8, второй 9 и третий 10 коммутаторы, триггер 11, первый 12 и второй 13 элементы И, одновибратор 14, входы 15 контролируемой последователь- ности, входы номера контролируемой последовательности 16 и синхронизации 17, первый 18 и второй 19 входы режимов работы устройства и выход 20 ошибки,

Входы 15 контролируемой последова- тельности устройства соединены с информационными входами первого 8 и второго 9 коммутаторов. Прямые управляющие входы первого коммутатора 8 и инверсные управляющие входы второго коммутатора 9 сое- динены с выходами дешифратора 6. Входы кода номера последовательности 16 и синхронизации 17 устройства соединены соответственно с информационным входом и входом синхронизации первого регистра 4, выход которого соединен с первым входом сумматора 2, второй вход которого соединен с выходом счетчика 3. Выход сумматора 2 соединен с адресным входом блока 1 памяти, выход которого соединен с информа- ционным входом дешифратора 6.

Входы 15 контролируемой последовательности устройства соединены с информационным входом второго регистра 5, выход которого соединен с входом шифра- тора 7. Выход шифратора 7 соединен с информационным входом блока 1 памяти.

Первый 18 и второй 19 входы режимов работы устройства соединены соответственное S-и R-входами триггера 11, нулевой выход которого соединен с первыми управляющим входом третьего коммутатора 10 и управляющим входом дешифратора 6. Единичный выход триггера 11 соединен с вто- рым управляющим входом третьего коммутатора 10, причем первым входом первого элемента И 12 и инверсным входом второго элемента И 13, выход которого является выходом 20 ошибки устройства.

Выход первого коммутатора 8 соединен с первым информационным входом третьего коммутатора 10, выход которого соединен со счетным входом счетчика 3. Выход второго коммутатора 9 соединен с прямым входом второго элемента И 13 и вторым входом первого элемента И 12, выход которого соединен с входом одновибратора 14. Выход одновибратора 14 соединен с К-вхо- дом и входом и синхронизации второго регистра 5, с вторым информационным входом третьего регистра 5, с вторым.информационным входом третье го коммутатора 10 и управляющим входом (WR) блока 1 памяти.

Рассмотрим назначение элементов предлагаемого устройства.

Блок 1 памяти представляет собой ОЗУ. Он предназначен для записи и хранения программ контроля последовательностей импульсов, поступающих на входы 15 устройства. Разрядность ячейки памяти определяется числом п входов 15, по которым поступают импульсы контролируемых последовательностей, и обеспечивает возможность записи кода номера входа, по которому должен поступить очередной импульс контролируемой последовательности. Запись информации, поступившей на D- вход блока 1 памяти, осуществляется в ячейку, код адреса которой поступает на адресный вход по импульсу, поступившему на WR-вход.

Сумматор 2 комбинационный служит для формирования адреса ячейки ОЗУ как суммы адреса начальной ячейки памяти, соответствующей контролируемой последовательности (с выхода регистра 4), и номера ячейки, соответствующего текущего такту контроля последовательности импульсов (выходы счетчика 3).

Счетчик 3 служит для подсчета числа импульсов, поступивших на входы 15 устройства и соответствующих контролируемой последовательности,

Регистр 4 предназначен для записи адреса начальной ячейки зоны памяти, выделяемой для контроля конкретной последовательности импульсов. Запись адреса осуществляется с входа 16 устройства по синхроимпульсу на входе 17 устройства.

Регистр 5 предназначен для записи и хранения информации, поступившей на входы 15 контролируемой последовательности устройства. Запись информации в регистр 5 осуществляется асинхронно с S-входов, а обнуление регистра 5 осуществляется по заднему фронту импульса, поступающего одновременно на его К- и С-входы.

Дешифратор 6 в соответствии с кодом, поступившим с выхода блока 1 памяти, фор- мируетуправляющие сигналы на входы коммутаторов 8 и 9, что позволяет различать импульсы, принадлежащие и не принадлежащие контролируемой последовательности. Дешифратор 6 - управляемый. Сигнал на его выходе будет сформирован только при наличии единичного сигнала на управляющем входе. При нулевом управляющем сигнале на всех выходах дешифратора 6 будут присутствовать нулевые сигналы.

Шифратор 7 в соответствии с унитарным кодом, поступающим на его вход, формирует на своем выходе двоичный код (код номера кода, по которому поступил импульс) для записи его в блок 1 памяти.

Коммутатор 8 служит для формирования на своем выходе импульса, если поступивший на один из входов 15 устройства импульс соответствует контролируемой последовательности импульсов.

Коммутатор 9 формирует на своем выхо- .де импульс при поступлении очередного импульса на один из входов 15 устройства в режиме Программирование, а в режиме Контроль - если поступивший на один из входов 15 устройства импульс не принадлежит контролируемой последовательности.

Коммутатор 10 предназначен для формирования импульсов на счетный вход счетчика 3,

Триггер 11 предназначен для управления режимов работы устройства. В единичное состояние триггер 11 переводится единичным сигналом, поступившим на его S-вход, в нулевое - на R-вход. Единичное состояние триггера 11 соответствует режиму Программирование, а нулевое - режиму Контроль.

Элемент И 12 служит для формирования импульса на входе одновибратора 14.

Элемент И 13 предназначен для формирования сигнала ошибки.

Одновибратор 14 служит для синхронизации работы устройства в режиме Программирование.

Устройство для контроля последовательностей импульсов работает следующим образом.

Перед началом функционирования элементы памяти устройства устанавливаются в ноль. Цепи начальной установки на фиг. 1 условно не показаны. В регистр 4 с входа 16 записывается адрес первой ячейки, соответствующей контролируемой последовательности, по синхроимпульсу, поступившему на вход 17, На вход 18 устройства поступает единичный импульс, и триггер 11 переходит в единичное состояние, т.е. устройство переходит в режим Программирование.

Единичный сигнал с единичного выхода триггера 11 закроет элемент И 13, откроет

коммутатор 10 по второму информационному входу и элемент И 12.

Нулевой сигнал с нулевого выхода триггера 11 закроет дешифратор 6. В результате на его выходах будут присутствовать только

нулевые сигналы и коммутатор 8 будет закрыт по всем информационным входам, а коммутатор 9 - открыт по всем входам.

По адресу, поступившему с выхода регистра 4, сумматор 2 формирует адрес ячейки памяти блока 1 памяти.

При поступлении импульса на один из входов 15 устройства (например, 15.J) последний запишется в j-й разряд регистра 5, поступит на вход шифратора 7, в соответствии с которым он сформирует на D-входе блока 1 памяти двоичный код.

Одновременно с записью в регистр 5

импульс, поступивший на вход 15.J, пройдет

на выход коммутатора 9 и далее через открытый элемент И 12 - на вход одновибратора 14. Последний по переднему фронту поступившего на его вход сигнала сформирует на своем выходе единичный импульс, по заднему фронту которого в блок 1 памяти

запишется код номера входа (в нашем случае 15J), по которому поступил импульс, об- нулится регистр. 5, и через коммутатор 10 поступит на счетный вход счетчика 3. Счетчик 3 увеличит свое состояние на единицу.

В результате этого на выходе сумматора 2 сформируется адрес следующей ячейки памяти ОЗУ,

Следующий импульс, поступивший на один из входов 15(пусть на 15.1-вход), аналогичным образом запишется на 1-й разряд регистра 5, шифратор 7 сформирует на D- входах блока 1 памяти код номера 1-го входа, по которому поступил импульс. Одновременно поступивший импульс пройдет через коммутатор 9, элемент И 12 на вход одновибратора и последний сформирует на своем выходе единичный импульс. В результате код, сформированный шифратором 7, запишется в блок 1 памяти, регистр 5

обнулится, а счетчик увеличит свое состояние еще на единицу и на выходе сумматора 2 будет сформирован адрес следующей ячейки.

При поступлении последующих импульсов на вход 15 устройства цикл работы в режиме Программирование повторяется. В результате в блоке 1 памяти формируется программа контроля данной последовательности импульсов.

Перед началом функционирования устройства в режиме Контроль счетчик 3 устанавливается в ноль. Цепи начальной установки на фиг. 1 условно не показаны. В регистр 4 с входа 16 записывается адрес первой ячейки, соответствующей контролируемой последовательности. Это осуществляется по синхроимпульсу, поступившему на вход 17. На вход 19 устройства поступает единичный импульс, и триггер 11 переходит в нулевое состояние, т.е. устройство переходит в режим Контроль.

Единичный сигнал с нулевого выхода триггера 11 открывает первый информационный вход коммутатора 10 и разрешает работу дешифратора Ь. Нулевой сигнал с единичного выхода триггера 11 закрывает информационный вход коммутатора 10, закрывает элемент И 12 и открывает элемент И 13,

По адресу, поступившему с выхода регистра 4, сумматор 2 формирует адрес ячейки блок 1 памяти, из которой считывается код номера входа (например, 15.), который поступает на вход дешифратора 6. По этому коду дешифратор 6 формирует единичный сигнал на j-м выходе и нулевые сигналы - на остальных выходах. В результате j-й выходной сигнал дешифратора 6 открывает j-й инФоомаиионный вход коммутатора 8 и закрывает j-й информационный вход коммутатора 9.

При поступлении импульса на вход 15J устройства (т.е. при правильной реализации контролируемой последовательности) последний через коммутаторы 8 и 10 поступит на вход счетчика 3 и переведет его в единичное состояние. В результате этого на выходе сумматора 2 сформируется адрес следующей ячейки блока 1 памяти и на вход дешифратора 6 поступит номер входа, по которому должен поступить очередной импульс контролируемой последовательности (например, вход 15.i). При поступлении импульса на вход 15.1 устройство будет работать аналогичным образом (см. фиг. 2, б).

Если контролируемая последовательность искажена и очередной импульс поступил на другой вход (например, вход 15.т), то этот импульс не пройдет на выход коммутатора 8. Однако он пройдет через коммутатор 9 и элемент И 13 на выход 20 устройства и сформирует сигнал ошибки (см. фиг. 2, в).

Аналогично, если одновременно с импульсом по входу 15.J (соответствующим входной последовательности) поступит импульс на любой другой вход (например, 15,т), то этот импульс все равно пройдет на выход коммутатора 9, элемента И 13 и сформирует на выходе 20 сигнал ошибки,

По окончании контролируемой последовательности из блока 1 памяти будет считана ячейка, содержащая нулевой код. В результате на всех задействованных выходах дешифратора 6 будет нулевой код и коммутатор 9 будет открыт по всем выходам. Поэтому любой импульс, поступивший на входы 15.1-15.п устройства, сформирует сигнал ошибки на.выходе 20 устройства.

Так как в данном устройстве смена программы контроля производится за время одного цикла контроля, то общее время Т . затрачиваемое на К циклов контроля, можно определить выражением

КТср+ аКТср

Tk

Тогда выигрыш в оперативности функционирования может быть оценен относи- тельным снижением общего времени, затрачиваемого на К циклов контроля, по формуле

25

Т

100% (

при а 0,01; I 25-50; а Т 19,2-32,6%. Таким образом, данное устройство обеспечивает снижение общего времени, затрачиваемого на К циклов контроля, на 19,2-32,6%.

Указанное техническое преимущество обеспечивает значительное превосходство данного устройства по оперативности функционирования, достигаемое введением соответствующих конструктивных признаков. Это обстоятельство значительно расширяет область применения данного устройства.

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее блок

памяти, сумматор, счетчик, первый регистр, дешифратор, первый и второй коммутаторы, причем входы контролируемой последовательности устройства соединены с информационными входами первого и второго

коммутаторов, прямые управляющие входы первого коммутатора и инверсные управляющие входы второго коммутатора соединены с выходами дешифратора, входы кода номера последовательности и синхронизации устройства соединены соответственно с информационным входом и входом синхронизации первого регистра, выход которого соединен с первым входом сумматора, тгорой вход которого соединен с выходом

счетчика, выход сумматора соединен с адресным входом блока памяти, выход которого соединен с информационным входом дешифратора, отличающееся тем, что; с целью повышения оперативности функционирования, в него введены второй регистр, шифратор, третий коммутатор, триггер, первый и второй элементы И и одновибратор, причем входы контролируемой последовательности устройства соединены с информационным входом второго регистра, выход которого соединен с входом шифратора, выход которого соединен с информационным . входом блока памяти, первый и второй входы режима устройства соединены соответственно с S- и R-входами триггера, нулевой выход которого соединен с первым управляющим входом

третьего коммутатора и управляющим входом дешифратора, единичный выход триггера соединен с вторым управляющим входом третьего коммутатора, первым входом первого элемента И и инверсным входом второго элемента И, выход которого является выходом ошибки устройства, выход первого коммутатора соединен с первым информационным входом третьего коммутатора, выход

которого соединен со счетным входом счетчика, выход второго коммутатора соединен с прямым входом второго элемента И и вторым входом первого элемента И, выход которого соединен с входом одновибратора, выход одновибратора соединен с К-входом и входом синхронизации второго регистра, с вторым информационным входом третьего коммутатора и управляющим входом блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для контроля хода программ ЭВМ | 1987 |

|

SU1430960A1 |

| Устройство для контроля интерфейса ввода-вывода | 1990 |

|

SU1829039A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство для контроля интерфейса ввода-вывода | 1991 |

|

SU1798792A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1619277A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

Изобретение относится к автоматике и цифровой технике и предназначено для проверки сложных блоков синхронизации, контроллеров, датчиков информации. Цель изобретения - повышение оперативности функционирования, достигается путем введения второго регистра 5, шифратора 7, третьего коммутатора 10, триггера 11, первого и второго элементов И 12 и 13 и одно- вибратора 14. Устройство также содержит блок 1 памяти, сумматор 2, счетчик 3, первый регистр 4, дешифратор 6, первый и второй коммутаторы 8 и 9. 2 ил.

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1501064A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1992-03-30—Публикация

1989-10-11—Подача