«

Изобрете.нне относится к вычислительной технике и может быть использовано для сопряжения вычислительных систем, имеющих интерфейс типа обща шина (ОШ), с магистральной микропро цессорной системой (МПС).

Между вычислительной системой, имеющей интерфейс типа ОШ, и МПС довольно часто возникает необходимость обмена блоками информации с макси- мально возможным быстродействием, которое обеспечивало бы передачу все блоков информации, поступающих в МПС от ее периферийных устройств в память ОШ, и прием этих блоков, об- работанных процессором ОШ,

Цель изобретения - повышение скорости обмена.

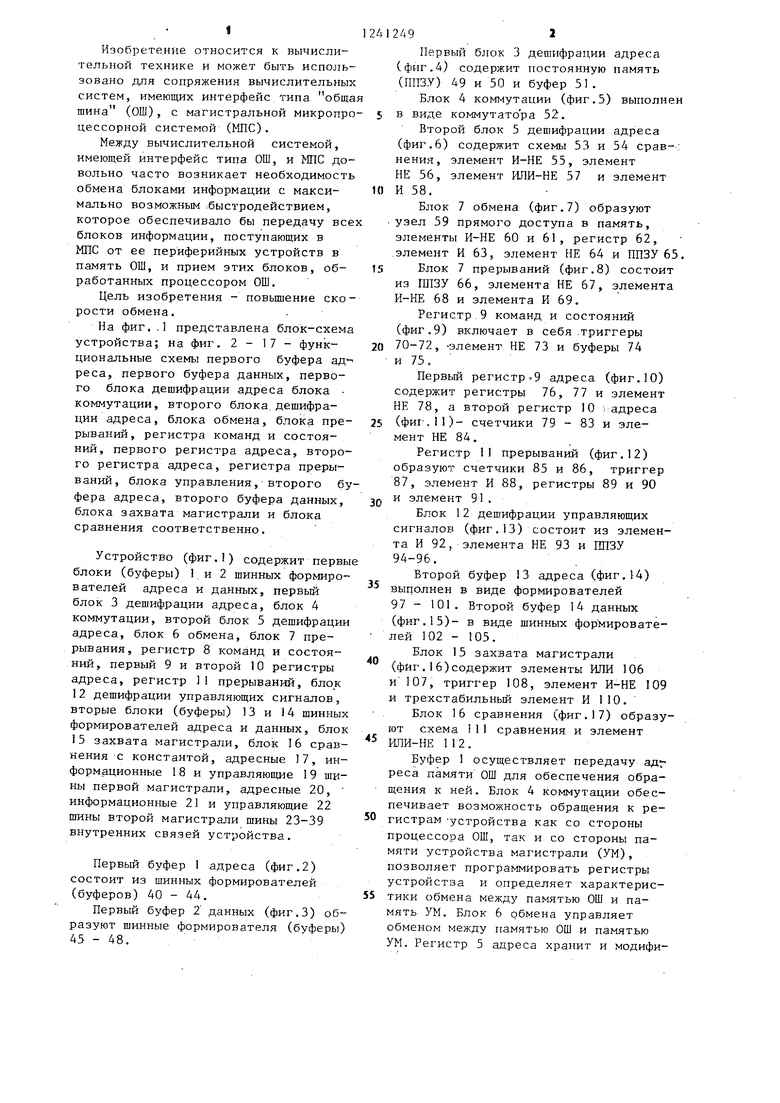

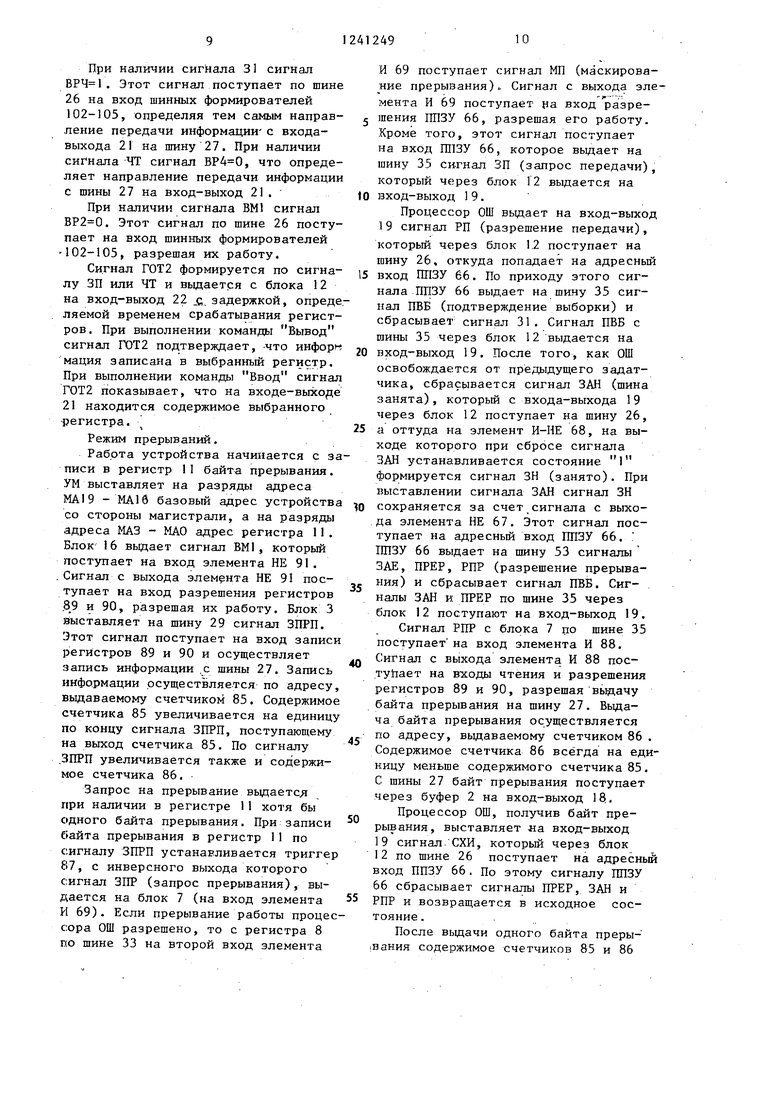

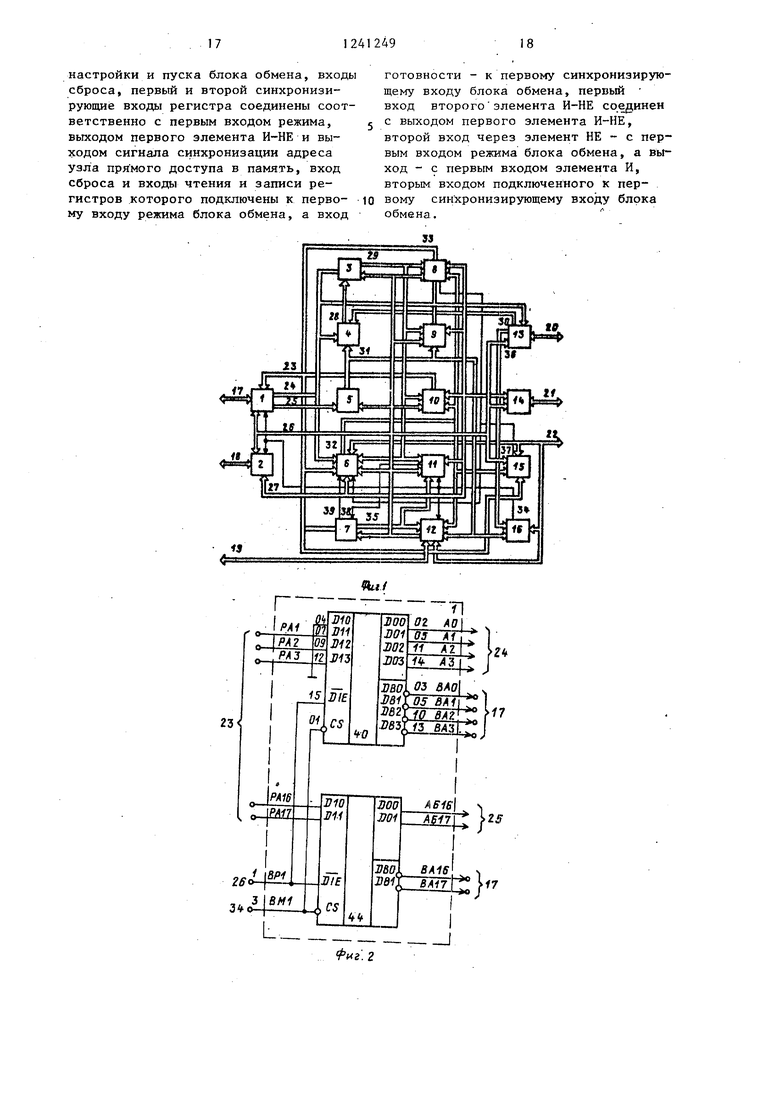

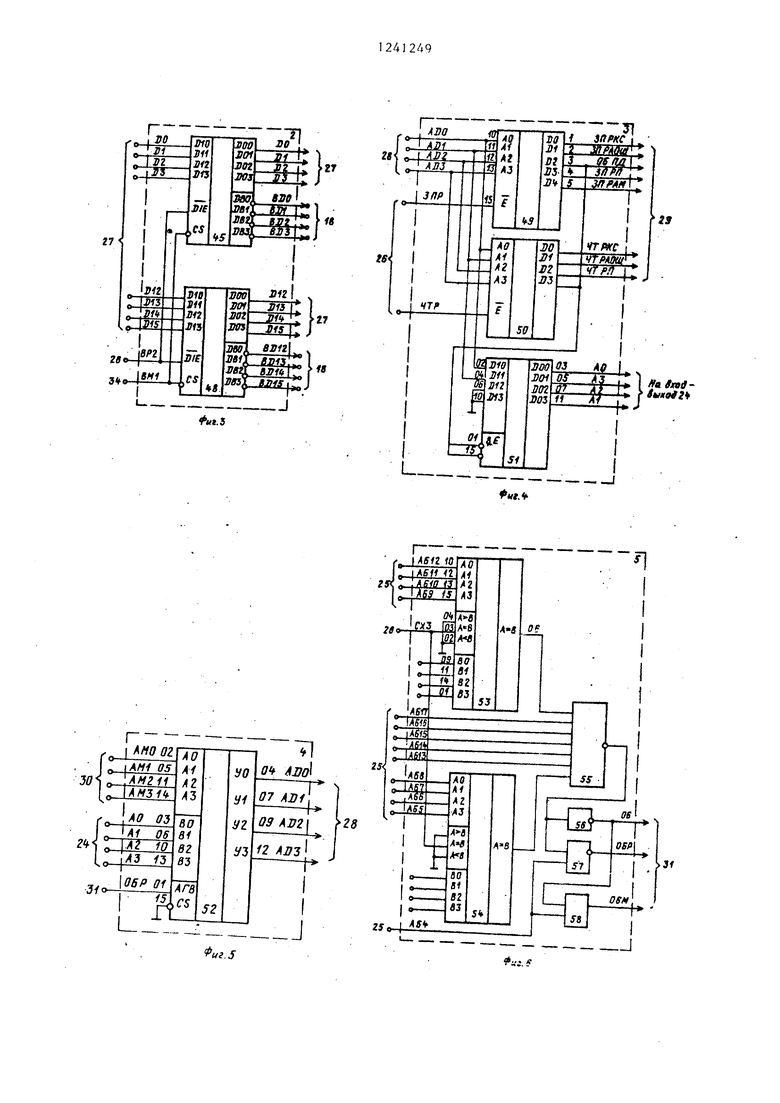

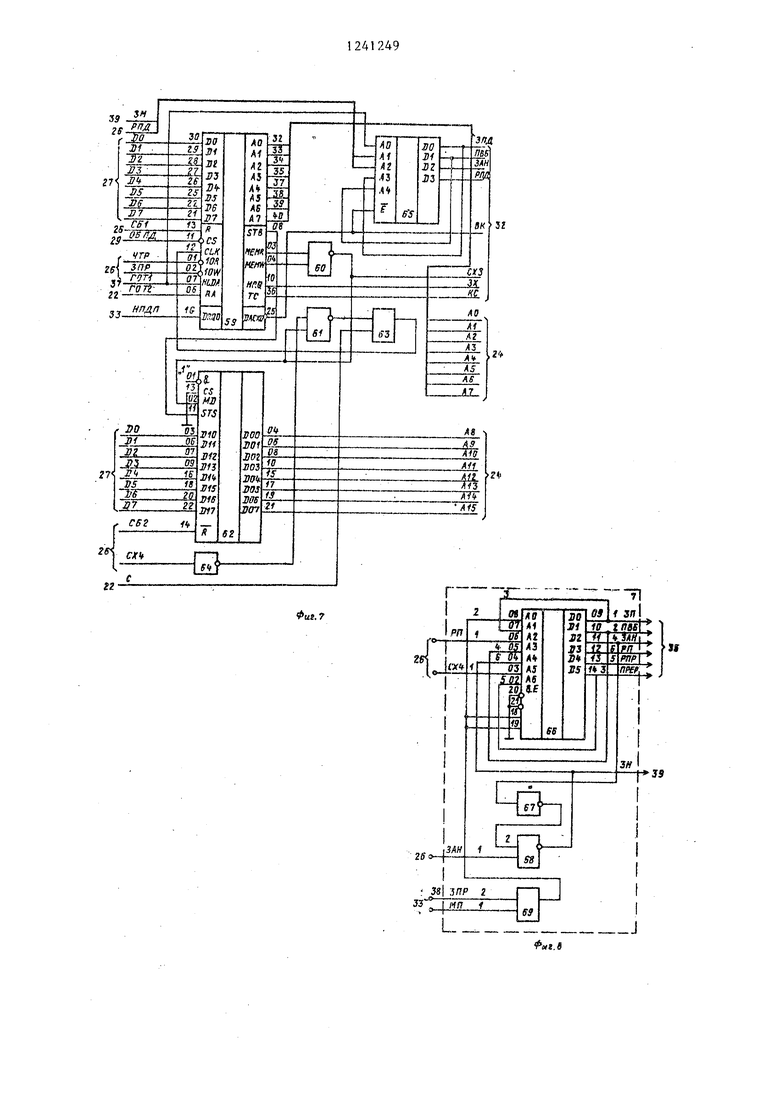

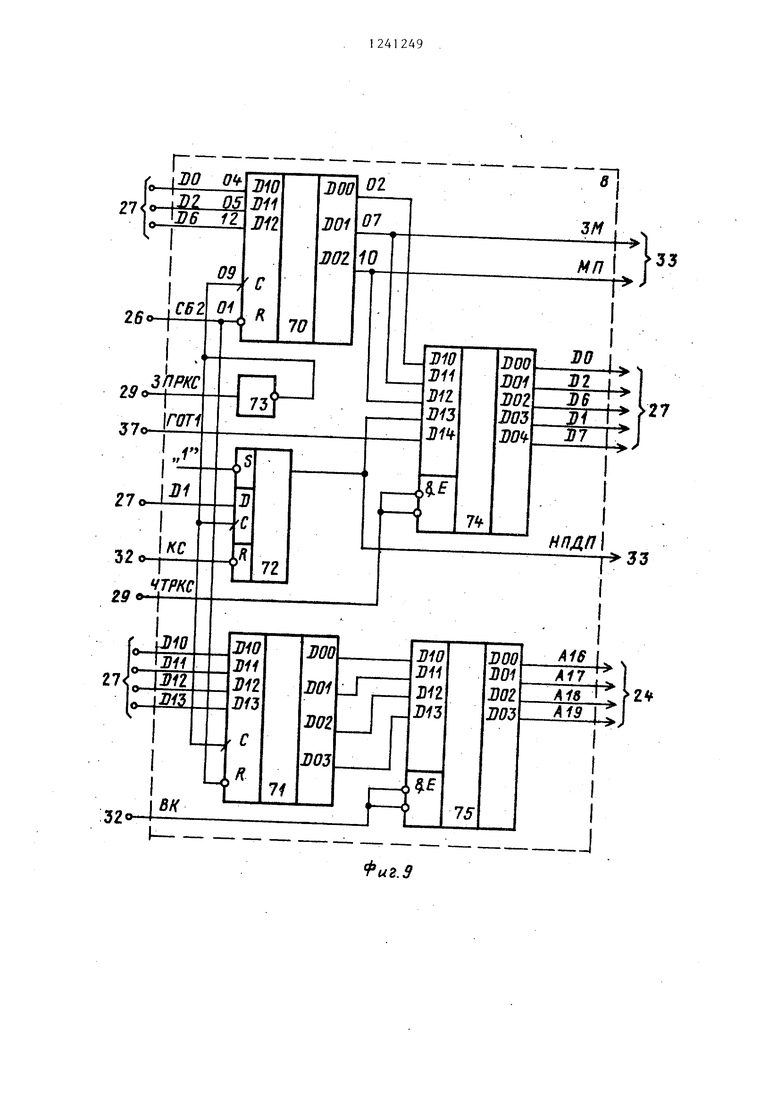

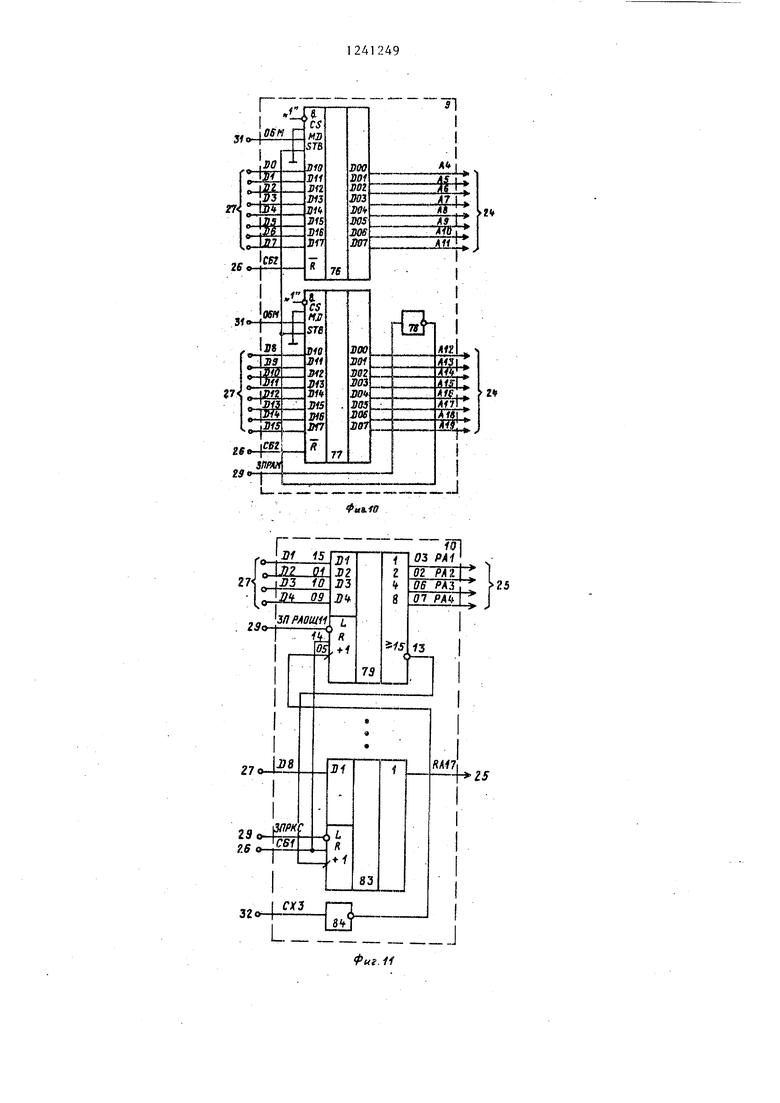

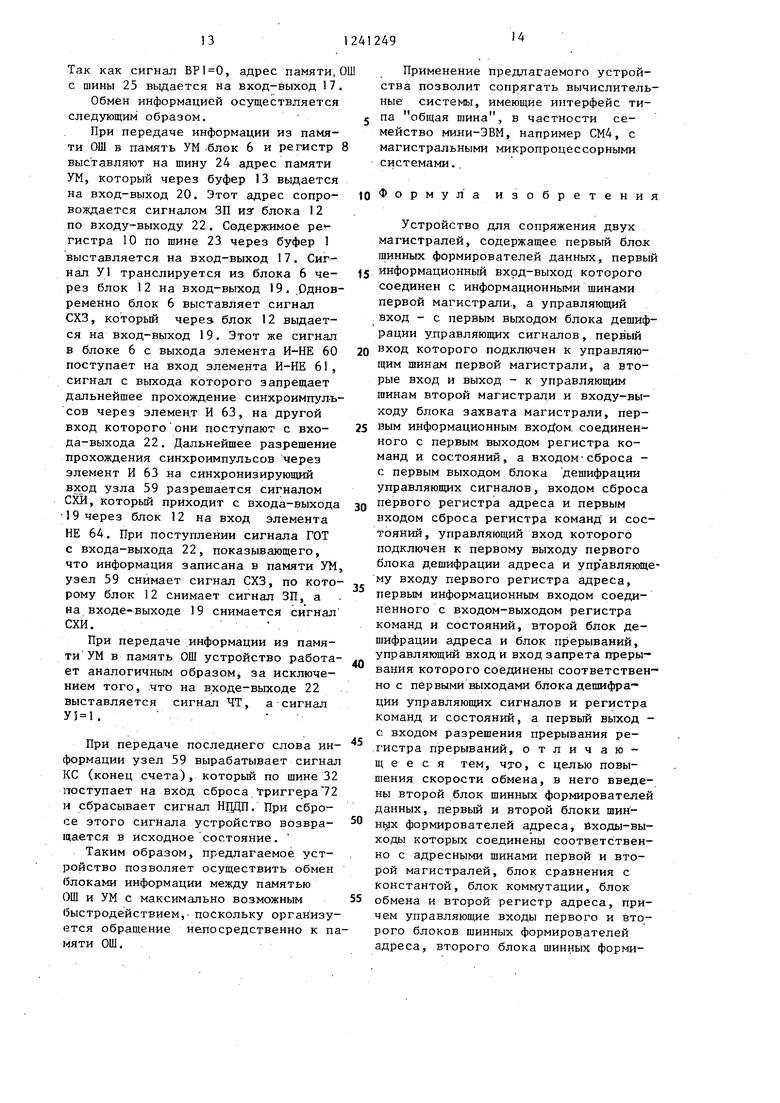

На фиг. .1 представлена блок-схема устройства; на фиг. 2 - 17 - функ- циональные схемы первого буфера ад реса, первого буфера данных, первого блока дешифрации адреса блока коммутации, второго блока,дешифрации адреса, блока обмена, блока пре- рываний, регистра команд и состояний, первого регистра адреса, второго регистра адреса, регистра прерываний, блока управления, второго буфера адреса, второго буфера данных, блока захвата магистрали и блока сравнения соответственно.

Устройство (фиг,1) содержит первы блоки (буферы) 1 и 2 шинных формирователей адреса и данных, первый блок 3 дешифрации адреса, блок 4 коммутации, второй блок 5 дешифрации адреса, блок 6 обмена, блок 7 прерывания, регистр 8 команд и состояний, первый 9 и второй 10 регистры адреса, регистр 1 прерываний, блок 12 дешифрации управляющих сигналов, вторые блоки (буферы) 13 и 14 шинных формирователей адреса и данных, блок 15 захвата магистрали, блок 16 сравнения с константой, адресные 17, информационные 18 и управляющие 19 шины первой магистрали, адресные 20, информационные 21 и управляющие 22 шины второй магистрали шины 23-39 внутренних связей устройства.

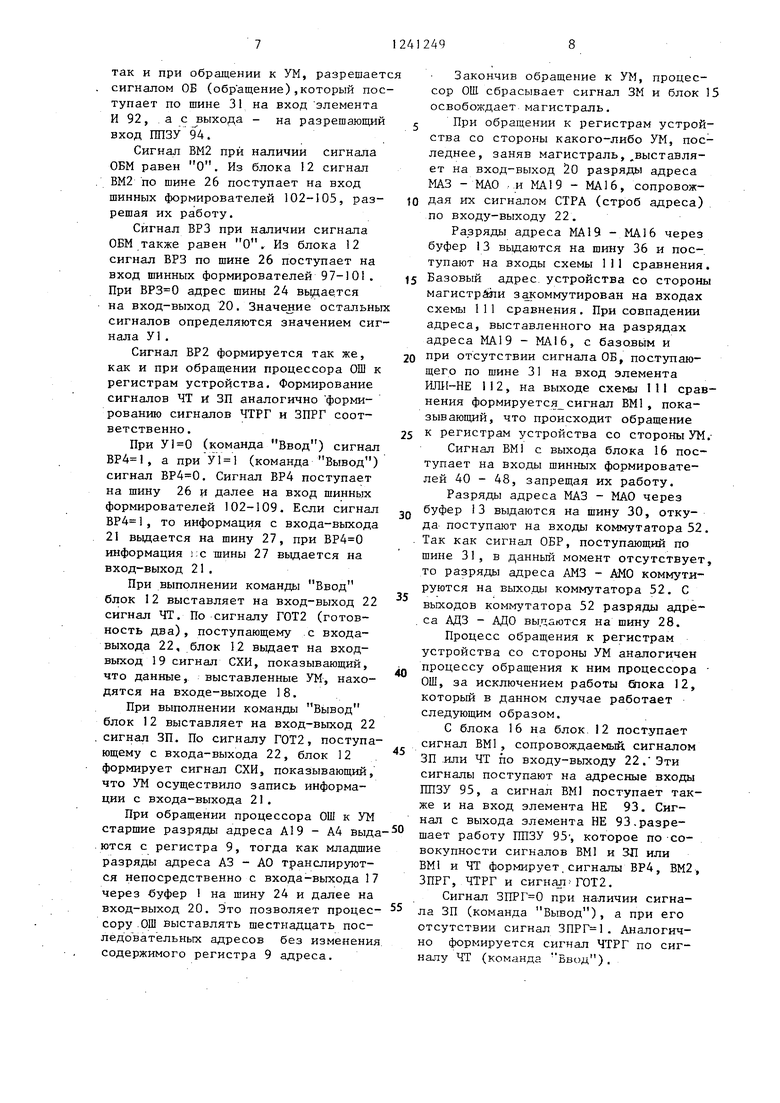

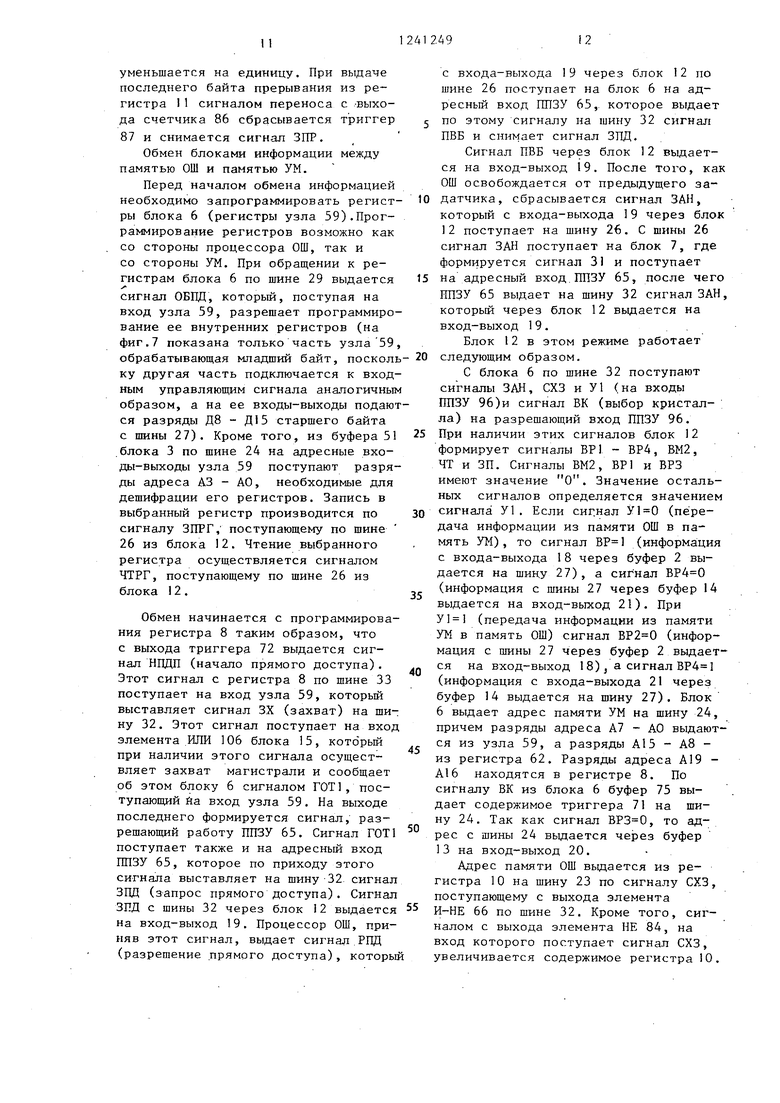

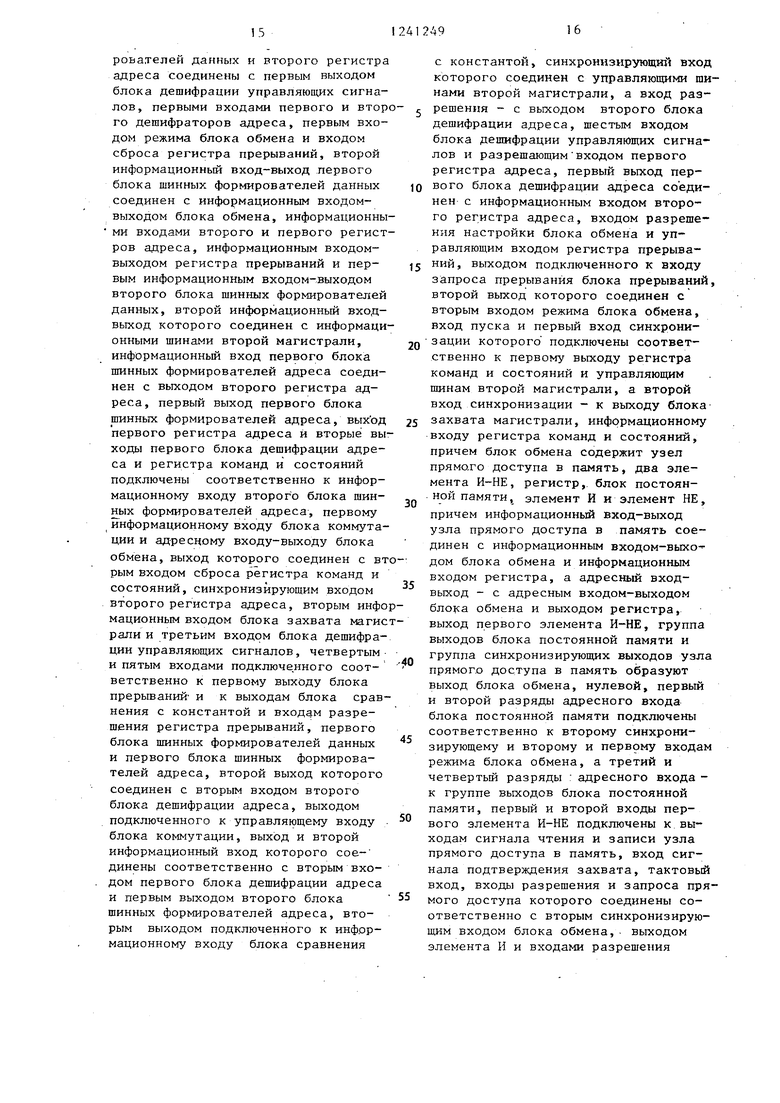

Первый буфер 1 адреса (фиг,2) состоит из шинных формирователей (буферов) 40-44.

Первый буфер 2 данных (фиг,3) образуют шинные формирователя (буферы) 45 - 48,

5

0 5 о

5

5

5

2492

Первый блок 3 дешифрации адреса (фиг.4) содержит постоянную память (ППЗУ) 49 и 50 и буфер 51.

Блок 4 ком1-1утации (фиг,5) выполнен в виде коммутато ра 52.

Второй блок 5 дешифрации адреса (фиг,6) содержит схемы 53 и 54 срав-: нения, элемент И-НЕ 55, элемент НЕ 56, элемент ИЛИ-НЕ 57 и элемент И 58,

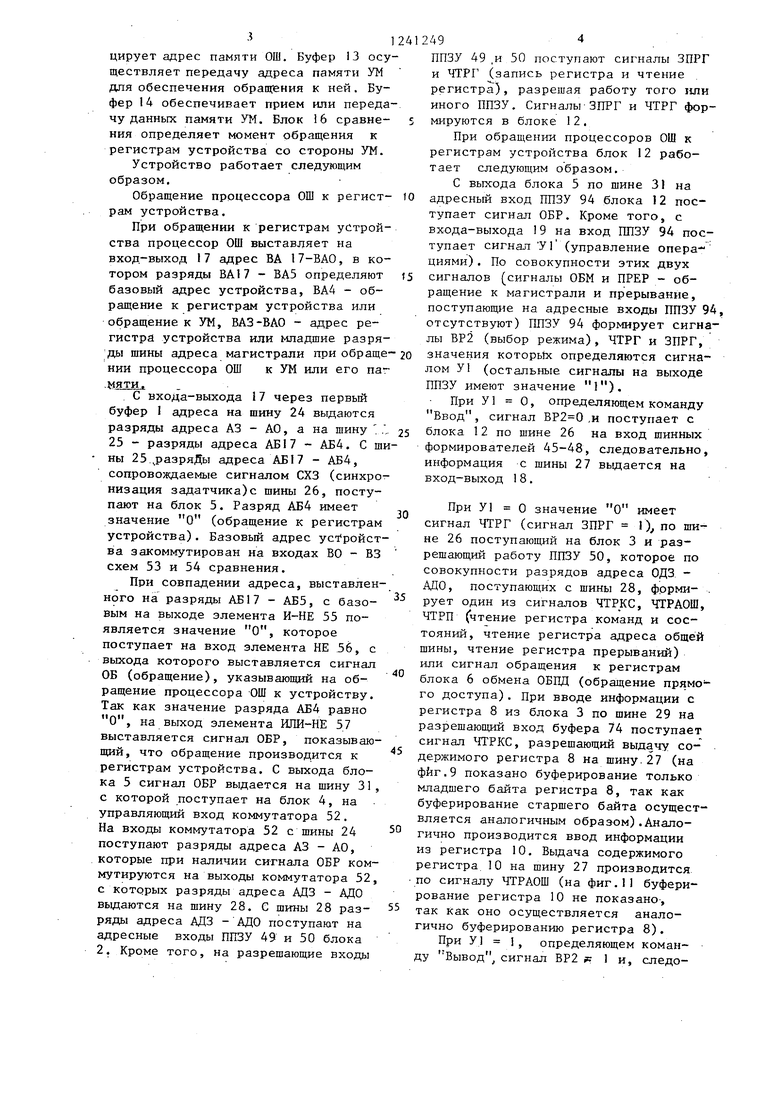

Блок 7 обмена (фиг.7) образуют узел 59 прямого доступа в память, элементы И-НЕ 60 и 61, регистр 62, .элемент И 63, элемент НЕ 64 и ППЗУ 65.

Блок 7 прерываний (фиг,8) состоит из ППЗУ 66, элемента НЕ 67, элемента И-НЕ 68 и элемента И 69.

Регистр. 9 команд и состояний (фиг,.9) включает в себя .триггеры 70-72 у -элемент НЕ 73 и буферы 74 и 75,,

Первый регистр.9 адреса (фиг.10) содержит регистры 76, 77 и элемент НЕ 78, а второй регистр 10 ;. адреса (фиг .М)- счетчики 79 - 83 и элемент НЕ 84.

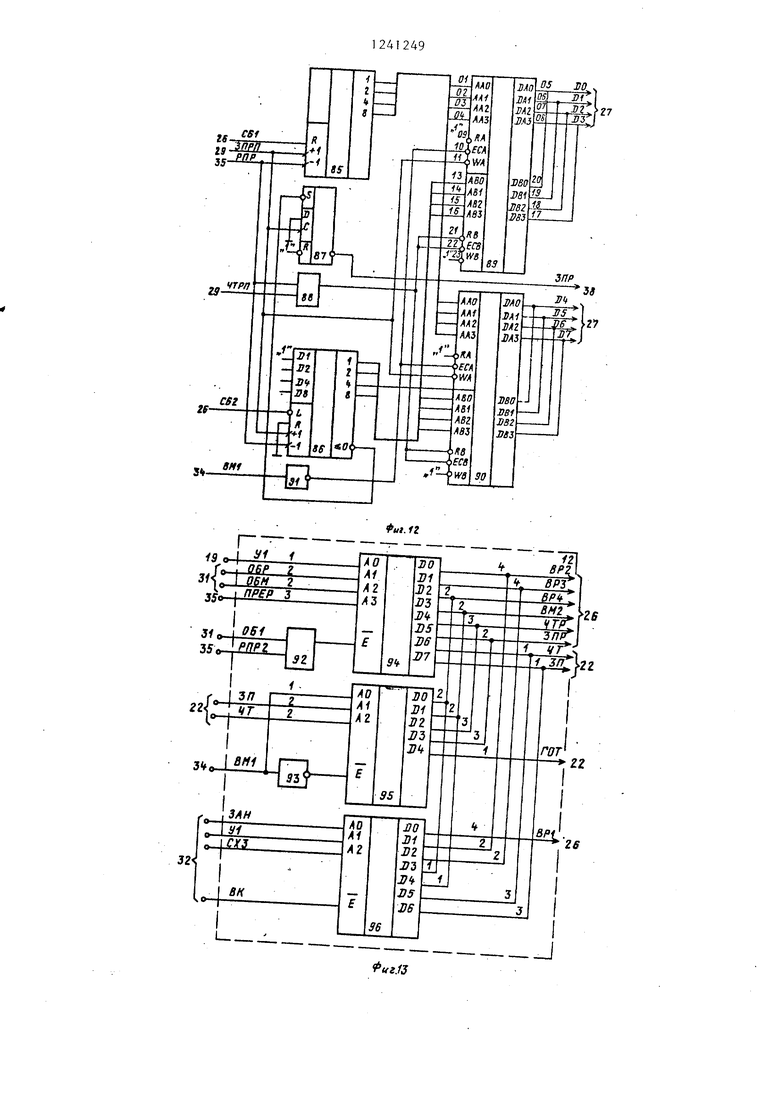

Регистр 11 прерываний (фиг,12) образуют счетчики 85 и 86, триггер 87, элемент И 88, регистры 89 и 90 и элемент 91,

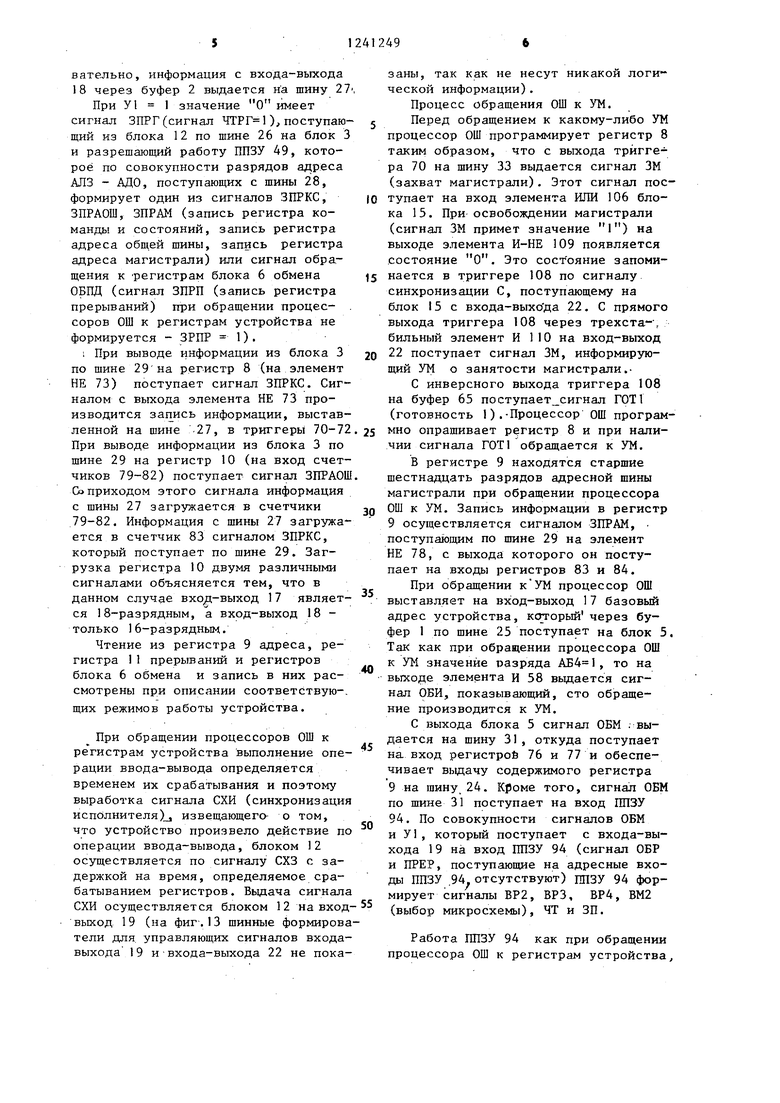

Блок 12 дешифрации управляющих сигналов (фиг,13) состоит из элемента И 92, элемента НЕ 93 и ППЗУ 94-96,

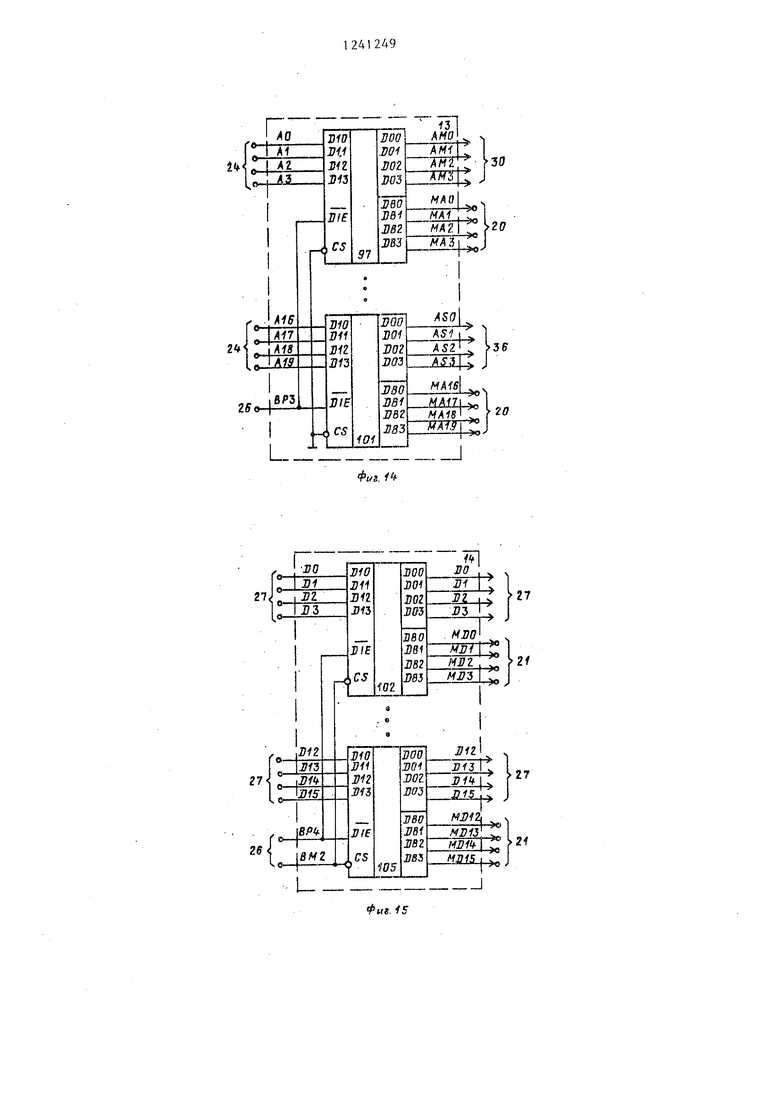

Второй буфер 13 адреса (фиг.14) выполнен в виде формирователей 97 - 101. Второй буфер 14 данных (фиг.15)- в виде шинных формирователей 102-105.

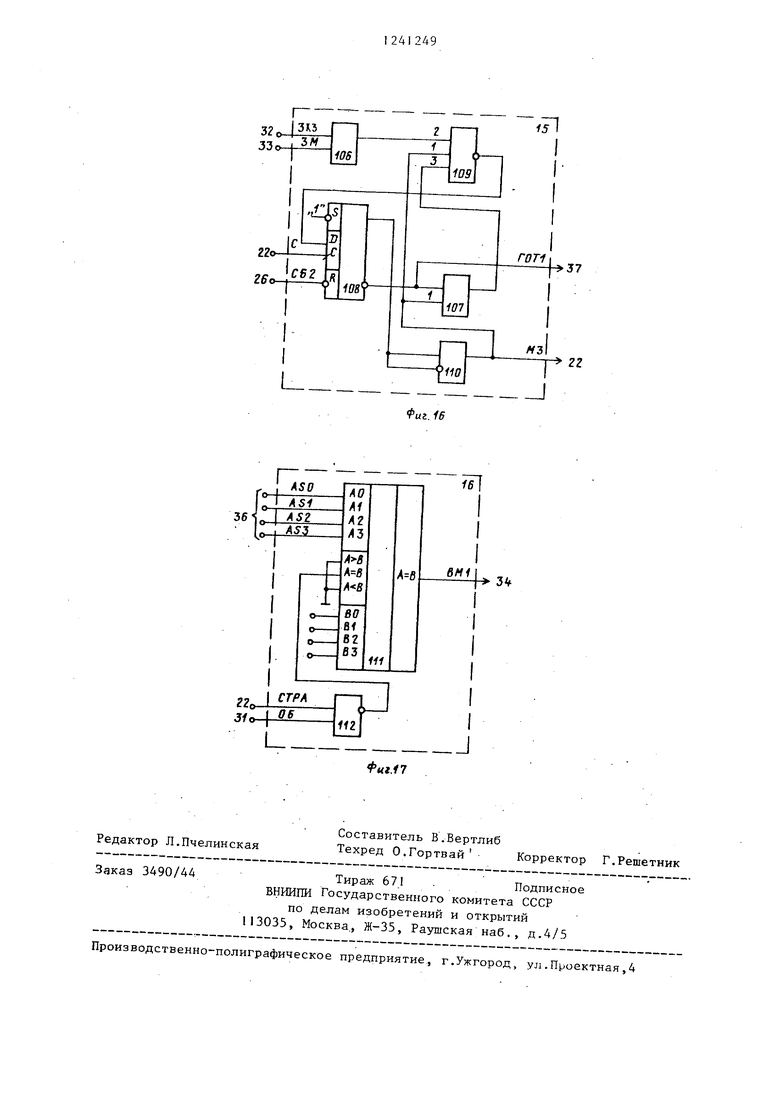

Блок 15 захвата магистрали (фиг,16)содержит элементы ИЛИ 106 и 107, триггер 108, элемент И-НЕ 109 и трехстабильный элемент И 110,

Блок 16 сравнения (фиг,17) образуют схема 111 сравнения и элемент ШШ-НЕ 112.

Буфер 1 осуществляет передачу реса памяти ОШ для обеспечения обр.а- щения к ней. Блок 4 коммутации обеспечивает возможность обращения к регистрам устройства как со стороны процессора ОШ, так и со стороны памяти устройства магистрали (УМ), позволяет программировать регистры устройства и определяет характеристики обмена между памятью ОШ и память УМ. Блок 6 обмена управляет обменом между памятью ОШ и памятью УМ, Регистр 5 адреса храпит и модифи-

цирует адрес памяти ОШ. Буфер 13 осуществляет передачу адреса памяти УМ для обеспечения обращения к ней. Буфер 14 обеспечивает прием или передачу данных памяти УМ. Блок 16 сравне- ния определяет момент обращения к регистрам устройства со стороны УМ.

Устройство работает следующим образом.

Обращение процессора ОШ к регист- рам устройства.

При обращении к регистрам устройства процессор ОШ выставляет на вход-выход 17 адрес ВА 17-ВАО, в котором разряды ВА17 - ВАЗ определяют базовый адрес устройства, ВА4 - обращение к регистрам устройства или обращение к УМ, ВАЗ-ВАО - адрес регистра устройства или младшие разряды щины адреса магистрали при обраще НИИ процессора ОШ к УМ или его паг

.мяти.

С входа-выхода i 7 через первый

буфер I адреса на шину 24 выдаются разряды адреса A3 - АО, а на шину . 25 - разряды адреса АБ17 АБ4. С шины 25.,разряДы адреса АБ17 - АБ4, сопровождаемые сигналом СХЗ (синхронизация задатчика)с шины 26, поступают на блок 5. Разряд АБ4 имеет значение О (обращение к регистрам устройства). Базовый адрес устройства закоммутирован на входах ВО - ВЗ схем 53 и 54 сравнения.

При совпадении адреса, выставленного на разряды АБ17 - АБ5, с базовым на выходе элемента И-НЕ 55 появляется значение О, которое поступает на вход элемента НЕ 56, с вькода которого выставляется сигнал ОБ (обращение), указывающий на обращение процессора ОШ к устройству. Так как значение разряда АБ4 равно О, на выход элемента ШШ-НЕ 57 выставляется сигнал ОБР, показывающий, что обращение производится к регистрам устройства. С выхода блока 5 сигнал ОБР выдается на щину 31, с которой поступает на блок 4, на управляющий вход коммутатора 52. На входы коммутатора 52 с шины 24 поступают разряды адреса A3 - АО, которые при наличии сигнала ОБР коммутируются на выходы коммутатора 52, с которых разряды адреса АДЗ - АДО выдаются на шину 28. С шины 28 раз- ряды адреса АДЗ - АДО поступают на адресные входы ПИЗУ 49 и 50 блока 2. Кроме того, на разрешающие входы

s

fO

t5 0

5

5

0

5

0

5

0

2494 .

ППЗУ 49 ,и 50 поступают сигналы ЗПРГ и ЧТРГ (запись регистра и чтение регистра), разрешая работу того тши иного ППЗУ. Сигналы-ЗПРГ и ЧТРГ формируются в блоке 12.

При обращении процессоров ОШ к регистрам устройства блок 12 работает следующим образом.

С выхода блока 5 по шине 31 на адресный вход ППЗУ 94 блока 12 поступает сигнал ОБР. Кроме того, с входа-выхода 19 на вход ППЗУ 94 поступает сигнал У 1 (управление опера- циями). По совокупности этих двух сигналов (сигналы ОБМ и ПРЕР - обращение к магистрали и прерывание, поступающие на адресные входы ППЗУ 94, отсутствуют) ППЗУ 94 формирует сигналы ВР2 (выбор режима), ЧТРГ и ЗПРГ, значения которьЬс определяются сигналом У1 (остальные сигналы на выходе ППЗУ имеют значение 1).

При У1 0, определяющем команду Ввод, сигнал ,и поступает с блока 12 по шине 26 на вход шинных формирователей 45-48, следовательно, информация с шины 27 выдается на вход-выход 18.

При У1 0 значение О имеет сигнал ЧТРГ (сигнал ЗПРГ I ) по шине 26 поступающий на блок 3 и разрешающий работу ППЗУ 50, которое по совокупности разрядов адреса ОДЗ - АДО, поступающих с шины 28, фррми- . рует один из сигналов ЧТРКС, ЧТРАОШ, ЧТРП (чтение регистра команд и состояний, чтение регистра адреса общей шины, чтение регистра прерываний) или сигнал обращения к регистрам блока 6 обмена ОБПД (обращение прямого доступа). При вводе информации с регистра 8 из блока 3 по шине 29 на разрешающий вход буфера 74 поступает сигнал ЧТРКС, разрешающий выдачу со- держимого регистра 8 на шину.27 (на фиг.9 показано буферирование только младшего байта регистра 8, так как буферирование старшего байта осуществляется аналогичным образом).Аналогично производится ввод информации из регистра 10. Выдача содержимого регистра 10 на шину 27 производится по сигналу ЧТРАОШ (на фиг.11 буферирование регистра 10 не показано, так как оно осуществляется аналогично буферированию регистра 8).

При У1 1, определяющем команду Вывод, сигнал ВР2 1 и, следовательно, информация с входа-выхода 18 через буфер 2 выдается на шину 27

При У1 1 значение О имеет сигнал ЗПРГ (сигнал ), поступаю- щий из блока 12 по шине 26 на блок 3 и разрешающий работу ППЗУ 49, которое по совокупности разрядов адреса АЛЗ - АДО, поступающих с шины 28, формирует один из сигналов ЗПРКС, ЗПРАОШ, ЗПРАМ (запись регистра команды и состояний, запись регистра адреса общей шины, запись регистра адреса магистрали) или сигнал обращения к регистрам блока 6 обмена ОБПД (сигнал ЗПРП (запись регистра прерываний) при обращении процес- соров ОШ к регистрам устройства не формируется - ЗРПР 1).

1 При выводе информации из блока 3 по шине 29 на регистр 8 (на элемент НЕ 73) поступает сигнал ЗПРКС, Сигналом с выхода элемента НЕ 73 производится запись информации, выставленной на шине 27, в триггеры 70-72 При выводе информации из блока 3 по шине 29 на регистр 10 (на вход счетчиков 79-82) поступает сигнал ЗПРАОШ Со приходом этого сигнала информация с шины 27 загружается в счетчики 79-82. Информация с шины 27 загружается в счетчик 83 сигналом ЗПРКС, который поступает по шине 29. Загрузка регистра 10 двумя различными сигналс1ми объясняется тем, что в данном случае вхо/;-выход 17 является 18-разрядным, а вход-выход 18 - только 16-разрядным.

Чтение из регистра 9 адреса, регистра 11 прерываний и регистров блока 6 обмена и запись в них рассмотрены при описании соответствую-, щих режимов работы устройства.

При обращении процессоров ОШ к регистрам устройства выполнение операции ввода-вывода определяется временем их срабатывания и поэтому выработка сигнала СХИ (синхронизация исполнителя)j извещающего- о том, что устройство произвело действие по операции ввода-вывода, блоком 12 осуществляется по сигналу СХЗ с задержкой на время, определяемое срабатыванием регистров. Выдача сигнала СХИ осуществляется блоком 12 на вход выход 19 (на фиг.13 шинные формирователи для управляющих сигналов входа- выхода 19 и входа-выхода 22 не пока

заны, так как не несут никакой логической информации).

Процесс обращения ОШ к УМ.

Перед обращением к какому-либо УМ процессор ОШ программирует регистр 8 таким образом, что с выхода триггера 70 на шину 33 выдается сигнал ЗМ (захват магистрали). Этот сигнал поступает на вход элемента ИЛИ 106 блока 15. При освобождении магистрали (сигнал ЗМ примет значение 1) на выходе элемента И-НЕ 109 появляется состояние О. Это сост ояние запоминается в триггере 108 по сигналу синхронизации С, поступающему на блок 15 с входа-выхо да 22. С прямого выхода триггера 108 через трехста- бильный элемент И 110 на вход-выход 22 поступает сигнал ЗМ, информирующий УМ о занятости магистрали.С инверсного выхода триггера 108 на буфер 65 поступает сигнал ГОТ1 (готовность 1) .-Процессор ОШ программно опрашивает регистр 8 и при наличии сигнала ГОТ 1 обращается к УМ.

В регистре 9 находятся старшие шестнадцать разрядов адресной шины магистрали при обращении процессора ОШ к УМ. Запись информации в регистр 9 осуществляется сигналом ЗПРАМ, . поступа ющим по шине 29 на элемент НЕ 78, с выхода которого он поступает на входы регистров 83 и 84.

При обращении к УМ процессор ОШ выставляет на вход-выход 17 базовый адрес устройства, который через буфер 1 по шине 25 поступает на блок 5. Так как при обращении процессора ОШ к УМ значение разряда , то на выходе элемента И 58 вьщается сигнал ОБИ, показывающий, сто обращение производится к УМ.

С выхода блока 5 сигнал ОБМ - выдается на шину 31, откуда поступает на вход регистроб 76 и 77 и обеспечивает выдачу содержимого регистра 9 на шину 24. Кроме того, сигнал ОБМ по шине 31 поступает на вход ППЗУ 94. По совокупности сигналов ОБМ и У1, который поступает с входа-выхода 19 на вход ППЗУ 94 (сигнал ОБР и ПРЕР, поступ,ающие на адресные входы ППЗУ .94 отсутствуют) ШЗУ 94 формирует сигналы ВР2, ВРЗ, ВР4, ВМ2 (выбор микросхемы), ЧТ и ЗП.

Работа ППЗУ 94 как при обращении процессора ОШ к регистрам устройства

так и при обращении к УМ, разрешает сигналом ОБ (обращение).который поступает по шине 31 на вход элемента И 92, а с выхода - на разрешающий вход ППЗУ 94.

Сигнал ВМ2 при наличии сигнала ОБМ равен О. Из блока 12 сигнал ВМ2 по шине 26 поступает на вход шинных формирователей 102-105, раз- решая их работу.

Сигнал ВРЗ при наличии сигнала ОБМ также равен О. Из блока 12 сигнал ВРЗ по шине 26 поступает на вход шинных формирователей 97-10. При адрес шины 24 вьгдается на вход-выход 20. Значение остальных сигналов определяются значением сигнала У1 .

Сигнал ВР2 формируется так же, как и при обращении процессора ОШ к регистрам устройства. Формирование сигналов ЧТ и ЗП аналогично формированию сигналов ЧТРГ и ЗПРГ соответственно.

При У (команда Ввод) сигнал , а при (команда Вывод) сигнал . Сигнал ВР4 поступает на шину 26 и далее на вход шинных формирователей 102-109. Если сигнал , то информация с входа-выхода 21 выдается на шину 27, при информация i:c тайны 27 выдается на вход-выход 21.

При выполнении команды Ввод блок 12 выставляет на вход-выход 22 сигнал ЧТ. По сигналу ГОТ2 (готовность два), поступающему с входа- выхода 22, блок 12 выдает на вход- выход 19 сигнал СХИ, показывающий, что данные, выставленные УМ, находятся на входе-выходе 18.

При выполнении команды Вывод блок 12 выставляет на вход-выход 22 сигнал ЗП. По сигналу ГОТ2, поступающему с входа-выхода 22, блок 12 формирует сигнал СХИ, показывающий, что УМ осуществило запись информации с входа-выхода 21.

При обращении процессора ОШ к УМ старшие разряды адреса А19 - А4 выда ются с регистра 9, тогда как младшие разряды адреса A3 - АО транслируются непосредственно с входа-выхода 17 через буфер 1 на шину 24 и далее на вход-выход 20. Это позволяет процес- сору .ОШ выставлять шестнадцать последовательных адресов без изменения содержимого регистра 9 адреса.

ю

5

20 25

,,j

5

0

Закончив обращение к УМ, процессор ОШ сбрасывает сигнал ЗМ и блок 15 освобождает магистраль.

При обращении к регистрам устройства со стороны какого-либо УМ, последнее, заняв магистраль,.выставляет на вход-выход 50 разряды адреса МАЗ - МАО .и МА19 - МА16, сопровождая их сигналом СТРА (строб адреса) по входу-выходу 22.

Разряды адреса МА19 - МА16 через буфер 13 выдаются на шину 36 и поступают на входы схемы 111 сравнения. Базовый адрес устройства со стороны магистрйяи закоммутирован на входах схемы 111 сравнения. При совпадении адреса, выставленного на разрядах адреса МА19 - MAI6, с базовым и при отсутствии сигнала ОБ, поступающего по шине 31 на вход элемента ИЛИ-НЕ 112, на выходе схемы 11I сравнения формируется сигнал ВМ1, показывающий, что происходит обращение к регистрам устройства со стороны УМ.Сигнал ВМ1 с выхода блока 16 поступает на входы шинных формирователей 40 - 48, запрещая их работу.

Разряды адреса МАЗ - МАО через буфер 13 выдаются на шину 30, откуда поступают на входы коммутатора 52. Так как сигнал ОБР, поступающий по шине 31, в данный момент отсутствует, то разряды адреса АМЗ - АМО коммутируются на выхо.ды коммутатора 52. С выходов коммутатора 52 разряды адреса АДЗ - АДО выдаются на шину 28.

Процесс обращения к регистрам устройства со стороны УМ аналогичен процессу обращения к ним процессора - ОШ, за исключением работы Отека 12, который в данном случае работает следующим образом.

С блока 16 на блок.12 поступает сигнал BMl, сопровождаемый сигналом ЗП -ИЛИ ЧТ по входу-выходу 22. Эти сигналы поступают на адресные входы ППЗУ 95, а сигнал ВМ1 поступает также и на вход элемента НЕ 93. Сигнал с выхода элемента НЕ 93,разрешает работу ППЗУ 95, которое по -совокупности сигналов ВМ1 и ЗЛ или ВМ и ЧТ формирует,сигналы ВР4, ВМ2, ЗПРГ, ЧТРГ и сигнал ГОТ2.

Сигнал при наличии сигнала ЗП (команда Вывод), а при его отсутствии сигнал . Аналогично формируется сигнал ЧТРГ по сигналу ЧТ (команда Ввод),

При наличии сигнала 31 сигнал . Этот сигнал поступает по шине 26 на вход шинных формирователей 102-105, определяя тем самым направ- ление передачи информации- с входа- выхода 21 на пгану 27. При наличии сигнала ЧТ сигнал , что определяет направление передачи информации с шины 27 на вход-выход 21.

При наличии сигнала BMI сигнал . Этот сигнал по шине 26 поступает на вход шинных формирователей 102-105, разрешая их работу.

Сигнал ГОТ2 формируется по сигна- лу ЗП или ЧТ и выдается с блока 12 на вход-выход 22 с задержкой, определяемой временем срабатывания регистров. При выполнении команды Вывод сигнал ГОТ2 подтверждает, -что инфор -; мация записана в выбранный регистр. При выполнении команды Ввод сигнал ГОТ2 показывает, что на входе-выхоре 21 находится содержимое выбранного 1 егистра.

Режим прерываний.

Работа устройства начинается с записи в регистр 11 байта прерывания. УМ выставляет на разряды адреса МА19 - МА16 базовый адрес устройства со стороны магистрали, а на разряды адреса МАЗ - МАО адрес регистра 11. Блок 16 выдает сигнал BMI, который поступает на вход элемента НЕ 91. . Сигнал с выхода элемента НЕ 91 поступает на вход разрешения регистров .89 и 90, разрешая их работу. Блок 3 выставляет на шину 29 сигнал ЗПРП. Этот сигнал поступает на вход записи регистров 89 и 90 и осуществляет запись информации ,с шины 27. Запись информации рсушествляется по адресу, вьщаваемому счетчиком 85. Содержимое счетчика 85 увеличивается на единицу по концу сигнала ЗПРП, поступающему на выход счетчика 85. По сигналу .ЗПРП увеличивается также и содержимое счетчика 86.

Запрос на прерывание выдается при наличии в регистре 11 хотя бы одного байта прерывания. При записи байта прерывания в регистр 11 по сигналу ЗПРП устанавливается триггер 87, с инверсного выхода которого сигнал ЗПР (запрос прерывания), выдается на блок 7 (на вход элемента И 69). Если прерывание работы процессора ОШ разрешено, то с регистра 8 по шине 33 на второй вход элемента

jO

|5 о 25

Q

5

5

0

И 69 поступает сигнал МП (маскирование прерывания).. Сигнал с выхода элемента И 69 поступает {la вход разрешения ППЗУ 66, разрешая его работу. Хроме того, этот сигнал поступает на вход ППЗУ 66, которое выдает на шину 35 сигнал ЗП (запрос передачи), который через блок 12 выдается на вход-выход 19.

Процессор ОШ выдает на вход-выход 19 сигнал РП (разрешение передачи), который через блок 1.2 поступает на шину 26, откуда попадает на адресный вход ППЗУ 66. По приходу этого сигнала ППЗУ 66 выдает на шину 35 сигнал ПВБ (подтверждение выборки) и сбрасывает сигнал 31. Сигнал ПВБ с шины 35 через блок 12 выдается на вход-выход 19. После того, как ОШ освобождается от предыдущего задат- чика, сбрасывается сигнал ЗАН (шина занята), который с входа-выхода 19 через блок 12 поступает на шину 26, а оттуда на элемент И-НЕ 68, на выходе которого при сбросе сигнала ЗАН устанавливается состояние 1 формируется сигнал ЗН (занято). При выставлении сигнала ЗАН сигнал ЗН сохраняется за счет сигнала с выхода элемента НЕ 67. Этот сигнал поступает на адресный вход ППЗУ 66. ППЗУ 66 выдает на шину 53 сигналы ЗАЕ, ПРЕР, РПР (разрешение прерывания) и сбрасывает сигнал ПВБ. Сигналы ЗАН и ПРЕР по шине 35 через блок 12 поступают на вход-выход 19.

Сигнал РПР с блока 7 по шине 35 поступает на вход элемента И 88. Сигнал с выхода элемента И 88 поступает на входы чтения и разрешения регистров 89 и 90, разрешая выдачу байта прерывания на шину 27. Выдача байта прерывания осуществляется по адресу, выдаваемому счетчиком 86 . Содержимое счетчика 86 всегда на единицу меньше содержимого счетчика 85. С шины 27 байт прерывания поступает через буфер 2 на вход-выход 18.

Процессор ОШ, получив байт прерывания, выставляет на вход-выход 19 сигнал. СХИ, которьш через блок 12 по шине 26 поступает на адресный вход ППЗУ 66 . По этому сигналу ППЗУ 66 сбрасывает сигналы ПРЕР, ЗАН и РПР и возвращается в исходное состояние .

После вьщачи одного байта преры- 1вания содержимое счетчиков 85 и 86

уменьшается на единицу. При выдаче последнего байта прерывания из регистра I 1 сигналом переноса с -выхода счетчика 86 сбрасывается триггер 87 и снимается сигнал ЗПР.

Обмен блоками информации между памятью ОШ и памятью УМ.

Перед началом обмена информацией необходимо запрограммировать регист- ры блока 6 (регистры узла 59).Программирование регистров возможно как со стороны процессора ОШ, так и со стороны УМ. При обращении к регистрам блока 6 по шине 29 выдается

сигнал ОБИД, который, поступая на вход узла 59, разрешает программирование ее внутренних регистров (на фиг,7 показана только часть узла 59 обрабатывающая младший байт, посколь ку другая часть подключается к входным управляющим сигнала аналогичным образом, а на ее входы-выходы подаются разряды Д8 - Д15 старшего байта с шины 27). Кроме того, из буфера 51 блока 3 по шине 24 на адресные входы-выходы узла 59 поступают разряды адреса A3 - АО, необходимые для дешифрации его регистров. Запись в выбранный регистр производится по сигналу ЗПРГ, поступающему по шине 26 из блока 12. Чтение выбранного регистра осуществляется сигналом ЧТРГ, поступающему по шине 26 из блока 12.

Обмен начинается с программирования регистра 8 таким образом, что с выхода триггера 72 выдается сигнал НПДП (начало прямого доступа). Этот сигнал с регистра 8 по шине 33 поступает на вход узла 59, который выставляет сигнал ЗХ (захват) на шину 32. Этот сигнал поступает на вход элемента ИЛИ 106 блока 15, кото рый при наличии этого сигнала осуществляет захват магистрали и сообщает об этом блоку 6 сигналом ГОТ, пос- тупаюшлй йа вход узла 59. На выходе последнего формируется сигнал, разрешающий работу ППЗУ 65. Сигнал ГОТ1 поступает также и на адресный вход ШТЗУ 65, которое по приходу этого сигнала выставляет на шину-32 сигнал ЗПД (запрос прямого доступа). Сигнал ЗПД с шины 32 через блок 12 выдается на вход-выход 19. Процессор ОШ, приняв этот сигнал, выдает сигнал РПД (разрешение прямого доступа), которы

Ю 15

20 5 0 5

5

0

5

с входа-выхода I9 через блок 12 по шине 26 поступает на блок 6 на адресный вход ППЗУ 65, которое выдает по этому сигналу на шину 32 сигнал ПВБ и снимает сигнал ЗПД.

Сигнал ПВБ через блок 12 выдается на вход-выход 19. После того, как ОШ освобождается от предыдущего за- датчика, сбрасывается сигнал ЗАН, который с входа-выхода 19 через блок

12поступает на шину 26. С шины 26 сигнал ЗАВ поступает на блок 7, где формируется сигнал 31 и поступает

на адресный вход ППЗУ 65, после чего ППЗУ 65 выдает на шину 32 сигнал ЗАН, который через блок 12 вьщается на вход-выход 19..

Блок 12 в этом режиме работает следующим образом.

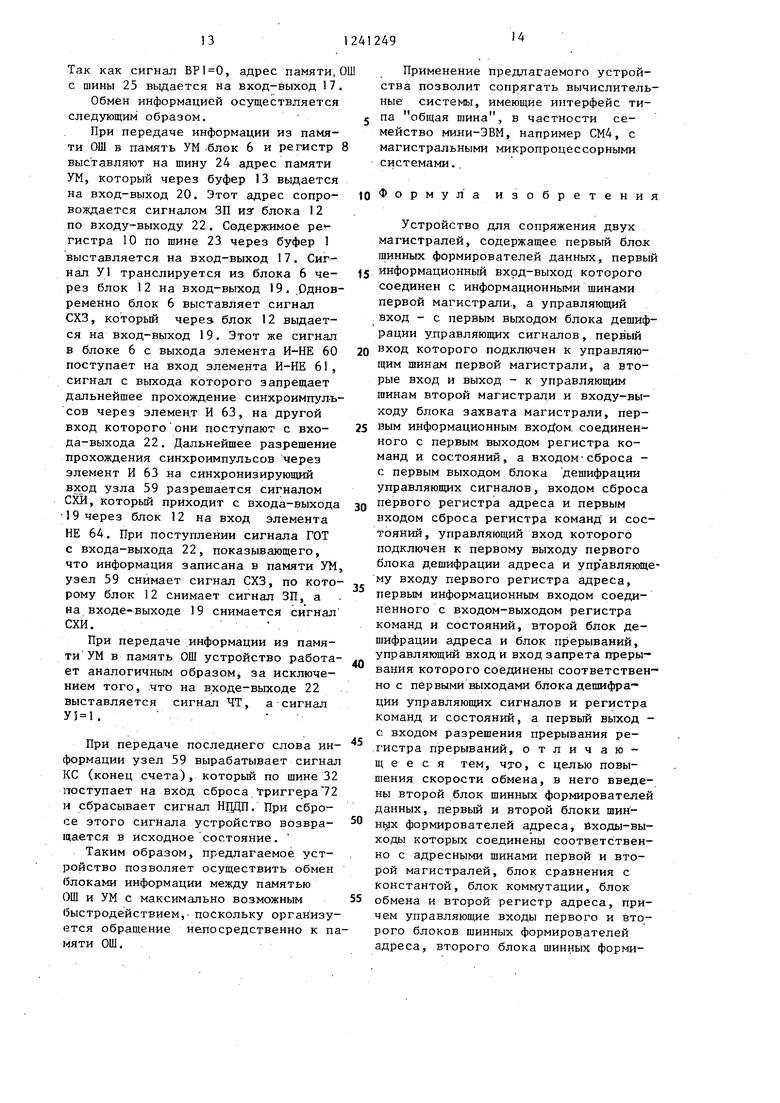

С блока 6 по шине 32 поступают сигналы ЗАН, СХЗ и У1 (на входы ППЗУ 96)и сигнал ВК (выбор кристалла) на разрешающий вход ППЗУ 96. При наличии этих сигналов блок 12 формирует сигналы ВР1 - ВР4, ВМ2, ЧТ и ЗП. Сигналы ВМ2, ВР1 и ВРЗ имеют значение О. Значение остальных сигналов определяется значением сигнала У1 . Если сиг.нал У (передача информации из памяти ОШ в память УМ), то сигнал ВР (информация с входа-выхода 18 через буфер 2 выдается на шину 27), а сигнал (информация с шины 27 через буфер 14 выдается на вход-выход 21). При У 1 1 (передача информации из памяти УМ в память ОШ) сигнал (информация с шины 27 через буфер 2 выдается на вход-выход 18) j а сигнал (информация с входа-выхода 21 через буфер 14 выдается на шину 27). Блок 6 вьщает адрес памяти УН на шину 24, причем разряды адреса А7 - АО выдаются из узла 59, а разряды А15 - А8 - из регистра 62. Разряды адреса А19 - А16 находятся в регистре 8. По сигналу ВК из блока 6 буфер 75 выдает содержимое триггера 71 на шину 24. Так как сигнал , то адрес с шины 24 вьщается через буфер

13на вход-выход 20. Адрес памяти ОШ выдается из регистра 10 на шину 23 по сигналу СХЗ, поступающему с выхода элемента

И-НЕ 66 по шине 32. Кроме того, сигналом с выхода элемента НЕ 84, на вход которого поступает сигнал СХЗ, увеличивается содержимое регистра 10.

Так как сигнал , адрес памяти,О с шины 25 выдается на вход-выход 17.

Обмен информацией осуществляется следующим образом.

При передаче информации из памяти ОШ в память УМ .блок 6 и регистр выставляют на шину 24 адрес памяти УМ, который через буфер 13 выдается на вход-выход 20. Этот адрес сопро- вождается сигналом ЗП изг блока 12 по входу-выходу 22. Содержимое гистра 10 по шине 23 через буфер 1 выставляется на вход-выход 17. Сигнал У1 транслируется из блока 6 че- рез блок 12 на вход-выход 19. .Одновременно блок 6 выставляет сигнал СХЗ, который через блок 12 выдается на вход-выход 19. Этот же сигнал в блоке 6 с выхода элемента И-НЕ 60 поступает на вход элемента И-НЕ 61, сигнал с выхода которого запрещает дальнейшее прохождение синхроимпульсов через элемент И 63, на другой вход которого они поступают с вхо- да-выхода 22. Дальнейшее разрешение прохождения синхроимпульсов через элемент И 63 на синхронизирующий вход узла 59 разрешается сигналом СХИ, который приходит с входа-выхода 1 9 через блок 12 на вход элемента НЕ 64. При поступлении сигнала ГОТ с входа-выхода 22, показывающего, что информация записана в памяти УМ узел 59 снимает сигнал СХЗ, по кото- рому блок 12 снимает сигнал ЗП, а на входе-выходе 19 снимается сигнал СХИ. . . .

При передаче информации из памяти УМ в память ОШ устройство работа- ет аналогичным образом, за исключением того, что на входе-выходе 22 выставляется сигнал ЧТ, а сигнал .

При передаче последнего слова ин- (1юрмации узел 59 вырабатывает сигнал КС (конец счета), который по шине 32 поступает на вход сброса /триггера 72 н сбрасывает сигнал НГЩП. При сбросе этого сигнала устройство возвра- щается в исходное состояние.

Таким образом, предлагаемое устройство позволяет осуществить обмен блоками информации между памятью ОШ и УМ с максимально возможным быстродействием,- поскольку организуется обращение непосредственно к памяти ОШ.

Применение предлагаемого устройства позволит сопрягать вычислительные системы, имеющие интерфейс типа общая шина, в частности семейство мини-ЭВМ, например СМ4, с магистральными микропроцессорными системами..

Формула изобретения

Устройство для сопряжения двух магистралей, содержащее первый блок шинных формирователей данных, первый информационный вход-выход которого соединен с информационными шинами первой магистраг и,, а управляющий вход - с первым выходом блока дешифрации управляющих сигналов, первый вход которого подключен к управляющим шинам первой магистрали, а вторые вход и выход - к управляющим шинам второй магистрали и входу-выходу блока захвата магистрали, первым информационным вхоДом. соединенного с первым выходом регистра команд и состояний, а входом-сброса - с первым выходом: блока дешифрации управляющих сигналов, входом сброса первого регистра адреса и первым входом сброса регистра команд и состояний, управляющий вход которого подключен к первому выходу первого блока дешифрации адреса и упр авлякяце му входу первого регистра адреса, первым информационным входом соединенного с входом-выходом регистра команд и состояний, второй блок дешифрации адреса и блок прерываний, управляющий входи вход запрета прерывания которого соединены соответственно с первыми выходами блока дешифрации управляющих сигналов и регистра команд и состояний, а первый выход - с входом разрешения прерывания ре- -гистра прерываний, отличающееся тем, что, с целью повышения скорости обмена, в него введены второй блок шинных формирователей данных, первый и второй блоки шин- Hhjx формирователей адреса, бходы-вы- ходы которых соединены соответственно с адресными шинами первой и второй магистралей, блок сравнения с константой, блок коммутации, блок обмена и второй регистр адреса, причем управляющие входы первого и второго блоков шинных формирователей адреса, второго блока шинных формирова.телеи данных и второго регистра адреса соединены с первым выходом блока дешифрации управляющих сигналов, первыми входами первого и втор го дешифраторов адреса, первым входом режима блока обмена и входом сброса регистра прерываний, второй информационный вход-выход первого блока шинных формирователей данных соединен с информационным входом- выходом блока обмена, информационными входами второго и первого регистров адреса, информационным входом- выходом регистра прерываний и пер- вым информационным входом-выходом второго блока шинных формирователей данных, второй информационный вход- выход которого соединен с информационными шинами второй магистрали, информационный вход первого блока шинных формирователей адреса соединен с выходом второго регистра адреса, первый выход первого блока шинных формирователей адреса, вых од первого регистра адреса и вторые выходы первого блока дешифрации адреса и регистра команд и состояний подключены соответственно к информационному входу второг о блока шинных формирователей адреса, первому информационному входу блока коммутации и ад-ресному входу-выходу блока обмена, выход которого соединен с вт рым входом сброса регистра команд и состояний, синхронизирующим входом второго регистра адреса, вторым инфомационным входом блока захвата магисрали и третьим входом блока дешифрации управляющих сигналов, четвертым и пятым входами подключе,нного соответственно к первому выходу блока прерываний и к выходам блока сравнения с константой и входам разрешения регистра прерываний, первого блока шинных формирователей данных и первого блока шинных формирователей адреса, второй выход которого соединен с вторым входом второго блока дешифрации адреса, выходом подключенного к управляющему входу блока коммутации, выход и второй информационный вход которого сое- динены соответственно с вторым входом первого блока дешифрации адреса и первым выходом второго блока шинных формирователей адреса, вторым выходом подключенного к информационному входу блока сравнения

ю 5 2о 5 5

0

5

0

5

0

с константой, синхронизирующий вход которого соединен с управляющими шинами второй магистрали, а вход разрешения - с выходом второго блока дешифрации адреса, шестым входом блока дешифрации управляющих сигналов и разрешающим входом первого регистра адреса, первый выход первого блока дешифрации адреса соединен с информационным входом второго регистра адреса, входом разрешения настройки блока обмена и управляющим входом регистра прерываний, выходом подключенного к входу запроса прерывания блока прерываний, второй выход которого соединен с вторым входом режима блока обмена, вход пуска и первый вход синхрони- зации которого подключены соответственно к первому выходу регистра команд и состояний и управляющим шинам второй магистрали, а второй вход синхронизации - к выходу блока захвата магистрали, информационному входу регистра команд и состояний, причем блок обмена содержит узел прямого доступа в память, два элемента И-НЕ, регистр,, блок постоянной памяти, элемент И и элемент НЕ, причем информационный вход-выход узла прямого доступа в память соединен с информационным входом-выхо- дом блока обмена и информационным входом регистра, а адресный вход- выход - с адресным входом-выходом блока обмена и выходом регистра, выход первого элемента И-НЕ, группа выходов блока постоянной памяти и группа синхронизирующих выходов узла прямого доступа в память образуют выход блока обмена, нулевой, первый и второй разряды адресного входа блока постоянной памяти подключены соответственно к второму синхронизирующему и второму и первому входам режима блока обмена, а третий и четвертый разряды : адресного входа - к группе выходов блока постоянной памяти, первый и второй входы первого элемента И-НЕ подключены к выходам сигнала чтения и записи узла прямого доступа в память, вход сигнала подтверждения захвата, тактовый вход, входы разрешения и запроса прямого доступа которого соединены соответственно с вторым синхронизирующим входом блока обмена,- выходом элемента И и входами разрешения

настройки и пуска блока обмена, входы сброса, первый и второй синхронизирующие входы регистра соединены соответственно с первым входом режима, выходом первого элемента И-НЕ и выходом сигнала синхронизации адреса узла прямого доступа в память, вход сброса и входы чтения и записи регистров которого подключены к первому входу режима блока обмена, а вход

готовности - к первому синхронизирующему входу блока обмена, первый вход второго элемента И-НЕ соединен с выходом первого элемента И-НЕ, второй вход через элемент НЕ - с первым входом режима блока обмена, а выход - с первым входом элемента И, вторым входом подключенного к первому синхронизирующему входу блока обмена.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Устройство для сопряжения ЭВМ с магистралью внешних устройств | 1985 |

|

SU1408440A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения вычислительной машины с периферийными устройствами | 1981 |

|

SU960787A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Устройство для сопряжения абонента с каналом связи | 1987 |

|

SU1508225A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к области вычислительной техники и может быть использовано для сопряжения вычислительных систем, имеющих интерфейс типа общая шина с магистральной микропроцессорной .системой. Целью изобретения является повышение скорости обмена. Для достижения поставленной цели в устройство,содержащее первый блок шинных формирователей данных, блок прерываний, дешифратор управляющих сигналов, блок захвата магистрали, регистр прерываний, первый регистр адреса, два блока дешифрации адреса и.регистр команд и состояний, введены . второй блок шинных формирователей данных,два блока шинных формирователей адреса, блок коммутации, второй регистр адреса, блок обмена и блок сравнения с константой. 1 п. 3. ф-лы, 17 ил, с € (/) С 0 1 5 СО

Фкг. 2

28

Фиг. 5

Z7

320

Z

Фиг. 9

Фчг. If

гв.

Фи1. f г

fi.fS

Фиг. IS

Г

Редактор Л.Пчелинская

Заказ 3490/44

Тираж 671 . Подписное БНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва., Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

71

Составитель В.Бертлиб

Техред О.Гортвай Корректор Г.Решетник

| Устройство для сопряжения | 1977 |

|

SU648974A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-30—Публикация

1984-12-10—Подача