i4

О 00

О

со

Изобретение относится к области вычислительной техники, а именно к аналоговым и гибридным вычислительным устройствам, предназначенным для исследования нелинейных динамических объектов с использованием аппарата дифференциальных преобразований,и может быть использовано также для запоминания функций, заданных реальными физическими сигналами, преобразования масштаба аргумента, введения регулируемого запаздывания, для сжатия информации в информационно-измерительных системах.

Целью изобретения является повышение точности решения.

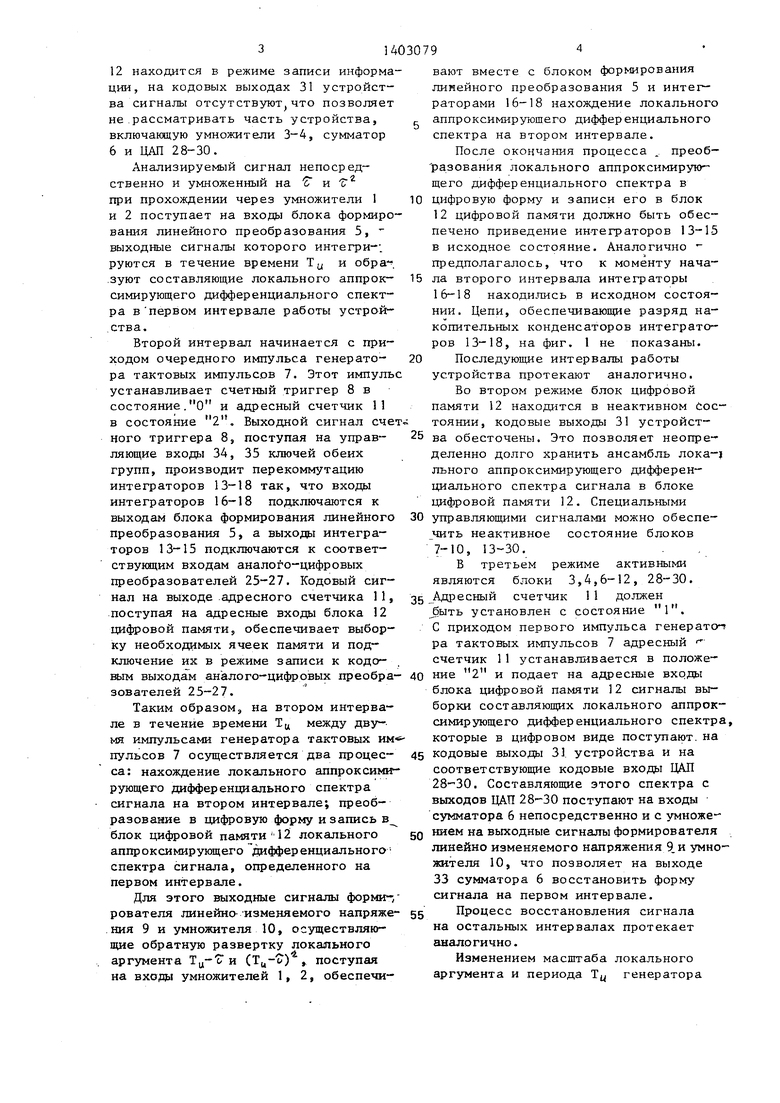

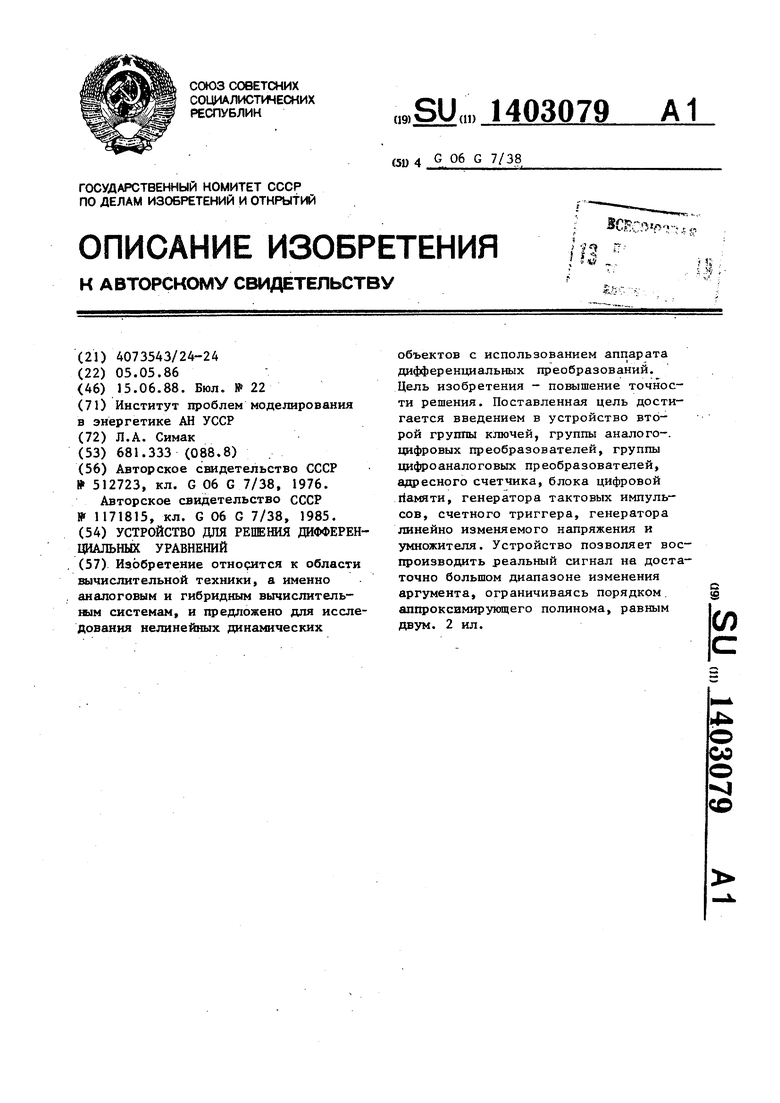

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - пример определения локальных аппроксимирую- щих дифференциальных спектров для функции

x(t) i-e

-t/г

cos---t

I и временные диаграмьы .сигналов.

I Устройство (фиг. 1) состоит из i I

I следующих, блоков: первый и второй ум- Множители первой группы 1, 2, первый iH второй умножители второй группы

3, 4, блок 5 формирования линейного :преобразователя, сумматор 6, генера- тор 7 тактовых импульсов счетный Триггер 8, формирователь 9 линейно ;изменяемого напряжения, умножитель 110, адресный счетчик П, блок 2 цифровой памяти, интеграторы 13 - 15 первой группы, интеграторы 16 - 18 второй группы, ключи первой группы 19 - 21, ключи второй группы 22 - 24 группа аналого-цифровых преобразователей 25 - 27, группа цифроаналоговы преобразователей (ЦАП) 28 - 30, кодовые выходы 31 устройства, вход 32 устройства, выход 33 сумматора, управляющие входа 34, 35 ключей. Устройство работает следующим образом.

Выполняя свои функции, устройство может находиться в одном из трех режимов.

Режим определения локальных ап- проксимирукяцих дифференциальных спекров сигнала, действующего на входе устройства. Этот же режим исполь- зуется для записи аналогового сигнала как. функции времени.

Режим хранения массива локальных аппроксимирующих дифференицальных

o

0

5

0

5 0 5

0

5

спектров. В этом же режиме осуществляется экономное хранение анализируемого сигнала в спектральном виде.

Режим восстановления сигнала. Этот же режим является режимом воспроизведения записанной функции, при котором возможно изменение масштаба аргумента и введение запаздывания,

В первом режиме устройство позво- ляет определить ансамбль локальных аппроксимирующих дифференциальных спектров анализируемого сигнала, действующего на входе 32 устройства. Максимально допустимый диапазон изменения аргумента анализируемого сигнала определяется частотой генератора тактовых импульсов 7, максимальной емкостью адресного счетчика 11. Этот максимальный диапазон может быть разбит на ряд одинаковых временных интервалов, равных периоду импульсов генератора 7. Внутри каждого интервала может быть введен локальный временной аргумент б ,который изменяется таким образом в пределах . С приходом первого импульса генератора тактовых импульсов 7 счетный триггер 8 и адресный счетчик 11 устанавливаются в положение 1. . Единичный сигнал счетного триггера 8, поступая на управляющие входы 34 и 35 ключей обеих групп, подключает . входы интеграторов 13 - 15 к соответ ствующим выходам блока формирования линейного преобразования 5. Этим же сигналом выходы интеграторов 16 - 18 подключаются к соответствующим . входам аналого-цифровых преобразователей 25-27. Входы интеграторов -. 16-18 и выходы интеграторов 13-15, соединенные с нормально замкнутыми полюсами соответствующих ключей , 19-24 обеих групп, отключены. Первый интервал работы устройства и части функционирования аналого-цифровых преобразователей является неинформативным, так как сигналы на выходах интеграторов 16-18 не имеют отношения к анализируемому сигналу. Развертка локального аргумента осу ще.ствляется формирователем линейно изменяемого напряжения 9. Сигнал, : пропорциональный Г , с выхода формирователя 9 и сигнал, пропорциональный о , с .выхода умножителя 10 по с-, тупают на вторые входы умножителей 1-4. Поскольку блок цифровой памяти

12 находится в режиме записи информации, на кодовых выходах 31 устройства сигналы отсутствуют что позволяет не .рассматривать часть устройства, включающую умножители 3-4, сумматор 6 и ЦАП 28-30.

Анализируемый сигнал непосредственно и умноженный на Г и Т при прохождении через умножители 1 и 2 поступает на входы блока формирования линейного преобразования 5, выходные сигналы которого интегри-. руются в течение времени Т ц и . ,зуют составляющие локального аппроксимирующего дифференциального спектра в первом интервале работы устрой- .ства.

Второй интервал начинается с приходом очередного импульса генератора тактовых импульсов 7. Этот импуль устанавливает счетный триггер 8 в состояние.О и адресный счетчик 11 в состояние 2, Выходной сигнал сченого триггера 8, поступая на управляющие входы 34, 35 ключей обеих групп, производит перекоммутацию интеграторов 13-18 так, что входы интеграторов 16-18 подключаются к выходам блока формирования линейного преобразования 5, а выходы интеграторов 13-15 подключаются к соответ- ствунщим входам аналого-цифровых преобразователей 25-27. Кодовый сигвают вместе с блоком формирования линейного преобразования 5 и интеграторами 16-18 нахождение локального

аппроксимируюшего дифференциального спектра на втором интервале.

После окончания процесса , преоб- разования локального аппроксимирую щего дифференциального спектра в

цифровую форму и записи его в блок 12 цифровой памяти должно быть обеспечено приведение интеграторов 13-15 в исходное состояние. Аналогично предполагалось, что к моменту начала второго интервала интеграторы

16-18 находились в исходном состоянии. Цепи, обеспечивающие разряд накопительных конденсаторов интеграторов 13-18, на фиг. 1 не показаны.

Последующие интервалы работы устройства протекают аналогично. Во втором режиме блок цифровой памяти 12 находится в неактивном Состоянии, кодовые выходы 31 устройства обесточены. Это позволяет неопределенно долго хранить ансамбль лока-j льного аппроксимирующего дифференциального спектра сигнала в блоке цифровой памяти 12. Специальными

управляющими сигналами можно обеспечить неактивное состояние блоков 7-10, 13-30.

В третьем режиме активными являются блоки 3,4,6-12, 28-30.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Устройство для формирования векторов на экране электронно-лучевой трубки | 1985 |

|

SU1251161A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1278886A1 |

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| Гибридный функциональный преобразователь | 1982 |

|

SU1076918A1 |

| Устройство для измерения динамических характеристик | 1983 |

|

SU1168902A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

Изобретение отно ;штся к области вычислительной техники, а именно аналоговым и гибридным вычислительным системам, и предложено для исследования нелинейных динамических объектов с использованием аппарата дифференциальных преобразований. Цель изобретения - повышение точности решения. Поставленная цель достигается введением в устройство второй группы ключей, группы аналого-. цифровых преобразователей, группы цифроаналоговых преобразователей, адресного счетчика, блока цифровой Памяти, генератора тактовых импульсов, счетного триггера, генератора линейно изменяемого напряжения и умножителя. Устройство позволяет воспроизводить реальный сигнал на достаточно большом диапазоне изменения аргумента, ограничиваясь порядком, аппроксимирующего полинома, равным двум. 2 ил. с S (Л

нал на выходе .адресного счетчика 11, 35-АВД ™ счетчик II должен

поступая на адресные входы блока 12 цифровой памяти, обеспечивает выборку необходимых ячеек памяти и подключение их в режиме записи к кодобыть установлен с состояние 1. С приходом первого импульса генерат ра тактовых импульсов 7 адресный счетчик 11 устанавливается в положе

вьш выходам аналого-цифровых преобра- 40 ние 2 и подает на адресные входы

зователей 25-27. Таким образом.

на втором интервале в течение времени Тц между дву-

блока цифровой памяти 12 сигналы выборки составляющих локального аппроксимирующего дифференциального спектра, мя импульсами генератора тактовых которые в цифровом виде поступают, на пульсов 7 осуществляется два процес- 45 кодовые выходы 31 устройства и на са: нахождение локального аппроксими- соответствующие кодовые входы ДАЛ рующего дифференциального спектра 28-30. Составляющие этого спектра с сигнала на втором интервале; преоб- выходов ЦАП 28-30 поступают на входы

сумматора 6 непосредственно и с умноже gQ нием на выходные сигналы формирователя линейно изменяемого напряжения 9. и умножителя 10, что позволяет на выходе 33 сумматора 6 восстановить форму сигнала на первом интервале.

разование в цифровую форму и запись в блок цифровой памяти 121 локального аппроксимирующего дифференциального- спектра сигнала, определенного на первом интервале.

Для этого выходные сигналы форми-/ рователя линейно изменяемого напряже- ния 9 и умножителя 10, осуществляющие обратную развертку локального аргумента Тц-Т и (Тц- Е ) , поступая на входы умножителей 1, 2, обеспечи

счетчик II должен

быть установлен с состояние 1. С приходом первого импульса генерато- ра тактовых импульсов 7 адресный счетчик 11 устанавливается в положе-

блока цифровой памяти 12 сигналы выборки составляющих локального аппроксимирующего дифференциального спектра, которые в цифровом виде поступают, на 5 кодовые выходы 31 устройства и на соответствующие кодовые входы ДАЛ 28-30. Составляющие этого спектра с выходов ЦАП 28-30 поступают на входы

5

сумматора 6 непосредственно и с умноже Q нием на выходные сигналы формирователя линейно изменяемого напряжения 9. и умножителя 10, что позволяет на выходе 33 сумматора 6 восстановить форму сигнала на первом интервале.

Процесс восстановления сигнала на остальных интервалах протекает аналогично.

Изменением масштаба локального аргумента и периода Ту генератора

5

тактовых импульсов 7 можно обеспечить масштабное преобразование независимой переменной.

Предварительной установкой адрес- ного счетчика 11 может быть выпол- рена селекция отдельных участков ана зируемого сигнала,

: в примере устройства (фиг. 2) ука |занные режи1« 1 реализуются аиалогич- о.

I На фиг 2 приведен пример работы |устройства для случая воздействия

i/ N . --Цг -г

(сигнала x(t)-l-e cos---t на

зходе 32 устройства. В этом примере шличество интервалов . На -1иг. 2 вместе с графиком входного сигнала показаны получаемые локаль- 1Ые аппроксимирующие дифференциаль- яые спектры. Временные диаграммы, триведенные на фиг. 2, отражают :игналы на выходах генератора тактовых импульсов 7, сигнал типа меандра на выходе счетного триггера 3, выходной сигнал формирователя ли- :1ейно-изменяемого напряжения 9 и :зыходной сигнал умножителя 10, соот- Цтствующий возведенному в квадрат |а1гналу 9.

I Ансамбль локальных аппроксимирукг- 1Ц1х,дифференицальных спектров, при- еденный в нижней части-фиг. 2, сме- iif(eH на величину диапазона изменения |1окального аргумента Тц 1 и отра- ает факт запаздывания, с которым Образуются составлякяцие указанного Спектра, формула изобретени

Устройство для решения дифферен- Циальных уравнений, содержащее пер- 8ый и второй умножители первой групп Первый и второй умножители второй группы, сумматор, блок формирования, ;вьтолненный в виде матрицы пхп масштабных резисторов линейного преобразования, две группы из трех интеграторов в каждой и первую группу из Трех ключей, первый и второй входы блока формирования линейного преобразования соединены с выходами соответс 9енно первого и второго умножителей Первой группу,.первые входы которых объединены собой и являются Иходом устройства, вторые входы пер- .його и второго умножителей первой 1т)уппы подключены к первым входам Соответственно первого и второго умн

жителей второй группы, выходы которых подключены соответственно к первому и второму входам сумматора, выход которого является выходом ройства, отличающееся тем, что, с целью повышения точности решения, в устройство введены; вторая группа, из трех ключей, группа из трех аналого-цифровых преобразователей, группа из трех цифроаналоговых преобразователей, адресный счетчик, блок цифровой памяти, генератор тактовых импульсов, счетный триггер, ге- ,

нератор линейно изменяемого напряжения и умножитель, первый и второй входа которого объединены между со-, бой и подключены к первому входу перво-. го умножителя второй группы и выходу генератора линейно изменяемого напряжения, вход которого соединен с управляющими входами ключей первой и второй групп, синхронизирующим входом блока цифровой памяти и выходом счетного триггера, вход которого подключен к выходу генератора такто-, И.1Х импульсов и счетному входу адресного счетчика, выходы которого соединены с адресным входом блока цифровой памяти, входы данных которого пoдкJГoчeны к выходам аналого-цифрою вых преобразователей группы, информационные входы которых соединены с пе- реключакицими контактами соответствующих ключей второй группы, выходы блока цифровой памяти являются кодо- Н51МИ выходами устройства и подключены к информационным входам первого, второго и третьего цифроаналоговых

преобразователей группы, выходы которых соединены соответственно с трё .- тьим входом сумматора, вторыми входами первого и второго умножителей

второй группы, выходы блока формирования линейного преобразования подключены к переключающим контактам соответствующих ключей первой группы,, первые замыкаюш;ие контакты которых через соответствукнцие интеграторы

первой группы соединены с первыми замыкающими контактами соответствующих ключей второй группы, вторые замыкающие контакты которых через соответствующие интеграторы второй

группы подключены к вторым замыкаю - щим контактам соответствующих ключей первой группы, третий вход блока формирования линейного преобразования соединен с входом устройства.

а

)((t)

)((t))

Ю

| Устройство для накопления аналоговой информации | 1968 |

|

SU512723A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения дифференциальных уравнений | 1983 |

|

SU1171815A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-06-15—Публикация

1986-05-05—Подача