(5) ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интегрирования | 1979 |

|

SU822194A1 |

| Цифровой интегратор | 1988 |

|

SU1580359A1 |

| Устройство для решения линейных дифференциальных уравнений | 1987 |

|

SU1476486A1 |

| Устройство для вычисления кратного интеграла | 1989 |

|

SU1647559A1 |

| Детерминированно-вероятностный интегратор | 1979 |

|

SU857990A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1056227A1 |

| Устройство для интегрирования функций | 1982 |

|

SU1070570A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

1

Изобретение относится к вычислительной технике и быть использовано при построении специализированных вычислительных машин для решения обыкновенных дифференциальных уравнений.

Известны устройства, осуществляющие операцию интегрирования в приращениях, содержащие, как правило, блоки для хранения значений подын-тегральной функции, хранения полученной суммы и позволяющие прибавлять или вычитать из, полученной, суммы новое значение функции 03 и t2l,

Методологическим недостатком данного класса интегрирукичих устройств является определение интеграла в приращениях, что требует для осуществления одного шага вычисления двух этапов. Кроме того, они имеют недостаточную точность вычислений, так как в них реализуется интегрирование по методам прямоугольников и трапеций.

В предлагаемом изобретении интегрирование по методам прямоугольников и трапеций реализуется при использовании интерполяционных- полиномов нулевой и первой степени, т.е. при осуществлении интегрирования заведомо с самой низкой точностью.

Наиболее близким по принципу действия и технической сущности к предлагаемому является устройство для интегрирования, состоящее из блока сумми зования и блока умножения значений функции на коэффициенты матриц, входы первых групп которых соединены соответственно с информационными входами устройства, блока умножения значений интегральной функции в точках на табличные коэффициенты, входы которого соединены соответственно с входами задания интерполяционных коэффициентов, задания предшествующих значений интегрируемой функции и входом задания величины шага интегрирования устроиства, а выходы подключены соответственно к входам второй группы блока суммирования, выходы которого являются выходами устройства, входы TpaTbevi группы блока суммирования соединены соответственно с выходами блока умножения значений функции на коэффициенты матриц, входы второй группы которого подключены соответственно к входам коэффициентов устройства, вход начальных значений интеграла и вход задания величины шага интегрирования устройства подключены к соответствующим входам блока суммирования 31 Недостатком данного устройства является значительный рост аппарату ных затрат с ростом интервала интегрирования, так как на один шаг интегрирования в среднем используются три умножителя и сумматор. .

Цель изобретения.- снижение аппаратурных затрат без ограничения н интервал интегрирования.

Поставленная цель достигается тем, что в устройство содерх ащее генератор импульсов, блок суммирования и блок умно)хителей первая группа входов которого соединена соответственно с первой группой блока суммирования, введены блок накапливания промежуточных значений интеграла, блок регистров текущих значений интегрируемой , йтробирующая группа элементов И, два элемента И, причем каждая 1-ая группа выходов регистров текущих значений интегрируемой функции подключена к 1-«-1-ой группе входов блока умножителей, а последняя группа выходов подключена к первой группе входов блока накапливания промежуточных значений интеграла, .другой вход котррого подключен к входу задания начального значения интеграла интегратора, а выходы - к второй группе входов блока суммирования, выходы которого подключены к первым входам стробирующих элементов И, выходы которых являются выходами устройства, вторая группа входов блока умножителей подключена ко входам первого элемента И, выход которого подключен к вторым входам стробирующих элементов И, первому входу второго элемента И, выход которого соединен со сдвиг ющим входом блока регистров текущих значений интeгpиpye ЮЙ функции, а

второй вход второго элемента И подключен к выходу генератора импульсов, информационные входы устройства соединены с входами блока регистров текущих значений интегрируемой функции.

Кроме того, блок накапливания промежуточных значений интеграла содержит сумматор и регистр, причем входы первой группы входов сумматоoра подключены к группе входов блока, входы второй группы - к выходам регистра, входы которого подключены к соответствующим выходам сумматора,

5 вход начального значения которого .подключен к входу начального значения блока, а выходы - к выходам блока..

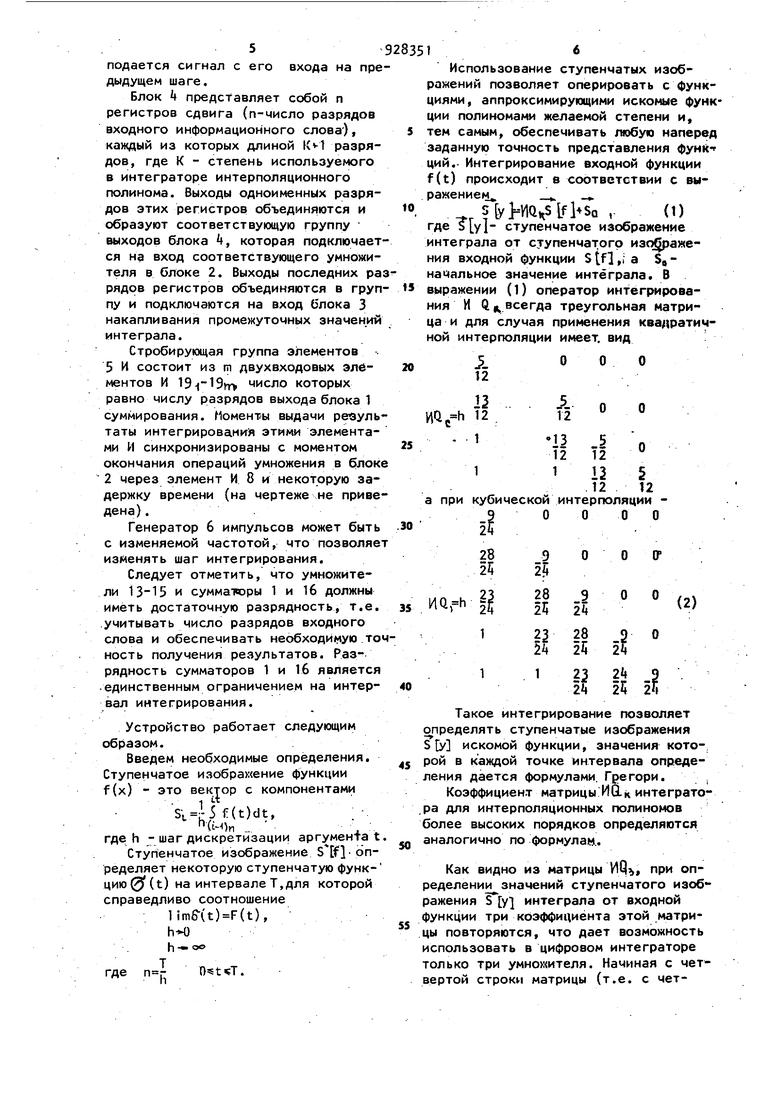

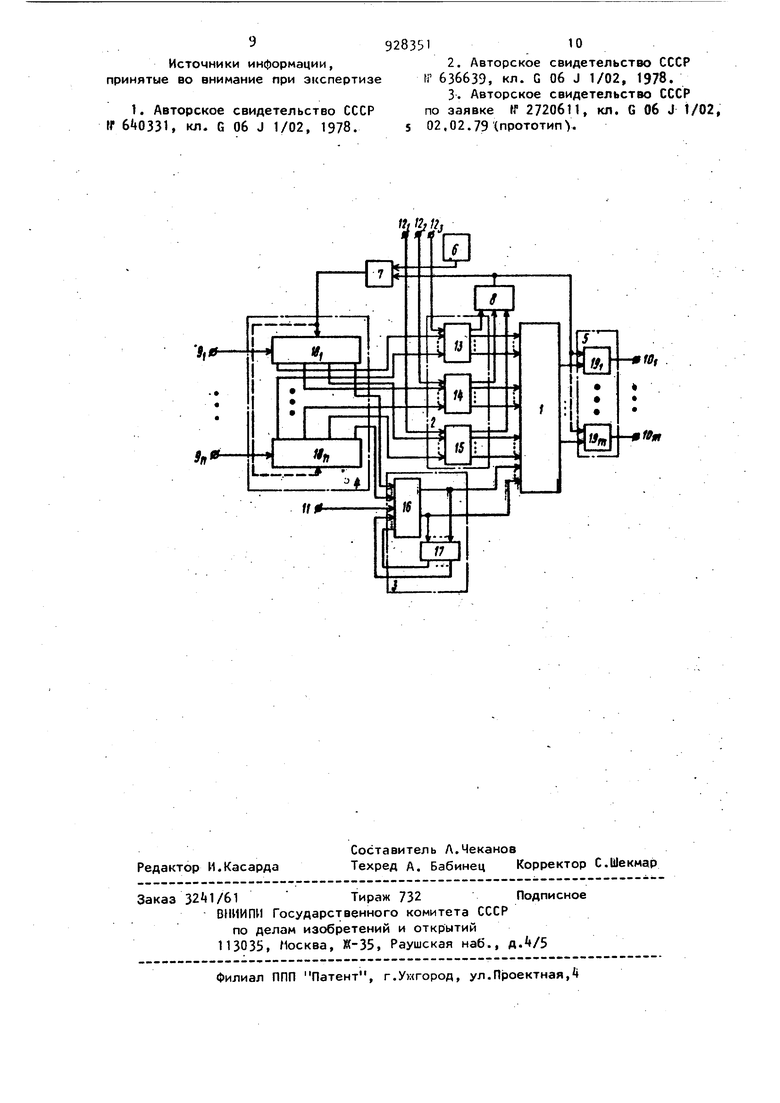

На чертеже представлена, схема

0 интегратора для случая кубической интерполяции.

Интегратор содержит блок 1 суммирования, блок 2 умножителей блок 3 накапливания промежуточных значе5ний интеграла, блок 4 регистров текущих значений интегрируемой функции, стробирующую.; группу элементов 5 И генератор 6 импульсов, элементы И 7 и 8, входы устройства, выходы lOv -IOrri устройства, вход 11 задания начальных значений интегра%ia, входы )j задания интерполяционных коэффициентов, умноиители 13-15, сумматор 16, регистры 17,

5 I8f-l8n, элементы И .

Блок 1 представляет собой п-входовой комбинационный сумматор, способный осуществлять алгебраическое суммирование.

0

Блок 2 содержит умножители 13 15 АЛЯ образования произведений текущих значений входной функции на интерполяционные коэффиценты. Число таких умножителей всегда равно сте5пени применяемого в интеграторе Интерпол я ционногс) полинома и, значит, зависит от желаемой точности получения результата интегрирования. Входы каждого 1-го умножителя

0 образуют f+1-ую группу входов блока 2..

Блок 3 состоит из регистра 17 и п-входоеого комбинационного сумматора 16, выход которого является

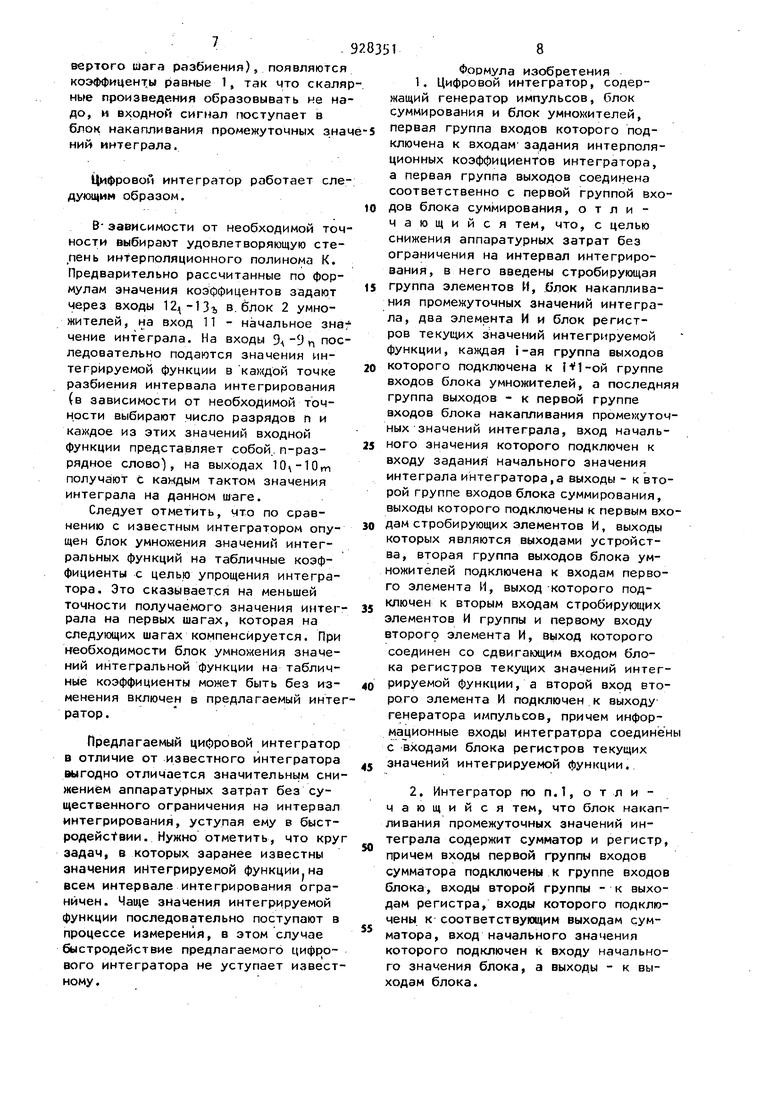

5 выходом блока 3, подается на вход блока 1 суммирования и на вход регистра 17, так что на каждом шаге интегрирования на вход сумматора 1б подается сигнал с его входа на пре дыдущем шаге. Блок представляет собой п регистров сдвига (п-число разрядов входного информационного слова), каждый из которых длиной разрядов, где К - степень используемого в интеграторе интерполяционного полинома. Выходы одноименных разрядов этих регистров объединяются и образуют соответствующую группу выходов блока k, которая подключает ся Н9 вход соответствующего умножителя в блоке 2. Выходы последних ра рядов регистров объединяются в груп пу и подключаются на вход блока 3 накапливания промежуточных значений интеграла. Стробирующая группа элементов 5 И состоит из m двухвходовых элементов И число которых равно числу разрядов выхода блока 1 суммирования. Моменты выдачи резуль таты интегрировамия этими элементами И синхронизированы с моментом окончания операций умножения в блок 2 через элемент И 8 и некоторую задержку времени (на чертеже не приве дена). Генератор 6 импульсов может быть с изменяемой частотой, что позволяе изменять шаг интегрирования. Следует отметить, что умножители 13-15 и сумматоры 1 и 16 должны иметь достаточную разрядность, т.е. .учитывать число разрядов входного слова и обеспечивать необходимую то ность получения результатов. Разрядность сумматоров 1 и 16 является единственным ограничением на интервал интегрирования. Устройство работает следующим образом. Введем необходимые определения. Ступенчатое изображение функции f(x) - это вектор с компонентами 1 f(t)dt, ; )n . где h - шаг дискретизации аргументам Ступенчатое изображение определяет некоторую ступенчатую функ ю0(t) на интервале Т, для которой справедливо соотношение lime(t)F(t), . Использование ступенчатых изображений позволяет оперировать с функциями, аппроксимирующими искомые функции полиномами желаемой степени и, тем самым, обеспечивать любую наперед заданную точность представления функций.. Интегрирование входной функции f(t) происходит в соответствии с выражением S y MQKSlf SQ ,(1) где ступенчатое изображение интеграла от ступенчатого изо ражения входной функции S (fl,; а S, начальное значение интеграла. В выражении (1) оператор интегрирования И QI всегда треугольная матрица и для случая применения квадратичной интерполяции имеет, вид. 000 12 а при кубической интерполяции О О О О 2 HQrh I Такое интегрирование позволяет определять ступенчатые изображения Sty искомой функции, значения которой в каждой точке интервала опредеения дается формулами. Грегори. . Коэффициент матрицыИйк интегратора для интерполяционных полиномов олее высоких порядков определяются аналогично по формулам.. Как видно из матрицы Иц при опеделении значений ступенчатого изобажения интеграла от входной ункции три коэффициента этой матриы повторяются, что дает возможность спользовать в цифровом интеграторе олько три умножителя. Начиная с четертой строки матрицы (т.е. с . вертого шага разбиения), появляются коэффиценты разные 1, так что скаля ные произведения образовывать не на до, и входной сигнал поступает в блок накапливания промежуточных зна НИИ интеграла. Цифровой интегратор работает сле дующим образом. В- зависимости от необходимой точ ности выбирают удовлетворяющую интерполяционного полинома К. Предварительно рассчитанные по формулам значения коэффицентов задают через входы в. блок 2 умножителей, на вход 11 - начальное 3Ha чение интеграла. На входы ледовательно подаются значения интегрируемой функции в каждой точке разбиения интервала интегрирования (в зависимости от необходимой точности выбирают число разрядов п и ка)хдое из этих значений входной функции представляет собой., п-разрядное слово), на выходах получают с камдым тактом значения интеграла на данном шаге. Следует отметить, что по сравнению с известным интегратором опущен блок умножения значений интегральных функций на табличные коэффициенты с целью упрощения интегратора. Это сказывается на меньшей точности получаемого значения интег рала на первых шагах, которая на следующих шагйх компенсируется. При необходимости блок умножения значений интегральной функции на табличные коэффициенты может быть без изменения включен в предлагаемый инте ратор. Предлагаемый цифровой интегратор а отличие от известного интегратора выгодно отличается значительнь1м сни жением аппаратурных затрат без существенного ограничения на интервал интегрирования, уступая ему в быстpoдeйctвии. Нужно отметить, что кру задач, в которых заранее известны значения интегрируемой функции на всем интервале интегрирования ограничен. Чаще значения интегрируемой функции последовательно поступают в процессе измерения, в этом случае быстродействие предлагаемого цифрового интегратора не уступает извест ному , 1 Формула изобретения 1.Цифровой интегратор, содержащий генератор импульсов, блок суммирования и блок умнох ителей, первая группа входов которого подключена к входамзадания интерполяционных коэффициентов интегратора, а первая группа выходов соединена соответственно с первой группой входов блока суммирования, отличающийся тем, что, с целью снижения аппаратурных затрат без ограничения на интервал интегрирования, в него введены стробирующая группа элементов И, блок накапливания промежуточных значений интеграла, два элемента И и блок регистров текуихих значений интегрируемой функции, каждая i-ая группа выходов которого подключена к И 1-ой группе входов блока умножителей, а последняя группа выходов - к первой группе входов блока накапливания проме, уточных значений интеграла, вход начального значения которого подключен к входу задания начального значения интеграла интегратора,а выходы - к второй группе входов блока суммирования, выходы которого подключены к первым входам стробирующих элементов И, выходы которых являются выходами устройства, вторая группа выходов блока умножителей подключена к входам первого элемента И, выход-которого подключен к вторым входам стробирующих элементов И группы и первому входу второго элемента И, выход которого соединен со сдвигающим входом блока регистров текущих значений интегрируемой функции, а второй вход второго элемента И подключен к выходу генератора импульсов, причем информационные входы интегратора соединёны с входами блока регистров текущих значений интегрируемой функции. 2.Интегратор по п.1, о т л и чающийся тем, что блок накапливания промежуточных значений интеграла содержит сумматор и регистр, причем входы первой группы входов сумматора подключены к группе входов блока, входы второй группы - к выходам регистра, входы которого подключены к соответствующим выходам сумматора, вход начального значения которого подключен к входу начального значения блока, а выходы - к выходам блока.

92835110

Источники информации,2. Авторское свидетельство СССР

принятые во внимание при экспертизе ff 636639, кл. G Об J 1/02, 1978.

I. Авторское свидетельство СССР по заявке № 2720611, кл. G 06 J 1/02, № , кл. G 06 J 1/02, 1978. 5 02.02.79 (прототипу.

Авторы

Даты

1982-05-15—Публикация

1980-03-10—Подача