констант соединены соответственно с вторым информационным выходом процессора и с информационным входом блока памяти, установочный вход блока согласования с источником констант соединен с вторым установочным выходом блока управления, выход сигнала окончания-приема блока согласования с источником крнстант соединен с входом признака окончания приема блока управления, отличающийся тем, что, с целью повышения надежности за счет предотвращения неверной идентификации событий при нарушении порядка размеш,ения входных слов в их последовательности и учета случаев нарушения указанного порядка, в него введен блок контроля последовательности слов, первый, второй, третий и четвертый информационные входы которого подключены соответственно к выходам разрядов регистра ввода, к выходу контрольных констант блока памяти, к выходу числа слов в группе блока памяти и к выходам разрядов счетчика слов, информационный выход соединен с третьим информационным входом блока согласования с источником констант, установочный вход блока контроля последовательности слов соединен с третьим установочнь м вы- ходом блока управления, вход признаков которого соединен с выходом признаков блока контроля последовательности слов, причем блок контроля последовательности слов содержит группу элементов И, схему сравнения, счетчики, элементы И, триггеры и дешифратор единицы, вход которого является четвертым информационным входом блока контроля последовательности слов, первые входы элементов И группы соединены с первым информационным входом блока контроля посоедовательности слов, вторые входы соединены с вторым информационным входом блока контроля последовательности слов, выходы элементов И подключены к первому входу схемы сравнения, второй вход которой соединен с вторым информационным входом блока контроля последовательности слов, выходы равенства и неравенства схемы сравнения соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых и установочные входы первого, второго, третьего счетчиков и первого и второго триггеров соединены с установочным входом блока контроля последовательности слов, выход второго элемента И соединен со счетными входами первого и второго счетчиков, с единичными входами первого и второго триггеров и с выходом признаков блока контроля последовательности слов, выходы разрядов первого и третьего счетчиков являются информационным выходом блока контроля последовательности слов, информационный вход второго счетчика является третьим информационным входом блока контроля последовательности слов, выход первого элемента И подключен к входу управления приемом второго счетчика, к первому нулевому входу первого триггера и к первому входу третьего элемента И, второй вход которого соединен с выходом дешифратора единицы, а выход подключен к нулевому входу второго триггера, выход переполнения второго счетчика соединен с вторым нулевым входом первого триггера, со счетным входом третьего счетчика и с выходом признаков блока контроля последовательности слов, выходы первого и второго триггеров соединены с выходом признаков блока контроля последовательности слов, а блок управления содержит триггер, элементы задержки, распределитель импульсов, синхронизаторы двух сигналов, элемента И, ИЛИ, узел синхронизации сигналов и узел начальной установки, выход которого соединен с установочными входами первого и второго синхронизаторов двух сигналов, узла синхронизации сигналов, вторым и третьим установочными выходами блока и с первым входом первого элемента ИЛИ, выход которого соединен с первым установочным выходом блока и через первый элемент задержки с нулевым входом триггера, информационный вход и первый информационный выход первого синхронизатора двух сигналов являются соответственно первыми входом и выходом блока управления, второй информационный выход соединен с первым входом второго элемента ИЛИ и с третьим выходом приема блока, а разрешаюш,ий вход подключен к выходу третьего элемента ИЛИ, выход второго элемента ИЛИ соединен с входом распределителя импульсов, первый и второй выходы которого являются соответственно первым и вторым тактовыми выходами блока, третий выход распределителя импульсов соединен с третьим установочным выходом блока, четвертый выход распределителя подключен к первым входам первого и второго элементов И, пятый выход соединен с первым входом третьего элемента И, выход которого подключен к запускающему входу узла синхронизации, вход признаков блока управления соединен с входом второго элемента задержки, с вторым входом второго элемента ИЛИ, с первыми входами четвертого элемента ИЛИ и четвертого элемента И, с первым входом пятого элемента И, с вторым входом первого элемента И и с вторым входом второго элемента И, выход второго элемента задержки соединен с первым входом пятого элемента ИЛИ, единичный выход триггера соединен с первым входом шестого элемента И и с вторым входом третьего элемента И, нулевой выход триггера соединен с третьим входом первого элемента И и с вторым входом четвертого элемента И, выход первого элемента И соединен с первым входом третьего элемента ИЛИ, второй вход которого и второй вход четвертого элемента ИЛИ соединены с выходом пятого элемента И, второй вход которого соединен,с первым .выходом узла синхронизации сигналов, второй выход которого является первым выходом приема блока управления, вход признака является входом признака выполнения критерия блока, а третий выход соединен с первым информационным входом второго синхронизатора двух сигналов, первый информационный выход которого соединен с вторым выходом приема блока и с входом запроса узла синхронизации сигналов, вторые информационные вход и выход синхронизатора двух сигналов являются соответственно вторыми входом и выходом блока, вход признака окончания приема которого соединен с третьим входом третьего элемента ИЛИ, с первым входом шестого элемента ИЛИ и с вторым входом пятого элемента ИЛИ, выход которого соединен с третьим установочным выходом блока, выходы второго элемента И и шестого элемента ИЛИ соединены с выходом установки счетчиков блока, единичный вход триггера соединен с входом признака числа слов блока, выход четвертого элемента ИЛИ соединен с вторым входом шестого элемента И, выход которого подключен к вторым входам первого и шестого элементов ИЛИ, выход четвертого элемента И соединен с третьим входом шестого элемента ИЛИ.

2.Процессор по п. 1, отличающийся тем, что блок проверки комбинаций условий содержит счетчик, элемент И и узлы сравнения, первые входы которых соединены с первым информационным входом блока, вторые входы подключены к второму информационному входу блока, входы элемента И соединены соответственно с выходами узлов сравнения и с установочным входом блока, счетный вход счетчика подключен к выходу элемента И, информационный и установочный входы счетчика соединены соответственно с третьим информационным и с установочным входами блока, выход переполнения счетчика является выходом блока.

3.Процессор по п. 1, отличающийся тем, что блок формирования адресов событий содержит регистр и шифратор, вход которого является вторым информационным входом блока, первый информационный вход которого соединен с входами младших разрядов регистра, входы старших разрядов которого подключены к выходу шифратора, вход разрешения приема регистра является разрешаюшим входом блока, выходы разрядов регистра являются выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля времени выполнения программ | 1982 |

|

SU1059575A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Программируемый контроллер | 1989 |

|

SU1780086A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Устройство для вывода информации | 1983 |

|

SU1124279A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

1. ПРОЦЕССОР ДЛЯ ИДЕНТИФИКАЦИИ И АДРЕСОВАНИЯ СОБЫТИЙ содержащий регистр ввода, информационный вход которого является первым информационным входом процессора, регистр вывода, выходы разрядов которого являются первым информационным выходом процессора, блок памяти, счетчик слов, группы элементов И, блоки сравнения, блоки проверки комбинаций условий, элемент ИЛИ, регистр адресной переменной, блок согласования с источником констант, блок управления и блок формирования адресов событий, выход которого соединен с информационным входом регистра вывода, выходы разрядов регистра ввода подключены соответственно к первым входам элементов И каждой группы, вторые входы которых соединены с выходом кодов масок блока памяти, выходы элементов И каждой группы подключены к первой группе входов соответствующего блока сравнения, вторая.группа входов каждого блока сравнения соединена с выходом констант блока памяти, выход каждого блока сравнения подключен к первому информационному входу соответствующего блока проверки комбинаций условий, второй и третий информационные входы которого соединены соответственно с выходом кодов отнощений сравнения и с выходом числа слов в группе блока памяти, установочный вход каждого блока проверки комбинаций условий и разрещающий вход регистра адресной переменной соединены с выходом установки начальных значений блока управления, информационный вход регистра адресной переменной подключен к выходам элементов И групп, вход запрещения приема соединен с выходом указателя адресной переменной блока памяти, а выход подключен к первому информационному входу блока формирования адресов событий, второй информационный вход которого и входы элемента ИЛИ соединены с выходами блоков проверки комбинаций условий, выход элемента ИЛИ подключен к входу признака выполнения критерия блока управления, первый, второй и третий выходы приема которого соединены SS соответственно с разрещающими входами блока формирования адресов событий, реСО гистра вывода и регистра ввода, первый и второй входы блока управления являются соответственно входом заявки на прием и управляющим входом выдачи процессора, первый и второй выходы блока управления являются соответственно выходом сигнала запроса следующего слова и выходом разрешения выдачи адреса процессора, первый 00 и второй тактовые выходы блока управления 00 соединены соответственно со счетным входом 1 счетчика слов и с в.ходом разрещения приема блока памяти, адресный вход которого подNU ключен к выходам разрядов счетчика слов, 00 информационный вход которого соединен с выходом числа слов в группе блока памяти, установочный вход счетчика слов соединен с первым установочным выходом блока управления, выход сигнала заданного числа слов соединен с входом признака числа слов блока управления, первый и второй информационные входы блока согласования с источником констант соединены соответственно с вторым информационным входом процессора и с информационным выходом блока памяти, первый и второй информационные выходы блока согласования с источником

Изобретение относится к вычислительной технике и может использоваться для идентификации и адресования событий, информация о которых заключена в последовательно подаваемых на вход процессора и имеющим одинаковую длину группах входных слов, в каждой из которых одинаково размещены переменные величины. Процессор может применяться в измерительно-вычислительных, системах регистрации спектров в ядерной физике.

Цель изобретения - повышение надежности за счет предотвращения неверной идентификации событий при нарушении порядка размещения входных слов в их последовательности и учета случаев нарушения указанного порядка.

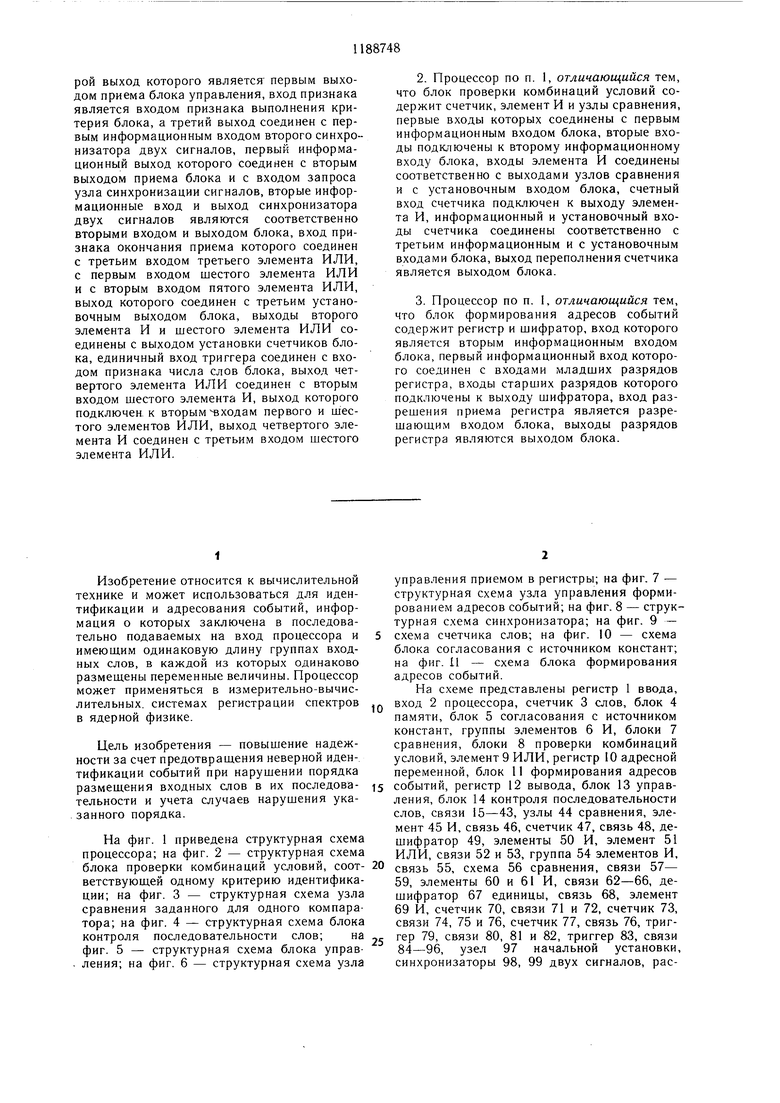

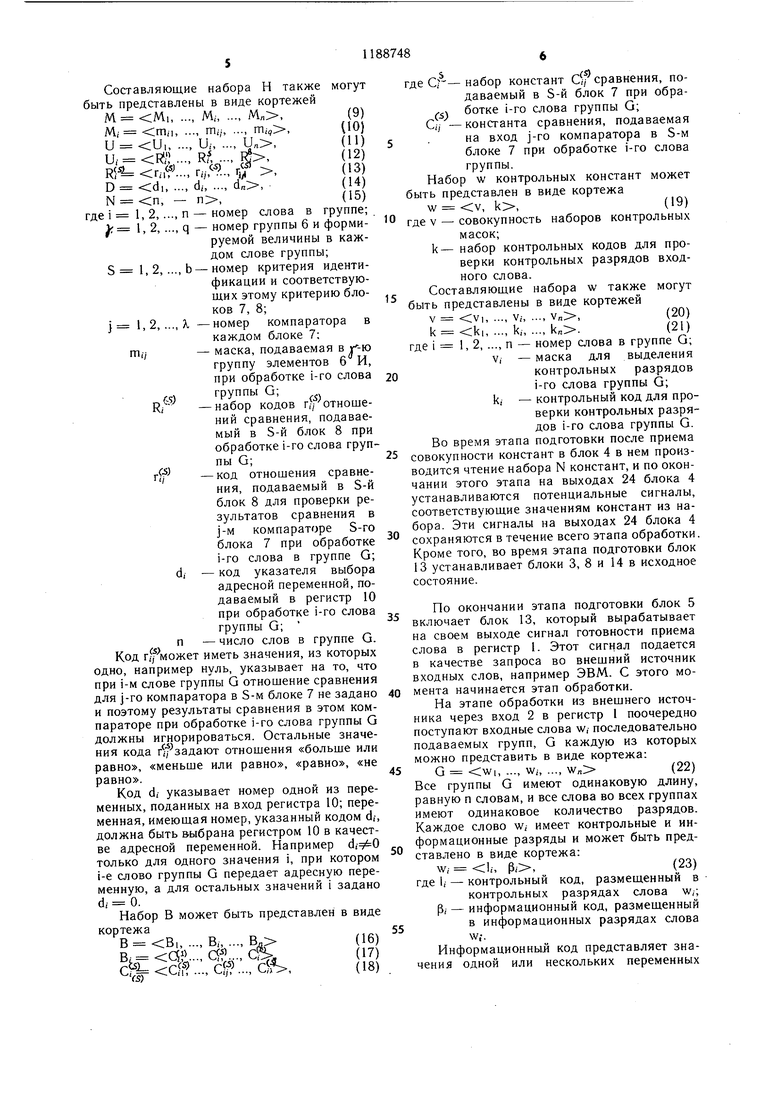

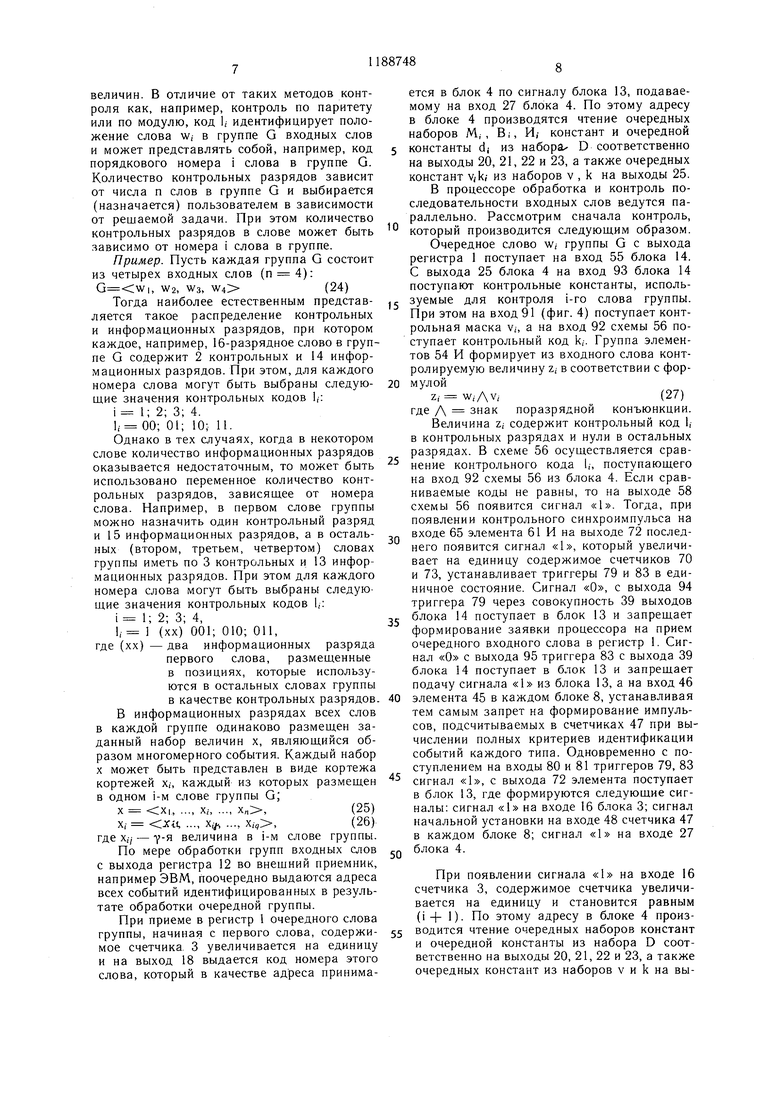

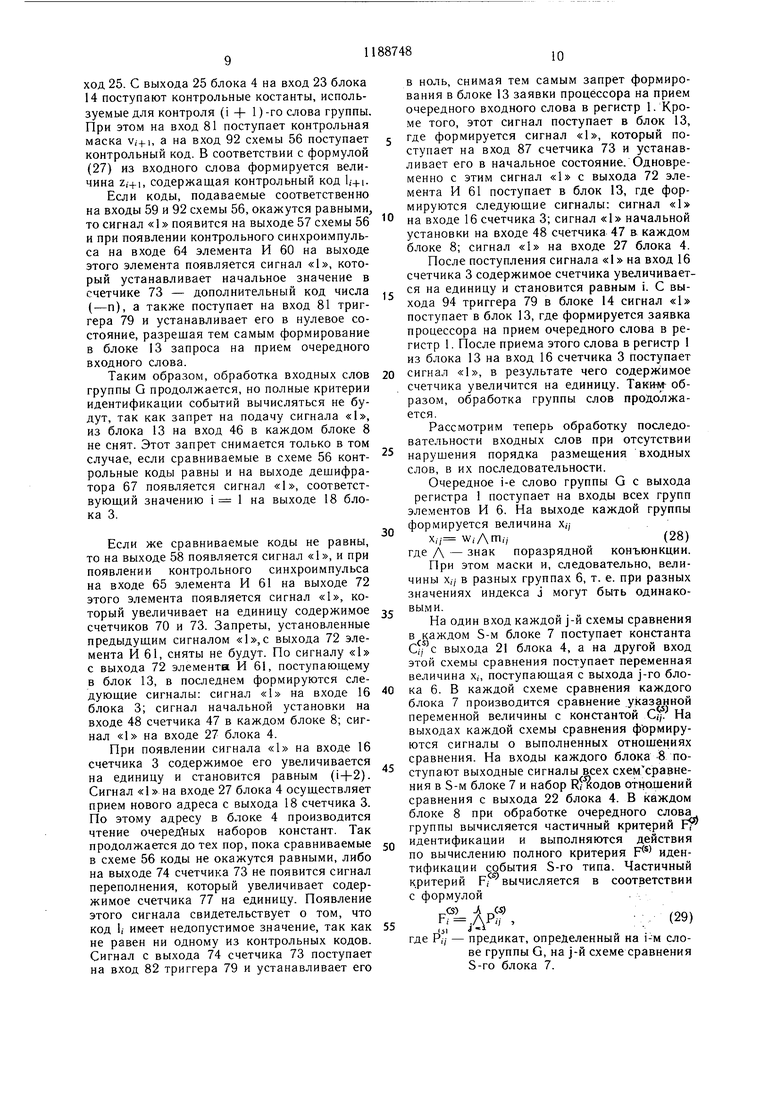

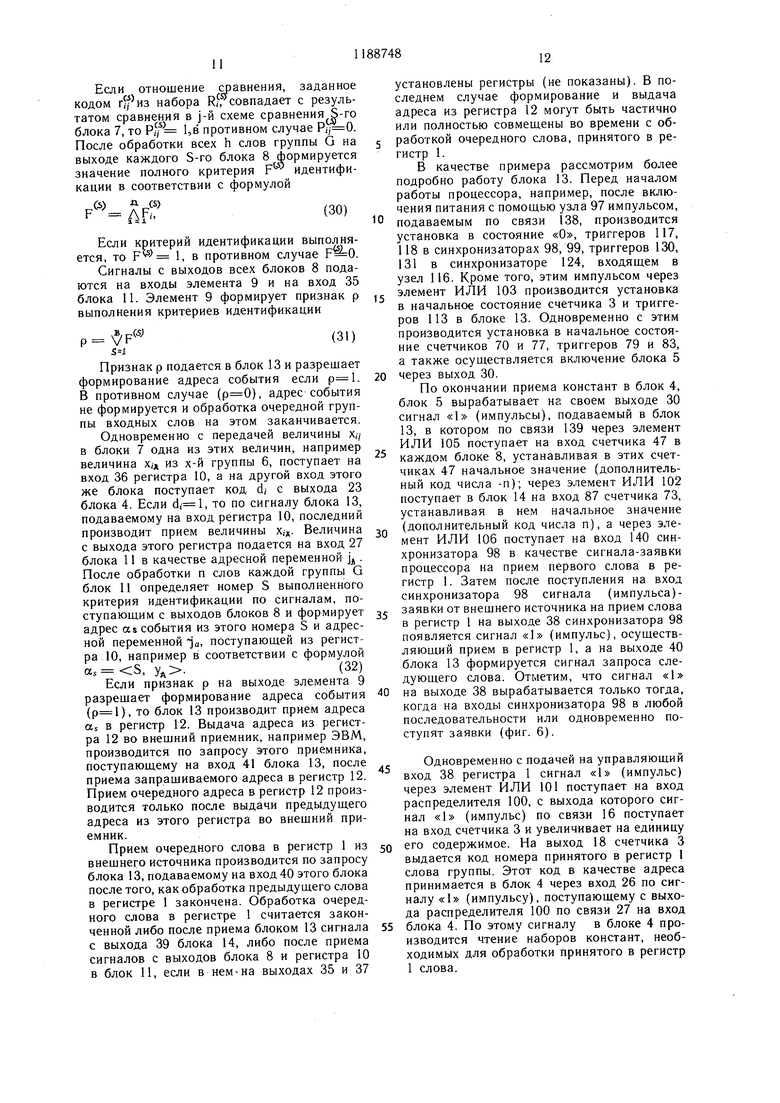

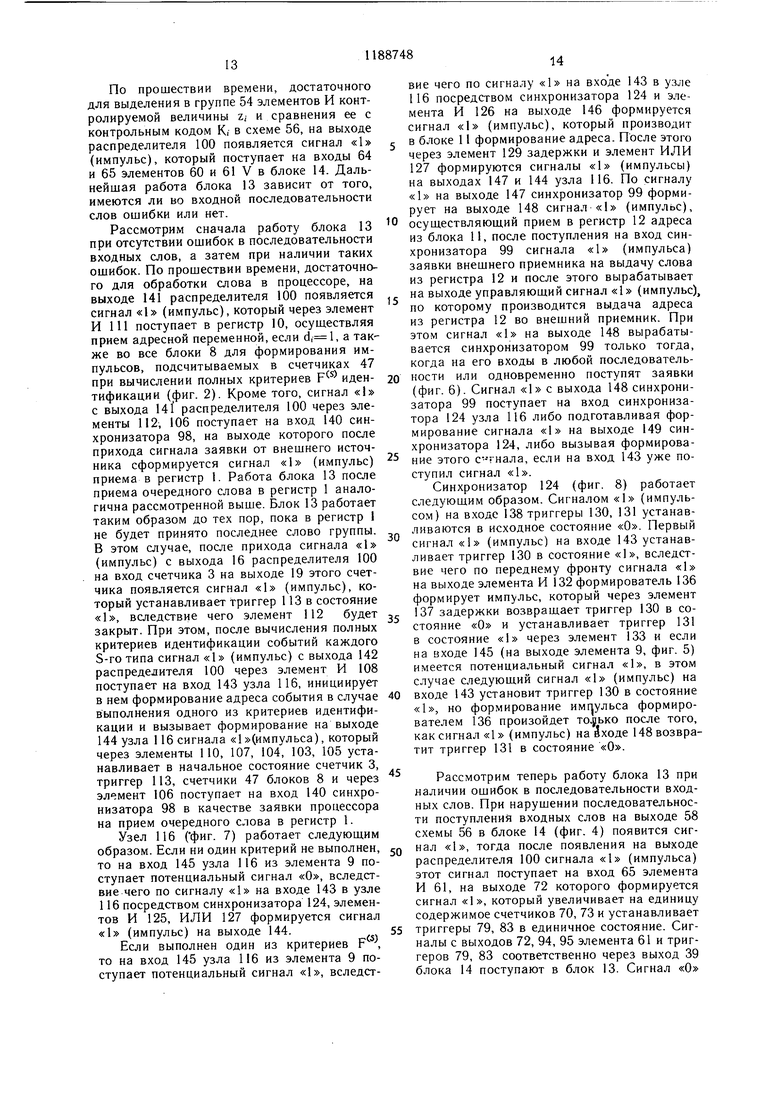

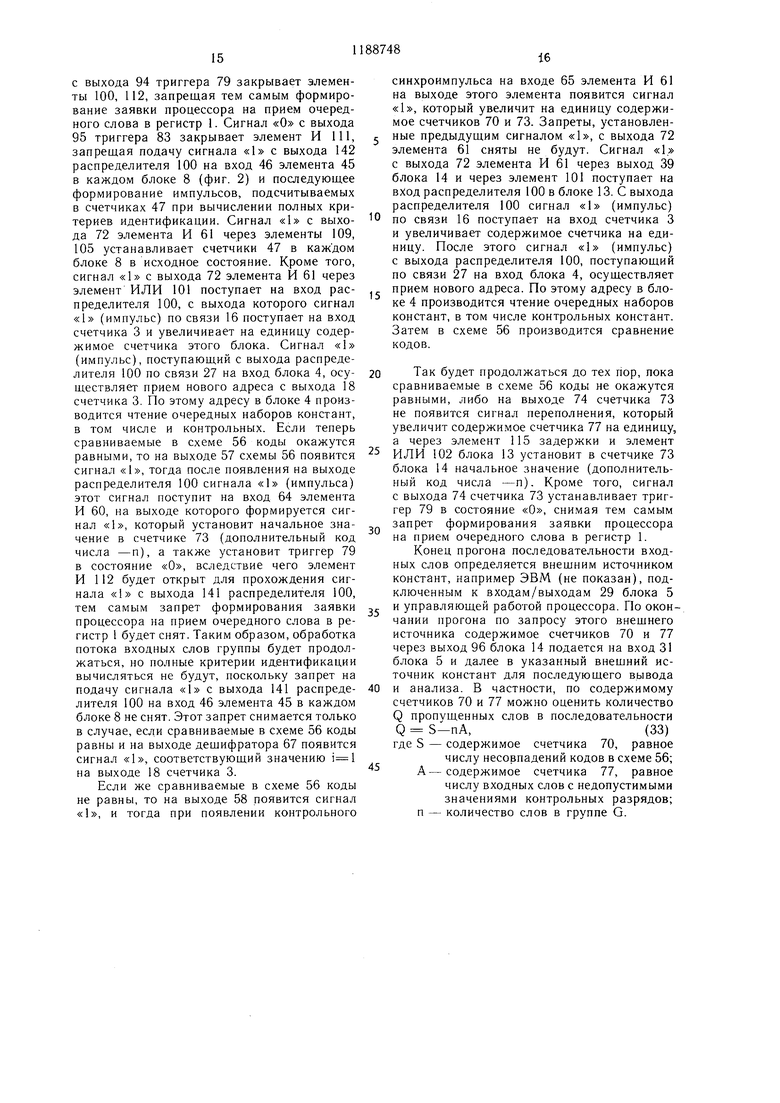

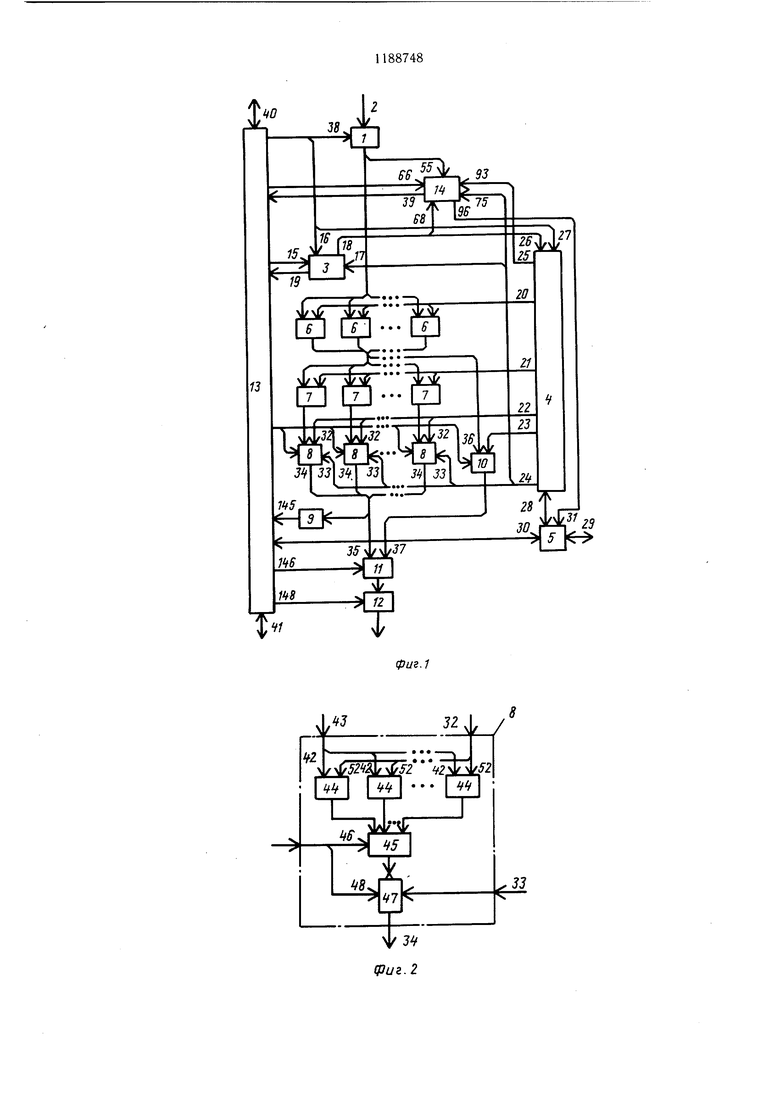

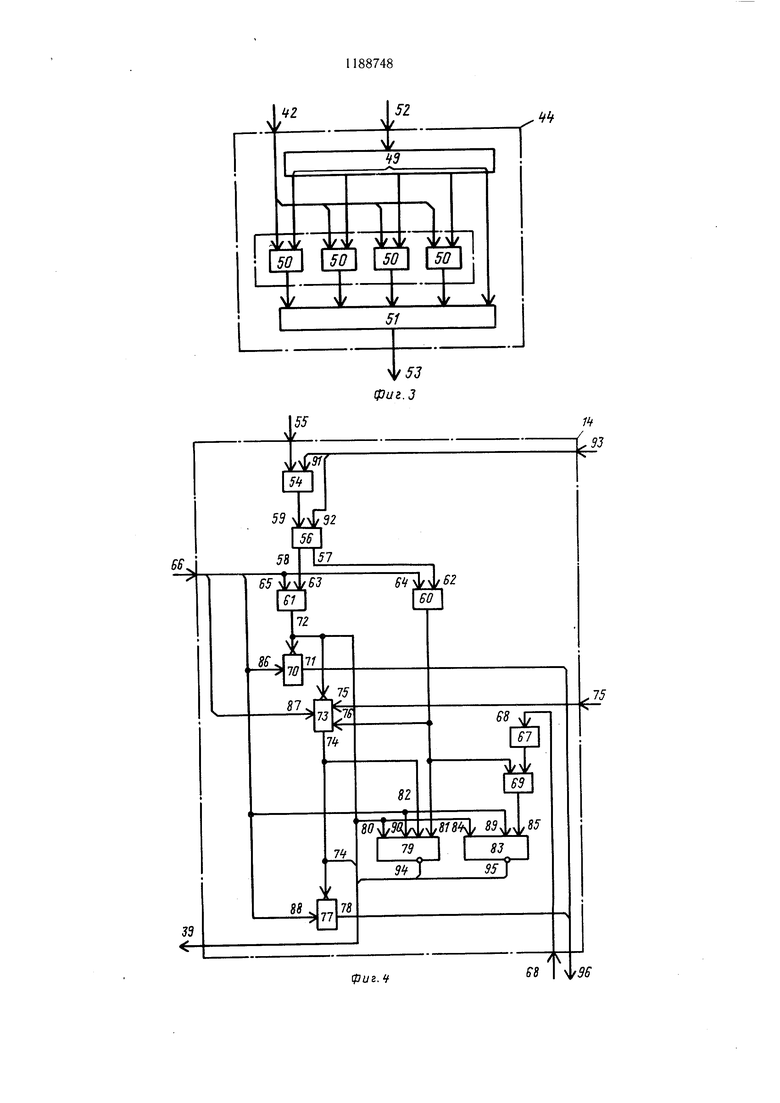

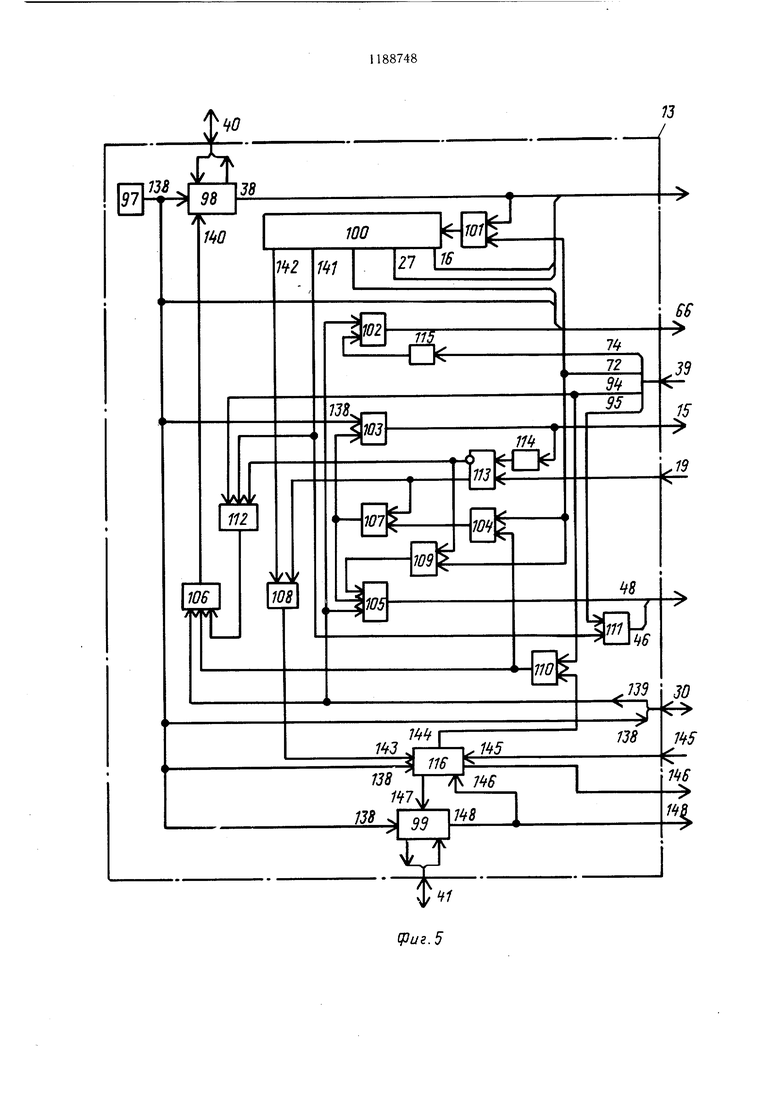

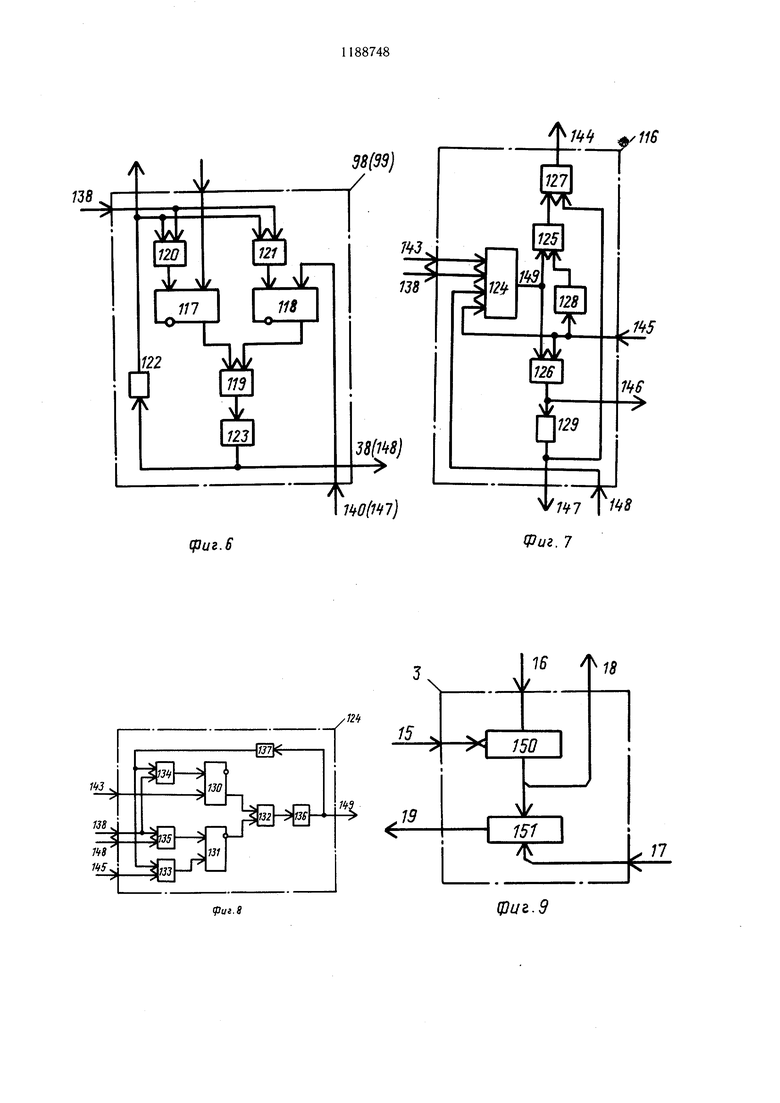

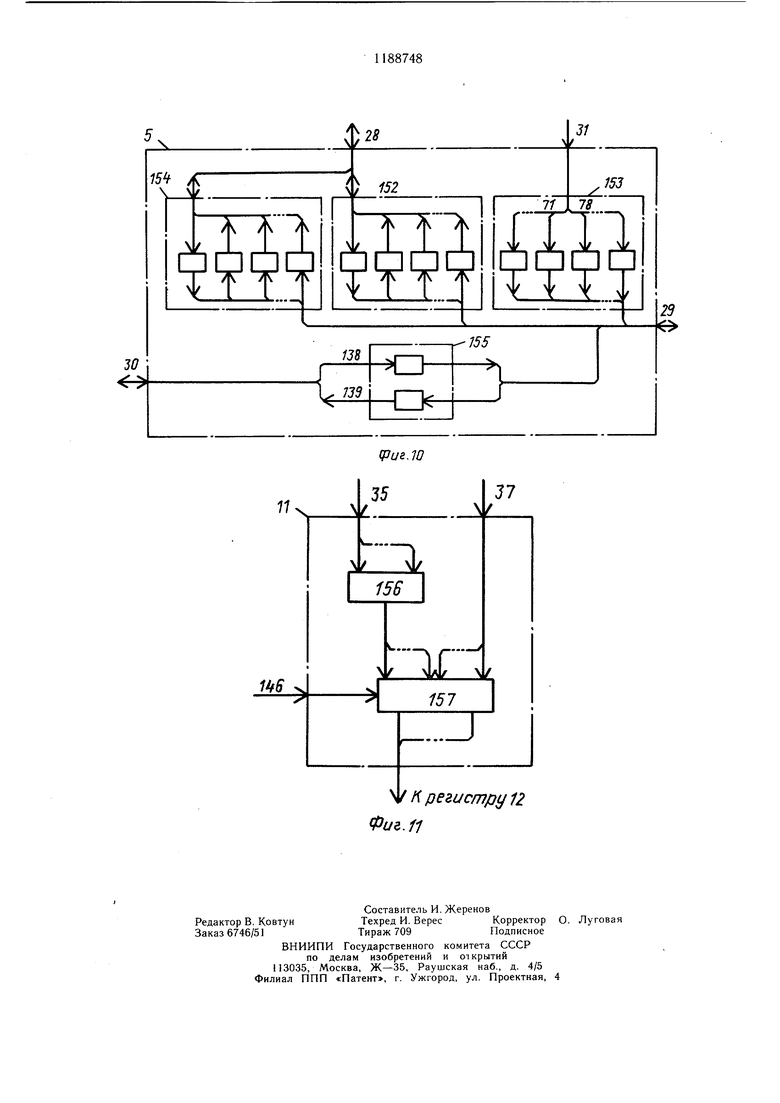

На фиг. 1 приведена структурная схема процессора; на фиг. 2 - структурная схема блока проверки комбинаций условий, соответствующей одному критерию идентификации; на фиг. 3 - структурная схема узла сравнения заданного для одного компаратора; на фиг. 4 - структурная схема блока контроля последовательности слов; на фиг. 5 - структурная схема блока управ. ления; на фиг. 6 - структурная схема узла

управления приемом в регистры; на фиг. 7 - структурная схема узла управления формированием адресов событий; на фиг. 8 - структурная схема синхронизатора; на фиг. 9 - схема счетчика слов; на фиг. 10 - схема блока согласования с источником констант; на фиг. 11 - схема блока формирования адресов событий.

На схеме представлены регистр 1 ввода, вход 2 процессора, счетчик 3 слов, блок 4 памяти, блок 5 согласования с источником констант, группы элементов 6 И, блоки 7 сравнения, блоки 8 проверки комбинаций условий, элемент 9 ИЛИ, регистр 10 адресной переменной, блок 11 формирования адресов событий, регистр 12 вывода, блок 13 управления, блок 14 контроля последовательности слов, связи 15-43, узлы 44 сравнения, элемент 45 И, связь 46, счетчик 47, связь 48, дешифратор 49, элементы 50 И, элемент 51 ИЛИ, связи 52 и 53, группа 54 элементов И, связь 55, схема 56 сравнения, связи 57- 59, элементы 60 и 61 И, связи 62-66, дешифратор 67 единицы, связь 68, элемент 69 И, счетчик 70, связи 71 и 72, счетчик 73, связи 74, 75 и 76, счетчик 77, связь 76, триггер 79, связи 80, 81 и 82, триггер 83, связи 84-96, узел 97 начальной установки, синхронизаторы 98, 99 двух сигналов, распределитель 100 импульсов, элементы 101 - 106 ИЛИ, элементы 107-112 И, триггер 113, элементы 114 и 115 задержки, узел 116 синхронизации сигналов, триггеры 117 и 118, элемент 119 И, элементы 120 и 121 ИЛИ, элемент 122 задержки, формирователь 123 прямоугольных импульсов, синхронизатор 124 двух импульсов, элементы 125 и 126 И, элемент 127 ИЛИ, элемент 128 НЕ, элемент 129 задержки, триггеры 130 и 131, элементы 132 и 133 И, элементы 134 и 135 ИЛИ, формирователь 136 прямоугольных импульсов, элемент 137 задержки, связи 138-149, счетчик 150, схема 151 сравнения, группы 152- 155 формирователей прямоугольных импульсов, шифратор 156, регистр 157. Каждый блок 7 содержит более двух компараторов, каждый из которых выполнен с выходами «Больше или равно, «Меньше или равно, «Равно, «Не равно. Один вход каждого компаратора, служаш.ий для подачи переменной величины, соединен с выходом одной из групп элементов 6 И. Другой вход каждого компаратора, служаш,ий для подачи константы сравнения, соединен с соответствуюш,им этому компаратору отдельным выходом 21 блока 4. Количество блоков 8 равно количеству блоков 7 и между блоками 8 и 7 существует взаимно однозначное соответствие: выходы каждого блока 7 соединены с входами одного блока 8, служаш.ими для подачи результатов сравнения, полученных в этом блоке 7, и наоборот. В каждом блоке В входы 32 служат для одновременной подачи всех кодов отношений сравнения, заданных для одного блока 7. Вход 33 блока 8, служаш,ий для подачи информации о числе входных слов в группе, соединен с отдельным выходом из набора 24 выходов блока 4. Выход 34 каждого блока 8 служит для выдачи вычисленного значения одного критерия идентификации. В регистре 10 информационный вход 36, служащий для подачи переменной величины, соединен с выходом одной из групп элементов 6 И. Пример. Последовательность L входных слов, состоящая из h групп G слов, может быть представлена в виде кортежа L G,, ..., G,, ..., а„,(1) где (, 2, ..., h - номер группы G слов в последовательности входных слов; GH- ц-я группа G слов в последовательности L входных слов. Пусть при этом каждая группа G состоит из двух слов , ,(2). где - первое слово х-й группы G входных слов, содержащее, например, код времени пролета частиц; Wn2 - второе слово ц-й группы G входных слов, содержащее, например, код состояния детекторов. Подставив (2) в (I), получим L Wii, Wi2, ..., Wц|, Wц2, ..-, WAI, (3) Пропуск, например, слова w:2 в группе GI последовательности L приводит к тому, что вместо последовательности L получим последовательность L L Wi|, Wi2, W22, ..., , , ..., WAI, WA2 (4) Процессор интерпретирует последовательность L как последовательности групп G слов таким образом, что в первую группу G включает первые h слов (в данном примере h 2), во вторую группу G| - вторые h слов и т. д. т --- г-- р. р. р, -./с L - С Uj, (Jj, ..., U, ..., Ll ,(О) G Wi|, Wi2 , G| W22, W31 J(6) Из формул (6) и (2) видно, что последовательность L содержит ошибочные группы, например, G,, Ga вместо верных групп GI, G2 в последовательности L GI W||, W|2 j/-y G2 W21, W22 J Таким образом, при нарушении порядка размещения входных слов в их последовательности в результате пропуска даже одного слова вся следующая за ним последовательность входных слов интерпретируется неверно, т. е. события идентифицируются неверно. Аналогичным образом последовательность входных слов будет интерпретироваться неверно при пропуске любого числа слов за исключением тех случаев, когда пропущенные слова, расположенные подряд в «истинной последовательности (т. е. в той, которая должна бы быть при отсутствии пропуска слов) составляют одну или несколько целых групп G входных слов. Работа процессора подразделяется на два этапа: этап подготовки и следующий за ним этап обработки потока групп входных слов. На этапе подготовки из внешнего источника, например электронной вычислительной машины (ЭВМ), через вход 29 блока 5 в блок 4 поступает совокупность констант, определяющая последующую обработку потока групп G входных слов. Эта совокупность состоит из набора Н управляющих констант, набора С констант сравнения и набора w контрольных констант. Набор Н может быть представлен в виде кортежа Н М, и, D, N, (8) где М - совокупность наборов масок; и - совокупность наборов кодов отнощений сравнения; D - набор указателей выбора адресной переменной; N - набор, представляющий информацию о числе входных слов в группе.

Составляющие набора Н такжемогут быть представлены в виде кортежей

, .... М„ ..., Мл,(9)

M; mn, ..., mij, ..., т;,,)

и и,, ..., и,-, .... у„,(11)

и,..., Rf, ..., Й,(12)

1(&- j-.ff) г..С-S) r«5l (:,(

Kl .1,1, ..., r,j, ..., Fja ,I-J/

D d,, ..., db ..., d«,(14)

N n, - n,(15)

где i 1, 2, .... n - номер слова в группе; 1,2, ..., q - номер группы 6 и формируемой величины в каждом слове группы;

S 1, 2, ..., Ь -номер критерия идентификации и соответствующих этому критерию блоков 7, 8; } 1,2, ..., Я, -номер компаратора в

каждом блоке 7;

т,-;- маска, подаваемая в г-ю

группу элементов б И, при обработке i-ro слова группы G;

R/ -набор кодов г/,- отношений сравнения, подаваемый в S-й блок 8 при обработке i-ro слова группы G;

rif - код отношения сравнения, подаваемый в S-й блок 8 для проверки результатов сравнения в J-M компараторе S-ro блока 7 при обработке i-ro слова в группе G; d, - код указателя выбора адресной переменной, подаваемый в регистр 10 при обработке i-ro слова группы G;

n - число слов в группе G. Код г рможет иметь значения, из которых одно, например нуль, указывает на то, что при 1-м слове группы G отношение сравнения для j-ro компаратора в S-м блоке 7 не задано и поэтому результаты сравнения в этом компараторе при обработке i-ro слова группы G должны игнорироваться. Остальные значения кода задают отношения «больше или равно, «меньше или равно, «равно, «не равно.

Код d,- указывает номер одной из переменных, поданных на вход регистра 10; переменная, имеющая номер, указанный кодом d,-, должна быть выбрана регистром 10 в качестве адресной переменной. Например только для одного значения 1, при котором i-e слово группы G передает адресную переменную, а для остальных значений i задано d/ 0.

Набор В может быть представлен в виде кортежа

В Bi, ..., В,, ..., (16)

В, . а« .,, а..., С.(17)

С iaf ..., С ..., С,(18)

где С;-набор констант сравнения, подаваемый в S-й блок 7 при обра ч ботке i-ro слова группы G; С;у - константа сравнения, подаваемая 5 .на вход j-ro компаратора в S-M

блоке 7 при обработке i-ro слова группы.

Набор W контрольных констант может быть представлен в виде кортежа

w v, k,(19)

О где V - совокупность наборов контрольных

масок;

k- набор контрольных кодов для проверки контрольных разрядов входного слова.

Составляющие набора w также могут быть представлены в виде кортежей

v vi, ..., Vb ..., Vn,(20)

k k,, ..., k,, ..., k«.(21)

где i 1,2, ..., n - номер слова в группе G;

V, - маска для выделения

0контрольных разрядов

i-ro слова группы G; k, - контрольный код для проверки контрольных разрядов 1-го слова группы G. Во время этапа подготовки после приема 5 совокупности констант в блок 4 в нем производится чтение набора N констант, и по окончании этого этапа на выходах 24 блока 4 устанавливаются потенциальные сигналы, соответствующие значениям констант из набора. Эти сигналы на выходах 24 блока 4 сохраняются в течение всего этапа обработки. Кроме того, во время этапа подготовки блок 13 устанавливает блоки 3, 8 и 14 в исходное состояние.

По окончании этапа подготовки блок 5 включает блок 13, который вырабатывает на своем выходе сигнал готовности приема слова в регистр 1. Этот сигнал подается в качестве запроса во внещний источник входных слов, например ЭВМ. С этого мо0 мента начинается этап обработки.

На этапе обработки из внешнего источника через вход 2 в регистр 1 поочередно поступают входные слова w,- последовательно подаваемых групп, G каждую из которых можно представить в виде кортежа:

5 G w,, ..., Wb ..., (22)

Все группы G имеют одинаковую длину, равную n словам, и все слова во всех группах имеют одинаковое количество разрядов. Каждое слово w, имеет контрольные и информационные разряды и может быть представлено в виде кортежа:

W, ;, р,,(23)

где 1/ - контрольный код, размещенный в

контрольных разрядах слова w,;

Pi - информационный код, размещенный

в информационных разрядах слова

w,-.

Информационный код представляет значения одной или нескольких переменных

величин. В отличие от таких методов контроля как, например, контроль по паритету или по модулю, код 1, идентифицирует положение слова W, в группе G входных слов и может представлять собой, например, код порядкового номера i слова в группе G. Количество контрольных разрядов зависит от числа п слов в группе G и выбирается (назначается) пользователем в зависимости от решаемой задачи. При этом количество контрольных разрядов в слове может быть зависимо от номера i слова в группе.

Пример. Пусть каждая группа G состоит из четырех входных слов (п 4): , W2, W3, (24)

Тогда наиболее естественным представляется такое распределение контрольных и информационных разрядов, при котором каждое, например, 16-разрядное слово в группе G содержит 2 контрольных и 14 информационных разрядов. При этом, для каждого номера слова могут быть выбраны следующие значения контрольных кодов 1,-:

i 1; 2; 3; 4.

1, 01; 10; 11.

Однако в тех случаях, когда в некотором слове количество информационных разрядов оказывается недостаточным, то может быть использовано переменное количество контрольных разрядов, зависящее от номера слова. Например, в первом слове группы можно назначить один контрольный разряд и 15 информационных разрядов, а в остальных (втором, третьем, четвертом) словах группы иметь по 3 контрольных и 13 информационных разрядов. При этом для каждого номера слова могут быть выбраны следующие значения контрольных кодов I,:

i 1; 2; 3; 4,

1/ (хх) 001; 010; 011, где (хх) - два информационных разряда первого слова, размещенные в позициях, которые используются в остальных словах группы в качестве контрольных разрядов.

В информационных разрядах всех слов в каждой группе одинаково размещен заданный набор величин х, являющийся образом многомерного события. Каждый набор X может быть представлен в виде кортежа кортежей х,-, каждый из которых размещен в одном i-M слове группы G;

X Х|, ..., X,-, ..., Хп,(25)

X,- xi(, ..., х,., ..., х/,,(26)

где ii - 7-я величина в i-м слове группы.

По мере обработки групп входных слов с выхода регистра 12 во внещний приемник, например ЭВМ, поочередно выдаются адреса всех событий идентифицированных в результате обработки очередной группы.

При приеме в регистр 1 очередного слова группы, начиная с первого слова, содержимое счетчика. 3 увеличивается на единицу и на выход 18 выдается код номера этого слова, который в качестве адреса принимается в блок 4 по сигналу блока 13, подаваемому на вход 27 блока 4. По этому адресу в блоке 4 производятся чтение очередных наборов М, , В;, И; констант и очередной 5 константы dj из набора D соответственно на выходы 20, 21, 22 и 23, а также очередных констант V(k,- из наборов v , k на выходы 25. В процессоре обработка и контроль последовательности входных слов ведутся параллельно. Рассмотрим сначала контроль,

который производится следующим образом.

Очередное слово w, группы G с выхода

регистра 1 поступает на вход 55 блока 14.

С выхода 25 блока 4 на вход 93 блока 14

поступают контрольные константы, испольг зуемые для контроля i-ro слова группы. При этом на вход 91 (фиг. 4) поступает контрольная маска V;, а на вход 92 схемы 56 поступает контрольный код k;. группа элементов 54 И формирует из входного слова контролируемую величину 2.1 в соответствии с фор0 мулой

z,(27)

где Л знак поразрядной конъюнкции. Величина z; содержит контрольный код 1, в контрольных разрядах и нули в остальных разрядах. В схеме 56 осуществляется сравнение контрольного кода 1,-, поступающего на вход 92 схемы 56 из блока 4. Если сравниваемые коды не равны, то на выходе 58 схемы 56 появится сигнал «1. Тогда, при появлении контрольного синхроимпульса на входе 65 элемента 61 И на выходе 72 последнего появится сигнал «1, который увеличивает на единицу содержимое счетчиков 70 и 73, устанавливает триггеры 79 и 83 в единичное состояние. Сигнал «О, с выхода 94 триггера 79 через совокупность 39 выходов

г блока 14 поступает в блок 13 и запрещает формирование заявки процессора на прием очередного входного слова в регистр 1. Сигнал «О с выхода 95 триггера 83 с выхода 39 блока 14 поступает в блок 13 и запрещает подачу сигнала «1 из блока 13, а на вход 46

элемента 45 в каждом блоке 8, устанавливая тем самым запрет на формирование импульсов, подсчитываемых в счетчиках 47 при вычислении полных критериев идентификации событий каждого типа. Одновременно с поступлением на входы 80 и 81 триггеров 79, 83

сигнал «1, с выхода 72 элемента поступает в блок 13, где формируются следующие сигналы: сигнал «1 на входе 16 блока 3; сигнал начальной установки на входе 48 счетчика 47 в каждом блоке 8; сигнал «1 на входе 27 блока 4.

При появлении сигнала «1 на входе 16 счетчика 3, содержимое счетчика увеличивается на единицу и становится равным (i -(- 1). По этому адресу в блоке 4 производится чтение очередных наборов констант и очередной константы из набора D соответственно на выходы 20, 21, 22 и 23, а также очередных констант из наборов v и k на выход 25. С выхода 25 блока 4 на вход 23 блока 14 поступают контрольные костанты, используемые для контроля (i + 1) -го слова группы При этом на вход 81 поступает контрольная маска v,+i, а на вход 92 схемы 56 поступает контрольный код. В соответствии с формулой (27) из входного слова формируется величина z,-+i, содержащая контрольный код 1/+|.

Если коды, подаваемые соответственно на входы 59 и 92 схемы 56, окажутся равными, то сигнал «1 появится на выходе 57 схемы 56 и при появлении контрольного синхроимпульса на входе 64 элемента И 60 на выходе этого элемента появляется сигнал «1, который устанавливает начальное значение в счетчике 73 - дополнительный код числа (-п), а также поступает на вход 81 триггера 79 и устанавливает его в нулевое состояние, разрешая тем самым формирование в блоке 13 запроса на прием очередного входного слова.

Таким образом, обработка входных слов группы G продолжается, но полные критерии идентификации событий вычисляться не будут, так как запрет на подачу сигнала «1, из блока 13 на вход 46 в каждом блоке 8 не снят. Этот запрет снимается только в том случае, если сравниваемые в схеме 56 контрольные коды равны и на выходе дешифратора 67 появляется сигнал «1, соответствующий значению i 1 на выходе 18 блока 3.

Если же сравниваемые коды не равны,

то на выходе 58 появляется сигнал «1, и при появлении контрольного синхроимпульса на входе 65 элемента И 61 на выходе 72 этого элемента появляется сигнал «1, который увеличивает на единицу содержимое счетчиков 70 и 73. Запреты, установленные предыдущим сигналом «1,с выхода 72 элемента И 61, сняты не будут. По сигналу «1 с выхода 72 элемента И 61, поступающему в блок 13, в последнем формируются следующие сигналы: сигнал «1 на входе 16 блока 3; сигнал начальной установки на входе 48 счетчика 47 в каждом блоке 8; сигнал «1 на входе 27 блока 4.

При появлении сигнала «1 на входе 16 счетчика 3 содержимое его увеличивается на единицу и становится равным (i+2). Сигнал «1 на входе 27 блока 4 осуществляет прием нового адреса с выхода 18 счетчика 3. По этому адресу в блоке 4 производится чтение очередных наборов констант. Так продолжается до тех пор, пока сравниваемые в схеме 56 коды не окажутся равными, либо на выходе 74 счетчика 73 не появится сигнал переполнения, который увеличивает содержимое счетчика 77 на единицу. Появление этого сигнала свидетельствует о том, что код 1, имеет недопустимое значение, так как не равен ни одному из контрольных кодов. Сигнал с выхода 74 счетчика 73 поступает на вход 82 триггера 79 и устанавливает его

в ноль, снимая тем самым запрет формирования в блоке 13 заявки процессора на прием очередного входного слова в регистр 1. Кроме того, этот сигнал поступает в блок 13, где формируется сигнал «1, который поступает на вход 87 счетчика 73 и устанавливает его в начальное состояние. Одновременно с этим сигнал «1 с выхода 72 элемента И 61 поступает в блок 13, где формируются следующие сигналы: сигнал «1 на входе 16 счетчика 3; сигнал «1 начальной установки на входе 48 счетчика 47 в каждом блоке 8; сигнал «1 на входе 27 блока 4.

После поступления сигнала «1 на вход 16 счетчика 3 содержимое счетчика увеличивается на единицу и становится равным i. С выхода 94 триггера 79 в блоке 14 сигнал «1 поступает в блок 13, где формируется заявка процессора на прием очередного слова в регистр 1. После приема этого слова в регистр 1 из блока 13 на вход 16 счетчика 3 йоступает сигнал «1, в результате чего содержимое счетчика увеличится на единицу. Таки-м- образом, обработка группы слов продолжается.

Рассмотрим теперь обработку последовательности входных слов при отсутствии нарушения порядка размещения входных слов, в их последовательности.

Очередное i-e слово группы G с выхода регистра 1 поступает на входы всех групп элементов И 6. На выходе каждой группы формируется величина х,-;

х// W;Am,v(28)

где Л - знак поразрядной конъюнкции.

При этом маски и, следовательно, величины п в разных группах 6, т. е. при разных значениях индекса j могут быть одинаковыми.

На один вход каждой j-й схемы сравнения в каждом S-M блоке 7 поступает константа С;/с выхода 21 блока 4, а на другой вход этой схемы сравнения поступает переменная величина х,, поступающая с выхода j-ro блока 6. В каждой схеме сравнения каждого блока 7 производится сравнение указанной переменной величины с константой . На выходах каждой схемы сравнения формируются сигналы о выполненных отношениях сравнения. На входы каждого блока .8 поступают выходные сигналы всех схемсравнения в S-M блоке 7 и набор отношений сравнения с выхода 22 блока 4. В каждом блоке 8 при обработке очередного слова группы вычисляется частичный критерий F идентификации и выполняются действия по вычислению полного критерия F идентификации события S-ro типа. Частичный

U г-ет критерии г, вычисляется в соответствии

с формулой.

Р.ДР, (29)

IJ1 J -i

где F,,- - предикат, определенный на i-м слове группы G, на j-й схеме сравнения S-ro блока 7. Если отношение сравнения, заданное кодом r/f из набора Rf, совпадает с результатом сравнения в j-й схеме сравнения S-ro блока 7, то Р 1,в противном случае . После обработки всех h слов группы G на выходе каждого S-ro блока 8 формируется значение полного критерия идентификации в соответствии с формулой „С5)л CS) F РЬ Если критерий идентификации выполняется, то 1, в противном случае . Сигналы с выходов всех блоков 8 подаются на входы элемента 9 и на вход 35 блока 11. Элемент 9 формирует признак р выполнения критериев идентификации (31) Признак р подается в блок 13 и разрешает формирование адреса события если . В противном случае (), адрес события не формируется и обработка очередной группы входных слов на этом заканчивается. Одновременно с передачей величины х,/ в блоки 7 одна из этих величин, например величина х,д из х-й группы 6, поступает на вход 36 регистра 10, а на другой вход этого же блока поступает код. d; с выхода 23 блока 4. Если d,, то по сигналу блока 13, подаваемому на вход регистра 10, последний производит прием величины х,-д. Величина с выхода этого регистра подается на вход 27 блока 11 в качестве адресной переменной j . После обработки п слов каждой группы G блок 11 определяет номер S выполненного критерия идентификации по сигналам, поступающим с выходов блоков 8 и формирует адрес as события из этого номера S и адресной переменной ja, поступающей из регистра 10, например в соответствии с формулой as S, уд.(32) Если признак р на выходе элемента 9 разрешает формирование адреса события (), то блок 13 производит прием адреса as в регистр 12. Выдача адреса из регистра 12 во внешний приемник, например ЭВМ, производится по запросу этого приемника, поступающему на вход 41 блока 13, после приема запрашиваемого адреса в регистр 12. Прием очередного адреса в регистр 12 производится только после выдачи предыдущего адреса из этого регистра во внешний приемник. Прием очередного слова в регистр 1 из внешнего источника производится по запросу блока 13, подаваемому на вход 40 этого блока после того, как обработка предыдущего слова в регистре 1 закончена. Обработка очередного слова в регистре 1 считается законченной либо после приема блоком 13 сигнала с выхода 39 блока 14, либо после приема сигналов с выходов блока 8 и регистра 10 в блок 11, если в нем-на выходах 35 и 37 установлены регистры (не показаны). В последнем случае формирование и выдача адреса из регистра 12 могут быть частично или полностью совмещены во времени с обработкой очередного слова, принятого в регистр 1. В качестве примера рассмотрим более подробно работу блока 13. Перед началом работы процессора, например, после включения питания с помощью узла 97 импульсом, подаваемым по связи 138, производится установка в состояние «О, триггеров 117, 118 в синхронизаторах 98, 99, триггеров 130, 131 в синхронизаторе 124, входящем в узел 116. Кроме того, этим импульсом через элемент ИЛИ 103 производится установка в начальное состояние счетчика 3 и триггеров 113 в блоке 13. Одновременно с этим производится установка в начальное состояние счетчиков 70 и 77, триггеров 79 и 83, а также осуществляется включение блока 5 через выход 30. По окончании приема констант в блок 4, блок 5 вырабатывает на своем выходе 30 сигнал «1 (импульсы), подаваемый в блок 13, в котором по связи 139 через элемент ИЛИ 105 поступает на вход счетчика 47 в каждом блоке 8, устанавливая в этих счетчиках 47 начальное значение (дополнительный код числа -п); через элемент ИЛИ 102 поступает в блок 14 на вход 87 счетчика 73, устанавливая в нем начальное значение (дополнительный код числа п), а через элемент ИЛИ 106 поступает на вход 140 синхронизатора 98 в качестве сигнала-заявки процессора на прием первого слова в регистр 1. Затем после поступления на вход синхронизатора 98 сигнала (импульса)заявки от внешнего источника на прием слова в регистр 1 на выходе 38 синхронизатора 98 появляется сигнал «1 (импульс), осуществляющий прием в регистр 1, а на выходе 40 блока 13 формируется сигнал запроса следующего слова. Отметим, что сигнал «1 на выходе 38 вырабатывается только тогда, когда на входы синхронизатора 98 в любой последовательности или одновременно поступят заявки (фиг. 6). Одновременно с подачей на управляющий вход 38 регистра 1 сигнал «1 (импульс) через элемент ИЛИ 101 поступает на вход распределителя 100, с выхода которого сигнал «1 (импульс) по связи 16 поступает на вход счетчика 3 и увеличивает на единицу его содержимое. На выход 18 счетчика 3 выдается код номера принятого в регистр 1 слова группы. Этот код в качестве адреса принимается в блок 4 через вход 26 по сигналу «1 (импульсу), поступающему с выхода распределителя 100 по связи 27 на вход блока 4. По этому сигналу в блоке 4 производится чтение наборов констант, необходимых для обработки принятого в регистр 1 слова. По прошествии времени, достаточного для выделения в группе 54 элементов И контролируемой величины Z, и сравнения ее с контрольным кодом К, в схеме 56, на выходе распределителя 100 появляется сигнал «1 (импульс), который поступает на входы 64 и 65 элементов 60 и 61 V в блоке 14. Дальнейшая работа блока 13 зависит от того, имеются ли во входной последовательности слов ошибки или нет. Рассмотрим сначала работу блока 13 при отсутствии ошибок в последовательности входных слов, а затем при наличии таких ошибок. По прошествии времени, достаточного для обработки слова в процессоре, на выходе 141 распределителя 100 появляется сигнал «1 (импульс), который через элемент И 111 поступает в регистр 10, осуш,ествляя прием адресной переменной, если d, l, а также во все блоки 8 для формирования импульсов, подсчитываемых в счетчиках 47 при вычислении полных критериев F идентификации (фиг. 2). Кроме того, сигнал «I с выхода 141 распределителя 100 через элементы 112, 106 поступает на вход 140 синхронизатора 98, на выходе которого после прихода сигнала заявки от внешнего источника сформируется сигнал «1 (импульс) приема в регистр 1. Работа блока 13 после приема очередного слова в регистр 1 аналогична рассмотренной выше. Блок 13 работает таким образом до тех пор, пока в регистр 1 не будет принято последнее слово группы. В этом случае, после прихода сигнала «1 (импульс) с выхода 16 распределителя 100 на вход счетчика 3 на выходе 19 этого счетчика появляется сигнал «1 (импульс), который устанавливает триггер 113 в состояние «1, вследствие чего элемент 112 будет закрыт. При этом, после вычисления полных критериев идентификации событий каждого S-ro типа сигнал «1 (импульс) с выхода 142 распределителя 100 через элемент И 108 поступает на вход 143 узла 116, инициирует в нем формирование адреса события в случае выполнения одного из критериев идентификации и вызывает формирование на выходе 144 узла 116 сигнала «1(импульса), который через элементы ПО, 107, 104, 103, 105 устанавливает в начальное состояние счетчик 3, триггер 113, счетчики 47 блоков 8 и через элемент 106 поступает на вход 140 синхронизатора 98 в качестве заявки процессора на прием очередного слова в регистр 1. Узел 116 (фиг. 7) работает следующим образом. Если ни один критерий не выполнен, то на вход 145 узла 116 из элемента 9 поступает потенциальный сигнал «О, вследствие чего по сигналу «1 на входе 143 в узле 116 посредством синхронизатора 124, элементов И 125, ИЛИ 127 формируется сигнал «1 (импульс) на выходе 144. Если выполнен один из критериев F, то на вход 145 узла 116 из элемента 9 поступает потенциальный сигнал «1, вследствие чего по сигналу «1 на входе 143 в узле 116 посредством синхронизатора 124 и элемента И 126 на выходе 146 формируется сигнал «1 (импульс), который производит в блоке 11 формирование адреса. После этого через элемент 129 задержки и элемент ИЛИ 127 формируются сигналы «1 (импульсы) на выходах 147 и 144 узла 116. По сигналу «1 на выходе 147 синхронизатор 99 формирует на выходе 148 сигнал «1 (импульс), осуществляющий прием в регистр 12 адреса из блока 11, после поступления на вход синхронизатора 99 сигнала «1 (импульса) заявки внешнего приемника на выдачу слова из регистра 12 и после этого вырабатывает на выходе управляющий сигнал «1 (импульс), по которому производится выдача адреса из регистра 12 во внешний приемник. При этом сигнал «1 на выходе 148 вырабатывается синхронизатором 99 только тогда, когда на его входы в любой последовательности или одновременно поступят заявки (фиг. 6). Сигнал «1 с выхода 148 синхронизатора 99 поступает на вход синхронизатора 124 узла 116 либо подготавливая формирование сигнала «1 на выходе 149 синхронизатора 124, либо вызывая формирование этого с--- -нала, если на вход 143 уже поступил сигнал «1. Синхронизатор 124 (фиг. 8) работает следующим образом. Сигналом «1 (импульсом) на входе 138 триггеры 130, 131 устанавливаются в исходное состояние «О. Первый сигнал «1 (импульс) на входе 143 устанавливает триггер 130 в состояние «1, вследствие чего по переднему фронту сигнала «1 на выходе элемента И 132 формирователь 136 формирует импульс, который через элемент 137 задержки возвращает триггер 130 в состояние «О и устанавливает триггер 131 в состояние «1 через элемент 133 и если на входе 145 (на выходе элемента 9, фиг. 5) имеется потенциальный сигнал «1, в этом случае следующий сигнал «1 (импульс) на входе 143 установит триггер 130 в состояние «1, но формирование имг ульса формирователем 136 произойдет только после того, как сигнал «1 (импульс) на йходе 148 возвратит триггер 131 в состояние «О. Рассмотрим теперь работу блока 13 при наличии ошибок в последовательности входных слов. При нарушении последовательности поступления входных слов на выходе 58 схемы 56 в блоке 14 (фиг. 4) появится сигнал «1, тогда после появления на вьгходе распределителя 100 сигнала «1 (импульса) этот сигнал поступает на вход 65 элемента И 61, на выходе 72 которого формируется сигнал «1, который увеличивает на единицу содержимое счетчиков 70, 73 и устанавливает триггеры 79, 83 в единичное состояние. Сигналы с выходов 72, 94, 95 элемента 61 и триггеров 79, 83 соответственно через выход 39 блока 14 поступают в блок 13. Сигнал «О

с выхода 94 триггера 79 закрывает элементы 100, 112, запрещая тем самым формирование заявки процессора на прием очередного слова в регистр 1. Сигнал «О с выхода 95 триггера 83 закрывает элемент И 111, запрещая подачу сигнала «1 с выхода 142 распределителя 100 на вход 46 элемента 45 в каждом блоке 8 (фиг. 2) и последующее формирование импульсов, подсчитываемых в счетчиках 47 при вычислении полных критериев идентификации. Сигнал «1 с выхода 72 элемента И 61 через элементы 109, 105 устанавливает счетчики 47 в каждом блоке 8 в исходное состояние. Кроме того, сигнал «1 с выхода 72 элемента И 61 через элемент ИЛИ 101 поступает на вход распределителя 100, с выхода которого сигнал «1 (импульс) по связи 16 поступает на вход счетчика 3 и увеличивает на единицу содержимое счетчика этого блока. Сигнал «1 (импульс), поступающий с выхода распределителя 100 по связи 27 на вход блока 4, осуществляет прием нового адреса с вьЕхода 18 счетчика 3. По этому адресу в блоке 4 производится чтение очередных наборов констант, в том числе и контрольных. Если теперь сравниваемые в схеме 56 коды окажутся равными, то на выходе 57 схемы 56 появится сигнал «1, тогда после появления на выходе распределителя 100 сигнала «1 (импульса) этот сигнал поступит на вход 64 элемента И 60, на выходе которого формируется сигнал «1, который установит начальное значение в счетчике 73 (дополнительный код числа -п), а также установит триггер 79 в состояние «О, вследствие чего элемент И 112 будет открыт для прохождения сигнала «1 с выхода 141 распределителя 100, тем самым запрет формирования заявки процессора на прием очередного слова в регистр 1 будет снят. Таким образом, обработка потока входных слов группы будет продолжаться, но полные критерии идентификации вычисляться не будут, поскольку запрет на подачу сигнала «1 с выхода 141 распределителя 100 на вход 46 элемента 45 в каждом блоке 8 не снят. Этот запрет снимается только в случае, если сравниваемые в схеме 56 коды равны и на выходе дещифратора 67 появится сигнал «1, соответствующий значению на выходе 18 счетчика 3.

Если же сравниваемые в схеме 56 коды не равны, то на выходе 58 появится сигнал «1, и тогда при появлении контрольного

синхроимпульса на входе 65 элемента И 61 на выходе этого элемента появится сигнал «1, который увеличит на единицу содержимое счетчиков 70 и 73. Запреты, установленные предыдущим сигналом «1, с выхода 72 элемента 61 сняты не будут. Сигнал «1. с выхода 72 элемента И 61 через выход 39 блока 14 и через элемент 101 поступает на вход распределителя 100 в блоке 13. С выхода распределителя 100 сигнал «1 (импульс) 0 по связи 16 поступает на вход счетчика 3 и увеличивает содержимое счетчика на единицу. После этого сигнал «1 (импульс) с выхода распределителя 100, поступающий по связи 27 на вход блока 4, осуществляет прием нового адреса. По этому адресу в блоке 4 производится чтение очередных наборов констант, в том числе контрольных констант. Затем в схеме 56 производится сравнение кодов.

0 Так будет продолжаться до тех riop, пока сравниваемые в схеме 56 коды не окажутся равными, либо на выходе 74 счетчика 73 не появится сигнал переполнения, который увеличит содержимое счетчика 77 на единицу, а через элемент 115 задержки и элемент

5 ИЛИ 102 блока 13 установит в счетчике 73 блока 14 начальное значение (дополнительный код числа -п). Кроме того, сигнал с выхода 74 счетчика 73 устанавливает триггер 79 в состояние «О, снимая тем самым запрет формирования заявки процессора на прием очередного слова в регистр 1.

Конец прогона последовательности входных слов определяется внещним источником констант, например ЭВМ (не показан), подключенным к входам/выходам 29 блока 5

и управляющей работой процессора. По окончании прогона по запросу этого внещнего источника содержимое счетчиков 70 и 77 через выход 96 блока 14 подается на вход 31 блока 5 и далее в указанный внещний источник констант для последующего вывода

0 и анализа. В частности, по содержимому

счетчиков 70 и 77 можно оценить количество

Q пропущенных слов в последовательности

Q S-пА,(33)

где S - содержимое счетчика 70, равное

числу несовпадений кодов в схеме 56;

А-содержимое счетчика 77, равное

числу входных слов с недопустимыми

значениями контрольных разрядов;

п - количество слов в группе G.

1

40

I

HI

42

J2

/

f

::.i52

tг

(L

и И Ш

52

t9

4

in

гп I

5L

J

фиг.З (риг.Б

tpui.a

фи&.9 / 116

11

Hf6

(риг.Ю

J7

3,

с...

II L

/

151

ZZI

t регистру 12 Фи.ц

| Нехай А | |||

| Л., Наканоров А | |||

| Г | |||

| Применение цифровых дискриминаторов при многомерном анализе в централизованной системе сбора и обработки физической информации | |||

| Труды седьмой конференции по ядерной электронике, т | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Видоизменение прибора с двумя приемами для рассматривания проекционные увеличенных и удаленных от зрителя стереограмм | 1919 |

|

SU28A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 913388, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1983-04-04—Подача