1

Изобретение относится к аналоговой вычислительной технике и может быть использовано для решения широкого класса задач исследования систем автоматического регулирования (САР) на аналоговых вычислительных машинах и непосредственно в САР для организации аналогового управления, контроля и цепей обратной связи.

Цель изобретения - повышение точности и быстродействия устройства при интегрировании импульсных сигналов .

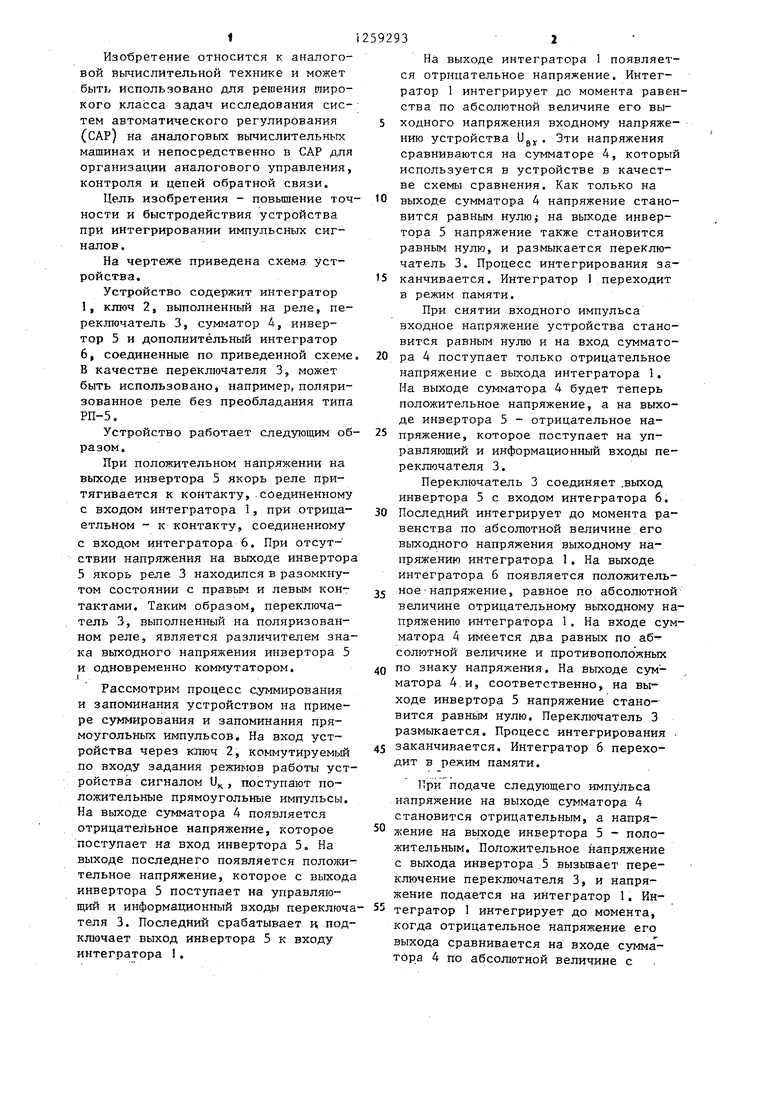

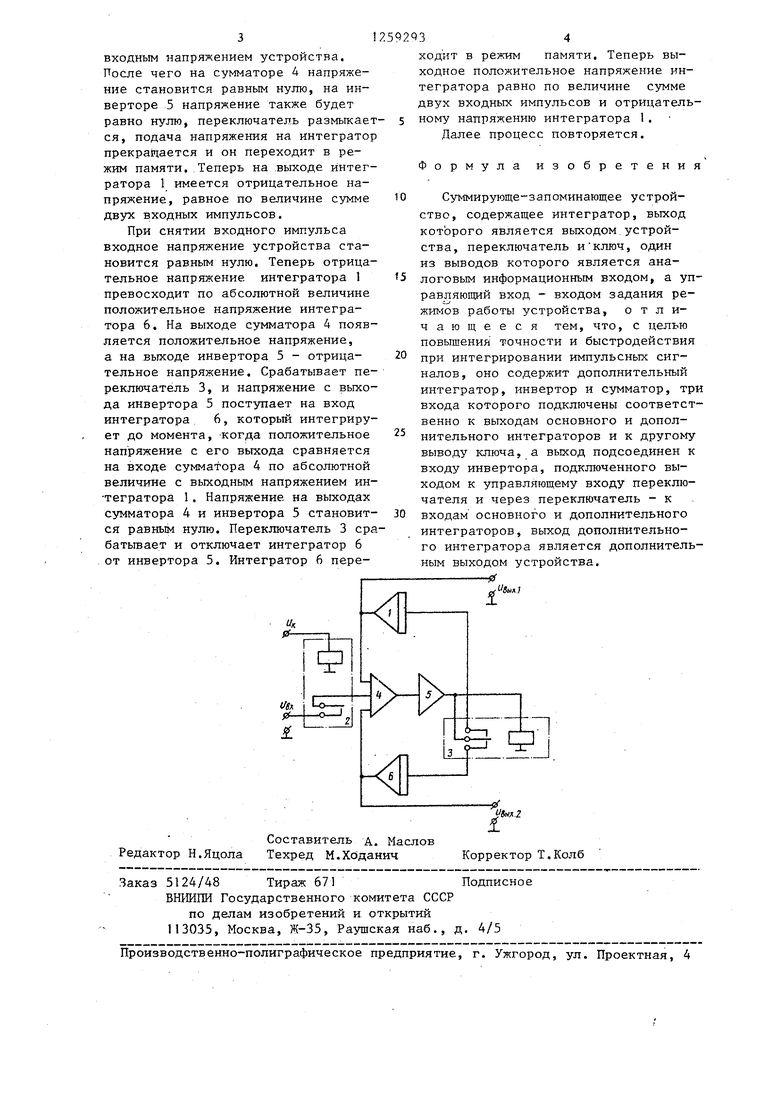

На чертеже приведена схема устройства.

Устройство содержит интегратор 1, ключ 2, выполненный на реле, переключатель 3, сумматор 4, инвертор 5 и дополнительный интегратор 6, соединенные по приведенной схеме В качестве переключателя 3, может быть использовано, например, поляризованное реле без преобладания типа РП-5.

Устройство работает следующим образом.

При положительном напряжении на выходе инвертора 5 якорь реле притягивается к контакту, .соединенному с входом интегратора 1, при отрица- етльном - к контакту, соединенному с входом интегратора 6. При отсутствии напряжения на выходе инвертора 5 якорь реле 3 находился в разомкнутом состоянии с правым и левым контактами. Таким образом, переключатель 3, выполненный на поляризованном реле, является различителен знака выходного напряжения инвертора 5

и одновременно коммутатором.

.1

Рассмотрим процесс суммирования и запоминания устройством на примере суммирования и запоминания прямоугольных импульсов. На вход устройства через кзтюч 2, ко -гмутируемый по входу задания режимов работы устройства сигналом Уц, поступают положительные прямоугольные импульсы. На выходе сумматора 4 появляется отрицательное напряжение, которое поступает на вход инвертора 5„ На выходе последнего появляется положительное напряжение, которое с выхода инвертора 5 поступает на управляющий и информационный входы переключа теля 3. Последний срабатывает к подключает выход инвертора 5 к входу интегратора 1.

59293 2

На выходе интегратора 1 появляется отрицательное напряжение. Интегратор 1 интегрирует до момента равенства по абсолютной величине его вы5 ходного напряжения входному напряжению устройства Ug, Эти напряжения сравниваются на сумматоре 4, который используется в устройстве в качестве схемы сравнения. Как только на

О выходе сумматора 4 напряжение становится равным нулю; на выходе инвертора 5 напряжение также становится равным нулю, и размыкается переключатель 3, Процесс интегрирования заtS канчивается. Интегратор 1 переходит в режим памяти.

При снятии входного импульса входное напряжение устройства становится равным нулю и на вход суммато20 ра 4 поступает только отрицательное напряжение с выхода интегратора 1. На выходе сумматора 4 будет теперь положительное напряжение, а на выходе инвертора 5 - отрицательное на25 пряжение, которое поступает на управляющий и информационный входы переключателя 3.

Переключатель 3 соединяет .выход инвертора 5 с входом интегратора 6,

30 Последний интегрирует до момента равенства по абсолютной величине его выходного напряжения выходному напряжению интегратора 1. На выходе интегратора б появляется положитель35 ноенапряжение, равное по абсолютной величине отрицательному вьпсодному напряжению интегратора 1, На входе сумматора 4 имеется два равных по аб- солютной величине и противоположных

40 по знаку напряжения. На выходе сумматора 4. и, соответственно, на выходе инвертора 5 напряжение становится paBHfsiM нулю. Переключатель 3 размыкается. Процесс интегрирования .

45 заканчивается. Интегратор 6 переходит в режим памяти.

1Три подаче следующего импульса напряжение на выходе сумматора 4 становится отрицательным, а напря- жение на выходе инвертора 5 - положительным. Положительное напряжение с выхода инвертора :5 вызывает переключение переключателя 3, и напряжение подается на интегратор 1. Ин- 55 тегратор 1 интегрирует до момента, когда отрицательное напряжение его выхода сравнивается на входе суМма - тора 4 по абсолютной величине с

3

входным напряжением устройства. После чего на сумматоре 4 напряжение становится равным нулю, на инверторе 5 напряжение также будет равно нулю, переключатель размыкает ся, подача напряжения на интегратор прекра1чается и он переходит в режим памяти. Теперь на выходе интегратора 1 имеется отрицательное напряжение, равное по величине сумме двух входных импульсов.

При снятии входного импульса входное напряжение устройства становится равным нулю. Теперь отрицательное напряжение интегратора 1 превосходит по абсолютной величине положительное напряжение интегратора 6. На выходе сумматора 4 появляется положительное напряжение, а на выходе инвертора 5 - отрицательное напряжение. Срабатывает переключатель 3, и напряжение с выхода инвертора 5 поступает на вход интегратора 6, который интегрирует до момента, когда положительное напряжение с его выхода сравняется на входе сумматора 4 по абсолютной величине с выходным напряжением ин- тегратора 1. Напряжение на выходах сумматора 4 и инвертора 5 становится равным нулю. Переключатель 3 сра батьтает и отключает интегратор 6 от инвертора 5. Интегратор 6 переРедактор Н.Яцола

Составитель д. Маслов Техред М.Ходанич

2592Q34

ходит в режим памяти. Теперь выходное положительное напряжение интегратора равно по величине сумме двух входных импульсов и отрицатель 5 ному напряжению интегратора 1. Далее процесс повторяется.

Формула изобретения

Суммирующе-запоминающее устройство, содержащее интегратор, выход которого является выходом устройства, переключатель и ключ, один из выводов которого является аналоговым информационным входом, а управляющий вход - входом задания режимов работы устройства, отличающееся тем, что, с целью повышения точности и быстродействия при интегрировании импульсных сигналов , оно содержит дополнительный интегратор, инвертор и сумматор, три входа которого подключены соответственно к выходам основного и дополнительного интеграторов и к другому выводу ключа, а выход подсоединен к входу инвертора, подключенного выходом к управляющему входу переключателя и через переключатель - к

входам основного и дополнительного интеграторов, выход дополнительного интегратора является дополнительным выходом устройства.

fS

«WA.;

Корректор Т.Колб

Заказ 5124/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Модель частотно-импульсного модулятора | 1977 |

|

SU651365A1 |

| Функциональное интегрирующее устройство | 1977 |

|

SU732903A1 |

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1628204A1 |

| Гибридное интегрирующее устройство | 1985 |

|

SU1418768A1 |

| I ВСГГСО'ЭЗНЛЯ I ДИСКРЕТНО-АНАЛОГОВЫЙ ИНТЕГРАТОР]|]ДТГ[{Т! Л :'Тк;^;Г v-^:^ | 1973 |

|

SU370614A1 |

| Интегрирующее устройство | 1983 |

|

SU1267439A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

| Интегратор | 1978 |

|

SU744628A2 |

| Фазовый дискриминатор | 1974 |

|

SU495757A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для решения широкого класса задач исследования систем автоматического регулирования для организации аналогового управления, контроля и цепей обратной связи. Цель изобретения - повышение точности и быстродействия устройства при интегрировании импульсных сигналов. Устройство содержит интегратор-, ключ, переключатель, сумматор, инвертор и дополнительный интегратор. Достижение поставленной цели обеспечено благодаря введению в устройство дополнительного интегратора, инвертора и сумматора и новым связям между составными элементами. 1 ил. & (Л

| 0 |

|

SU154679A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналоговое запоминающее устройство | 1972 |

|

SU484565A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-23—Публикация

1984-12-18—Подача