Изобретение относится к устройствам автоматики и вычислительной техники, а более конкретно - к преобразователям кодов, и может быть использовано, например, в преобразователях “перемещение-код” приводов контрольно-измерительных систем.

Известны преобразователи кода Грея в параллельный двоичный код, содержащие распределитель импульсов, триггер, регистр, логические элементы И, ИЛИ и элементы задержки [1, 2, 3].

Особенностью работы устройства [1] является то, что исходное состояние его триггера безразлично, а перед преобразованием кодов производится перевод за один такт младшего разряда регистра в то же состояние, что и у триггера.

Недостатком данного устройства является его низкое быстродействие. Для преобразования m чисел, каждый из которых представлен в n-разрядном коде Грея, требуется не менее m(n+3) тактов (с учетом такта выдачи информации с регистра).

Особенностью работы устройства [2] является то, что установочный вход триггера и установочные входы всех разрядов регистра, включая установочный вход его младшего разряда, соединены вместе и подключены к соответствующему выходу распределителя импульсов. В итоге перед преобразованием каждого очередного числа в коде Грея производится установка триггера и всех разрядов регистра, включая его младший разряд, в исходное состояние “0”.

Недостатком данного устройства также является его низкое быстродействие. Для преобразования m чисел, каждый из которых представлен в n-разрядном коде Грея, требуется m(n+1) тактов.

Алгоритм преобразования кодов, реализованный в устройстве [3], требует предварительной установки младшего разряда регистра в то же состояние, что и состояние триггера. В процессе такой установки, для предотвращения несанкционированной выдачи кода на выход устройства, осуществляется блокировка элементов И первой и второй групп. А это требует, в свою очередь, постоянной поддержки в процессе преобразования кодов высокого потенциала на пятых и шестых входах этих элементов И. Очевидно, что незначительные сбои в работе блокирующего триггера, блокирующего элемента и третьего элемента задержки могут приводить к нестабильной работе элементов И первой и второй групп. Это, в конечном счете, снижает устойчивую работу преобразователя, а, следовательно, надежность и достоверность преобразования кодов.

Наиболее близким изобретением к предлагаемому по технической сущности и схемному решению является преобразователь кода Грея в параллельный двоичный код, описанный в [4].

Такой преобразователь, выбранный в качестве прототипа, содержит распределитель импульсов, установочный и тактовый входы которого являются соответственно установочным и тактовым входами преобразователя, информационные элементы И, первые входы которых подключены к записывающим выходам распределителя импульсов, регистр, информационные входы разрядов которого, кроме младшего разряда, соединены с выходами информационных элементов И, элементы И-ИЛИ, первые и вторые входы которых подключены соответственно к прямому и инверсному выходам разрядов регистра, а выходы являются разрядными выходами преобразователя, триггер, счетный вход которого является информационным входом преобразователя, установочный вход объединен с установочным входом преобразователя, а прямой выход соединен со вторыми входами информационных элементов И, первый и второй управляющие элементы И, первые входы которых подключены соответственно к прямому и инверсному входам триггера, вторые входы - к считывающему выходу распределителя импульсов, а выходы - соответственно к третьему и четвертому входам элементов И-ИЛИ, первый и второй элементы ИЛИ, выход первого из которых соединен с установочными входами разрядов регистра, кроме младшего разряда, и первый и второй элементы задержки, выходы которых подключены к первым входам соответственно первого и второго элементов ИЛИ, а входы - к выходам соответственно первого и второго управляющих элементов И, при этом вторые входы первого и второго элементов ИЛИ соединены соответственно с выходом второго элемента ИЛИ и установочным входом преобразователя.

В таком устройстве преобразование кодов основано на последовательном сложении по модулю два (mod 2) разрядов кода Грея, начиная с младшего разряда. Согласно алгоритма преобразования вначале формируется промежуточный код по следующему правилу:

pi+1=pi+bi,

где pi, рi+1 - разряды промежуточного кода,

bi -разряд кода Грея,

+ - знак сложения по mod 2.

Если число в коде Грея нечетно, двоичный код образуется как обратный код промежуточного кода, если же четно - разряды промежуточного кода передаются на выход без инвертирования.

К этому следует добавить, что значение младшего разряда двоичного кода также определяется четностью-нечетностью преобразуемого кода Грея. Если сумма по mod 2 разрядов кода Грея равна “1”, то младший разряд равен “1”. Если же эта сумма равна “0”, то и младший разряд двоичного кода равен “0”.

В устройстве промежуточный код формируется в разрядах регистра, сумма по mod 2 - в триггере.

Процесс преобразования завершается установкой младшего разряда регистра в то же состояние, в котором находится триггер.

Наиболее ненадежным звеном в таком алгоритме преобразования является периодически повторяющаяся операция установки триггера и младшего разряда регистра в одинаковое состояние путем передачи информации от триггера к этому разряду.

Очевидно, что любая “лишняя” операция усложняет работу устройства, увеличивает вероятность ошибок преобразования и, как следствие, снижает надежность и достоверность преобразования кодов.

Предлагаемым изобретением решается задача повышения достоверности и надежности преобразования кодов путем исключения необходимости передачи информации от триггера к младшему разряду, а также снижения количества используемых в преобразователе элементов и связей между ними.

Для достижения указанного технического результата в преобразователе кода Грея в параллельный двоичный код, содержащем распределитель импульсов, установочный и тактовый входы которого являются соответственно установочным и тактовым входами преобразователя, информационные элементы И, первые входы которых подключены к записывающим выходам распределителя импульсов, регистр, информационные входы разрядов которого соединены с выходами информационных элементов И, элементы И-ИЛИ, первые и вторые входы которых подключены соответственно к прямому и инверсному выходам разрядов регистра, а выходы являются выходами разрядов преобразователя, кроме младшего разряда, триггер, счетный вход которого является информационным входом преобразователя, а прямой выход соединен со вторыми входами информационных элементов И, управляющий элемент И, первый и второй входы которого подключены соответственно к прямому выходу триггера и считывающему выходу распределителя импульсов, элемент ИЛИ, выход которого соединен с установочными входами разрядов регистра, и элемент задержки, выход которого подключен к первому входу элемента ИЛИ, а вход соединен с третьими входами элементов И-ИЛИ, причем считывающий выход распределителя импульсов подключен ко входу элемента задержки и к третьим и четвертым входам элементов И-ИЛИ, пятый и шестой входы которых соединены соответственно с прямым и инверсным выходами триггера, установочный вход которого подключен к выходу элемента ИЛИ, второй выход которого объединен с установочным входом преобразователя, при этом выход управляющего элемента И является выходом младшего разряда преобразователя.

Основными признаками, отличающими предлагаемое устройство от прототипа, являются:

- подключение считывающего выхода распределителя импульсов ко входу элемента задержки и к третьим и четвертым входам элементов И-ИЛИ,

- соединение пятого и шестого входов элементов И-ИЛИ соответственно с прямым и инверсным выходами триггера,

- подключение установочного входа триггера к выходу элемента ИЛИ, второй вход которого объединен с установочным входом преобразователя,

- принятие в качестве выхода младшего разряда преобразователя выход управляющего элемента И.

Наличие указанных признаков в заявляемом устройстве обеспечивает его соответствие условию патентоспособности “новизна”. При этом сравнение заявляемого устройства не только с прототипом, но и с другими техническими решениями в данной и смежных областях техники показало, что последние не содержат признаков, сходных с признаками, отличающими заявляемое техническое решение от прототипа.

Новая совокупность существенных признаков устройства исключает необходимость передачи значения триггера в регистр после каждого преобразования кода Грея в двоичный код, снижает количество используемых в преобразователе элементов и связей между ними, что, в итоге, обеспечивает повышение надежности и достоверности преобразования кодов.

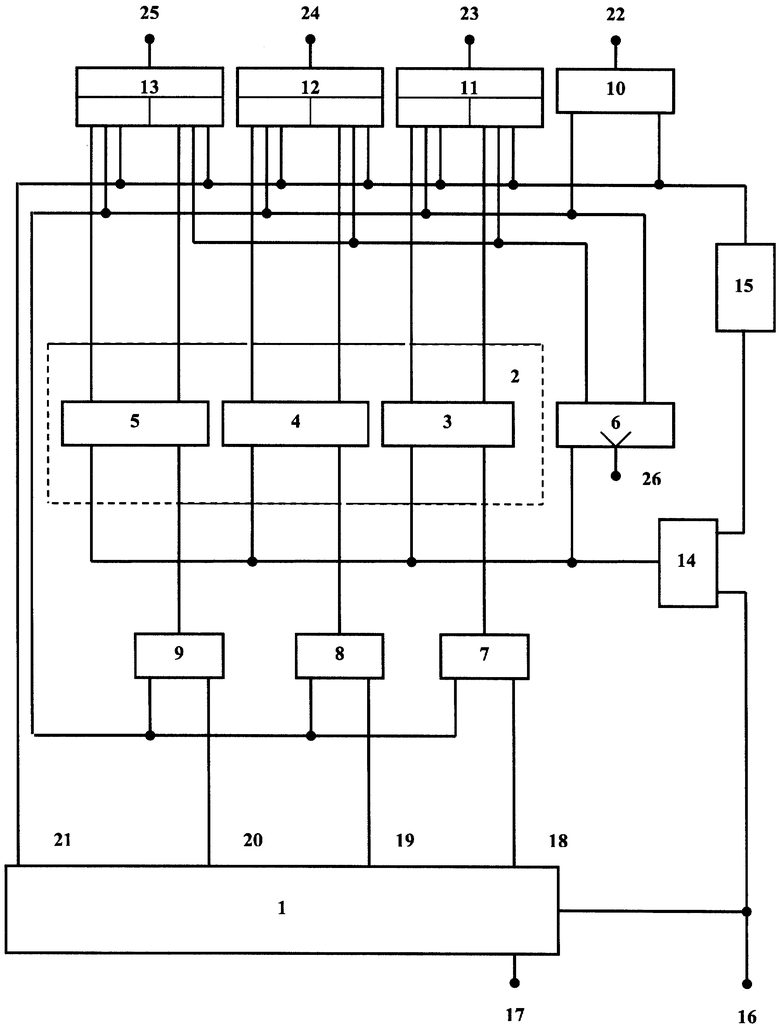

Структурная схема преобразователя четырехразрядного кода Грея в параллельный двоичный код, выполненная согласно данному изобретению, приведена на чертеже.

Устройство содержит распределитель 1 импульсов, регистр 2 с разрядами 3-5, триггер 6, информационные 7-9 и управляющий 10 элементы И, элементы 11-13 И-ИЛИ, элемент 14 ИЛИ и элемент 15 задержки.

Установочный и тактовый входы распределителя 1 импульсов являются соответственно установочным 16 и тактовым 17 входами преобразователя.

Первые входы информационных элементов 7-9 И подключены соответственно к записывающим выходам 18-20 распределителя 1 импульсов, вторые входы - к прямому выходу триггера 6, а выходы соединены соответственно с информационными входами разрядов 3-5 регистра 2.

Прямой и инверсный выходы разрядов 3-5 регистра 2 подключены соответственно к первому и второму входам элементов 11-13 И-ИЛИ, третьи и четвертые входы которых соединены со считывающим выходом 21 распределителя 1.

Выход управляющего элемента 10 И и выходы элементов 11-13 И-ИЛИ являются соответственно выходом 22 младшего и выходами 23-25 старших разрядов преобразователя.

Прямой и инверсный выходы триггера 6 подключены соответственно к пятому и шестому входам элементов 11-13 И-ИЛИ, а прямой выход указанного триггера 6 соединен дополнительно с первым входом элемента 10 И, второй вход которого подключен к считывающему выходу 21 распределителя 1 импульсов.

Вход элемента 15 задержки соединен со считывающим выходом 21 распределителя импульсов, а выход - с первым входом элемента 14 ИЛИ, второй вход которого объединен с установочным входом 16 преобразователя. Выход элемента 14 ИЛИ подключен к установочным входам разрядов 3-5 регистра 2 и установочному входу триггера 6, счетный вход которого является информационным входом 26 преобразователя.

Согласно выполняемым функциям каждый из элементов 11-13 - это элемент 3-2И-ИЛИ. Конструктивно управляющий элемент 10 И и элементы 11-13 И-ИЛИ могут быть реализованы на основе одной интегральной микросхемы.

Варианты выполнения схемы распределителя 1 импульсов могут быть самыми разными. Общим для них будет то, что они обеспечивают появление на своих выходах определенной последовательности управляющих (тактовых) импульсов.

Устройство работает следующим образом.

Пусть требуется преобразовать четырехразрядные коды Грея 1101 и 1011, поступающие на информационный вход 26 преобразователя последовательно младшими разрядами вперед.

Перед началом преобразования с внешнего по отношению к данному преобразователю устройства (на чертеже не показано) на установочный вход 16 подается импульс установки преобразователя в исходное состояние. По этому импульсу распределитель 1 импульсов, триггер 6 и разряды 3-5 регистра 2 устанавливаются в исходное состояние “0”.

В следующий момент времени с внешнего устройства на вход 17 преобразователя подается тактовый импульс. Одновременно с ним на информационный вход 26 преобразователя поступает сигнал первого (младшего) разряда кода Грея, равный в данном случае “1”. В результате этот триггер 6 переходит в единичное состояние. Задержанный на время этой записи тактовый импульс появляется на “первом” выходе 18 распределителя 1 и через подготовленный элемент 7 И поступает на информационный вход разряда 3, записывая в него также “1”.

Второй тактовый импульс аналогичным образом поступает на вход 17 преобразователя. Одновременно с ним на вход 26 преобразователя поступает сигнал второго разряда кода Грея. Но так как он равен “0”, состояние триггера 6 не меняется и он сохраняет свое значение “1”. Задержанный тактовый импульс со “второго” выхода 19 распределителя 1 через подготовленный элемент 8 И поступает на информационный вход разряда 4, записывая в него “1”.

Третий тактовый импульс, аналогично указанному выше, поступает на вход 17 преобразователя. Одновременно с ним на вход 26 преобразователя поступает сигнал третьего разряда кода Грея, равный “1”. В результате этого триггер 6 переходит в противоположное состояние (состояние “0”), а задержанный на время этой записи тактовый импульс появляется на “третьем” выходе 20 распределителя 1. Однако, так как триггер 6 теперь находится в “0”, этот тактовый импульс не проходит через элемент 9 И и разряд 5 регистра 2 сохраняет исходное состояние “0”.

Четвертый тактовый импульс и четвертый (старший) разряд кода Грея, равный “1”, поступают аналогичным образом соответственно на входы 17 и 26 преобразователя. В результате триггер 6 переходит в состояние “1”, а задержанный на время этой записи тактовый импульс появляется на “нулевом” выходе 21 распределителя 1 и поступает на второй вход элемента 10 И, на третьи и четвертые входы элементов 11-13 И-ИЛИ и на вход элемента 15 задержки. В результате этого импульсы появляются на выходах 25 и 22 преобразователя, что соответствует считыванию с преобразователя параллельного двоичного кода 1001.

Импульс, задержанный на элементе 15 на время считывания информации с разрядов 3-5 регистра 2 и триггера 6, через элемент 14 ИЛИ поступает на установочный вход триггера 6 и установочные входы разрядов 3-5 регистра 2, устанавливая их все в состояние “0”.

Пятый тактовый импульс, аналогично указанному выше, поступает на вход 17 преобразователя. Одновременно на вход 26 преобразователя поступает первый разряд следующего кода Грея, равный “1”, который переводит триггер 6 в состояние “1”. Задержанный на время этой записи тактовый импульс появляется на “первом” выходе 18 преобразователя 1 и через подготовленный элемент 7 И записывает “1” в разряд 3 регистра 2.

Шестой тактовый импульс и второй разряд кода Грея, равный “1”, поступают одновременно на входы 17 и 26 преобразователя. В результате триггер 6 переходит в состояние “0”, а задержанный тактовый импульс с выхода 19 распределителя 1 не проходит через неподготовленный элемент 8 И и разряд 4 регистра 2 сохраняет исходное состояние “0”.

Седьмой тактовый импульс и очередной разряд кода Грея поступают одновременно на входы 17 и 26 преобразователя. Но так как третий разряд кода Грея равен “0”, триггер 6 сохраняет свое значение “0”, и задержанный тактовый импульс с выхода 20 распределителя 1 не проходит через неподготовленный элемент 9 и разряд 5 регистра 2 сохраняет свое исходное состояние “0”,

Восьмой тактовый импульс и четвертый разряд кода Грея поступают одновременно на входы 17 и 26 преобразователя. Так как четвертый разряд кода Грея равен “1”, триггер переходит в состояние “1”, а задержанный тактовый импульс со считывающего выхода 21 проходит на выходы 25, 24 и 22 преобразователя, что соответствует считыванию с преобразователя параллельного двоичного кода 1101.

Импульс, задержанный на элементе 15, аналогично вышеизложенному, возвращает триггер 6 и разряды 3-5 регистра 2 в исходное состояние “0”, подготавливая тем самым устройство к преобразованию следующего кода Грея.

Таким образом, благодаря организации новых связей между элементами преобразователя обеспечивается:

- выполнение триггером дополнительно функции младшего разряда регистра прототипа,

- съем значений младшего разряда двоичного кода с той “точки” схемы преобразователя, в котором формируется сигнал, соответствующий четности-нечетности преобразуемого кода Грея,

- установка триггера перед каждым преобразованием кода Грея в необходимое исходное состояние “0”,

- снижение количества используемых в преобразователе элементов и связей между ними.

В итоге указанное позволяет повысить надежность и достоверность преобразования кодов. При этом новая совокупность существенных признаков предлагаемого устройства для специалиста явным образом не следует из уровня техники, обеспечивая тем самым его соответствие условию патентоспособности “изобретательский уровень”.

Описанный преобразователь предполагается использовать в преобразователях “перемещение-код” приводов контрольно-измерительных систем, что обеспечивает соответствие заявляемого технического решения условию патентоспособности “промышленная применимость”.

ИСПОЛЬЗОВАННЫЕ ИСТОЧНИКИ.

1. Авт. св. СССР №431512 по кл. G 06 F 5/02. Устройство для преобразования кода Грея в параллельный двоичный код. БИ, 1974, №21.

2. Авт. св. СССР №788104 по кл. G 06 F 5/02. Преобразователь кода Грея в параллельный двоичный код. БИ, 1980, №46.

3. Авт. св. СССР №1070541 по кл. G 06 F 5/02. Преобразователь кода Грея в параллельный двоичный код. БИ, 1984, №4.

4. Авт. св. СССР №1784963 по кл. G 06 F 5/00, Н 03 М 7/16. Преобразователь кода Грея в параллельный двоичный код. БИ, 1992, №48 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода Грея в параллельный двоичный код | 1990 |

|

SU1784963A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1982 |

|

SU1070541A1 |

| Преобразователь кода грея в параллельный двоичный код | 1978 |

|

SU788104A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Преобразователь кодов | 1985 |

|

SU1259494A1 |

| Преобразователь прямого кода в обратный | 1982 |

|

SU1032448A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1985 |

|

SU1275777A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

| Преобразователь кода грея в двоичный код | 1977 |

|

SU658556A1 |

Изобретение относится к устройствам автоматики и вычислительной техники, и может быть использовано, например, в преобразователях “перемещение-код” приводов контрольно-измерительных систем. Техническим результатом является повышение достоверности и надежности преобразования кодов путем исключения необходимости передачи информации от триггера к младшему разряду, а также снижение количества используемых в преобразователе элементов и связей между ними. Указанный результат достигается за счет того, что преобразователь содержит распределитель импульсов, регистр, триггер, информационные и управляющий элемент И, элементы И-ИЛИ, элементы ИЛИ и элемент задержки. 1 ил.

Преобразователь кода Грея в параллельный двоичный код, содержащий распределитель импульсов, установочный и тактовый входы которого являются соответственно установочным и тактовым входами преобразователя, информационные элементы И, первый входы которых подключены к записывающим выходам распределителя импульсов, регистр, информационные входы разрядов которого соединены с выходами информационных элементов И, элементы И-ИЛИ, первые и вторые входы которых подключены соответственно к прямому и инверсному выходам разрядов регистра, а выходы являются выходами разрядов преобразователя, кроме младшего разряда, триггер, счетный вход которого является информационным входом преобразователя, а прямой выход соединен со вторыми входами информационных элементов И, управляющий элемент И, первый и второй входы которого подключены соответственно к прямому выходу триггера и считывающему выходу распределителя импульсов, элемент ИЛИ, выход которого соединен с установочными входами разрядов регистра, и элемент задержки, выход которого подключен к первому входу элемента ИЛИ, а вход соединен с третьими входами элементов И-ИЛИ, отличающийся тем, что считывающий выход распределителя импульсов подключен ко входу элемента задержки и к третьим и четвертым входам элементов И-ИЛИ, пятый и шестой входы которых соединены соответственно с прямым и инверсным выходами триггера, установочный вход которого подключен к выходу элемента ИЛИ, второй вход которого объединен с установочным входом преобразователя, при этом выход управляющего элемента И является выходом младшего разряда преобразователя.

| Преобразователь кода Грея в параллельный двоичный код | 1990 |

|

SU1784963A1 |

| SU 431512 A, 05.06.1974 | |||

| Преобразователь кода грея в параллельный двоичный код | 1978 |

|

SU788104A1 |

| Преобразователь кода Грея в параллельный двоичный код | 1982 |

|

SU1070541A1 |

Авторы

Даты

2005-03-10—Публикация

2003-05-21—Подача