(54) ПРЕОБРАЗОВАТЕЛЬ КОДОВ ИЗ СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ДВОИЧНБ1Й ПОЗИЦИОННБ1Й КОД

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь полиадического кодаВ КОд СиСТЕМы ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU809154A1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| Преобразователь кода из системы остаточных классов в позиционный код | 1978 |

|

SU744549A1 |

| Обратимый преобразователь двоичных кодов в код системы остаточных классов | 1983 |

|

SU1141398A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ЧИСЕЛ ИЗ КОДА СИСТЕМЫ ОСТАТОЧНЫХ КЛАССОВ В ПОЛИАДИЧЕСКИЙ КОД | 2001 |

|

RU2187886C1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Преобразователь двоичного кода в модулярный код | 1985 |

|

SU1267624A1 |

| Преобразователь кода системы остаточных классов в двоичный код | 1983 |

|

SU1133669A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ЧИСЛА В МОДУЛЯРНОМ КОДЕ НА ОСНОВАНИЕ СИСТЕМЫ СЧИСЛЕНИЯ | 2002 |

|

RU2237274C2 |

| Преобразователь непозиционного кода в двоичный код | 1988 |

|

SU1578810A1 |

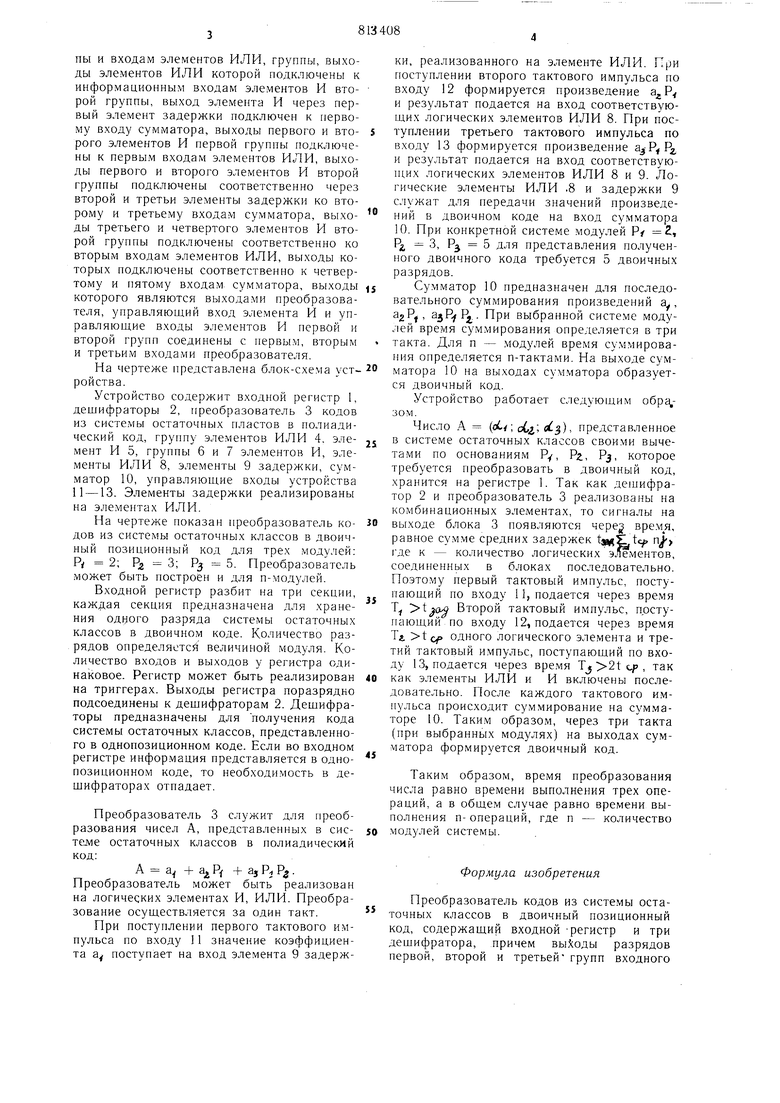

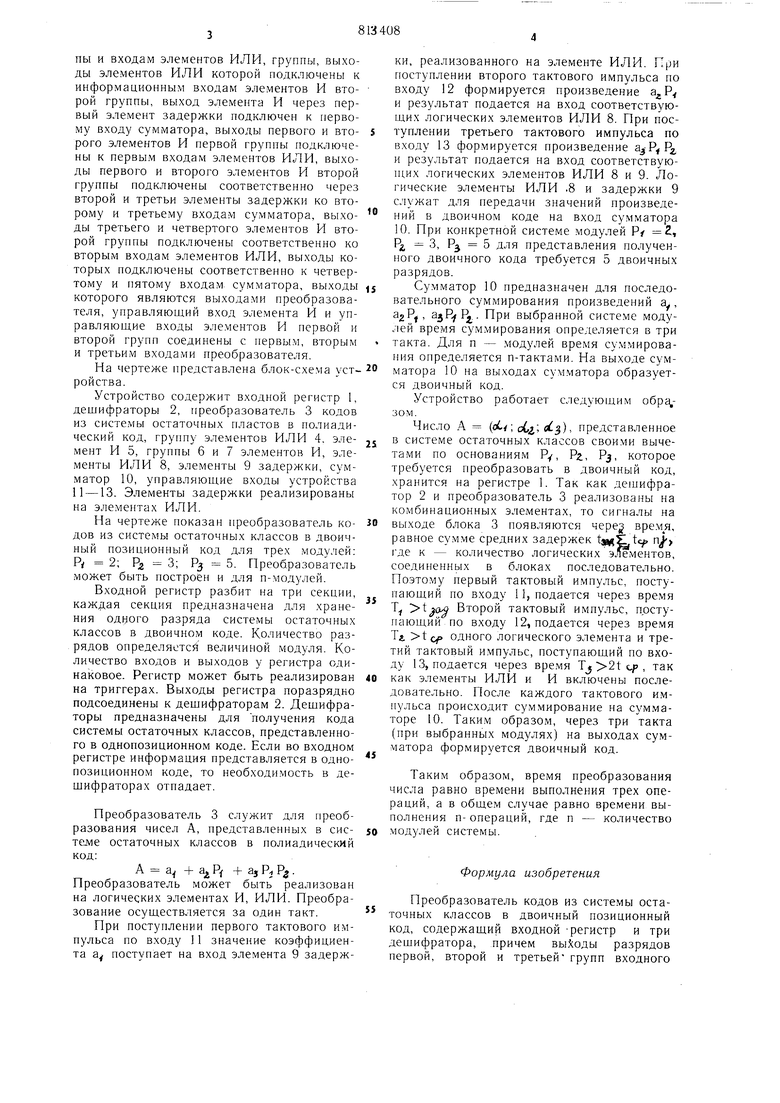

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах для перевода чисел, закодированных в системе остаточных классов, в двоичную позиционную систему счисления. Известен преобразователь кодов из системы остаточных классов в позиционный код, содержащий входной и выходной регистры, пирамиду сумматоров, блок хранения констант по каждому модулю и формирователи переносов 1. Недостатком известного устройства является большой объем оборудования, приходящийся на один модуль. Из известных преобразователей кодов из системы остаточных классов в позиционный код наиболее близким к предлагаемому является преобразователь кодЬв из системы остаточных классов в позиционный код, содержащий входной регистр и три дешифратора, причем выходы разрядов первой, второй и третьей групп входного регистра подключены ко входам соответствующих дешифраторов, преобразователь кода, выходной регистр, блок начальных условий, блок СДВИГОВЫХ регистров, блок сравнения, счетчик и блок управления 2. Недостатком данного преобразователя является низкое быстродействие и большой объем оборудования. Цель изобретения - повышение быстродействия и уменьшение объема оборудования. Поставленная цель достигается тем, что в известный преобразователь, содержащий входной регистр и три дешифратора, причем выходы разрядов первой, второй и третьей групп входного регистра подключены ко входам соответствующих дешифраторов, дополнительно введены преобразователь кодов из системы остаточных классов в полиадический код, группа элементов ИЛИ, элемент И, две группы элементов И, два элемента ИЛИ, три элемента задержки и сумматор, причем выходы дешифраторов подключены к соответствующим группам входов преобразователя кодов из системы остаточных классов в полиадический код, выход и первая и вторая группы выходов которого соответственно подключены к информационному входу элемента И, инфо(рмационным входам элементов И первой группы и входам элементов ИЛИ, группы, выходы элементов ИЛИ которой подключены к информационным входам элементов И второй группы, выход элемента И через первый элемент задержки подключен к первому входу сумматора, выходы первого и второго элементов И первой группы подключены к первым входам элементов ИЛИ, выходы первого и второго элементов И второй группы подключены соответственно через второй и третьи элементы задержки ко второму и третьему входам сумматора, выходы третьего и четвертого элементов И второй группы подключены соответственно ко вторым входам элементов ИЛИ, вьгходы которых подключены соответственно к четвертому и пятому входам сумматора, выходы которого являются выходами преобразователя, управляющий вход элемента И и управляющие входы элементов И первой и второй групп соединены с первым, вторым и третьим входами преобразователя. На чертеже представлена блок-схема устройства. Устройство содержит входной регистр 1, дещифраторы 2, преобразователь 3 кодов из системы остаточных пластов в полиадический код, группу элементов ИЛИ 4, элемент И 5, группы б и 7 элементов И, элементы ИЛИ 8, элементы 9 задержки, сумматор 10, управляющие входы устройства 11 -13. Элементы задержки реализированы на элементах ИДИ. На чертеже показан преобразователь кодов из системы остаточных классов в двоичный позиционный код для трех модулей: Р 2; РЗ 3; РЗ 5. Преобразователь может быть построен и для п-модулей. Входной регистр разбит на три секции, каждая секция предназначена для хранения одного разряда системы остаточных классов в двоичном коде. Количество разрядов определяотсй величиной модуля. Количество входов и выходов у регистра одинаковое. Регистр может быть реализирован на триггерах. Выходы регистра поразрядно подсоединены к дещифраторам 2. Дешифраторы предназначены для получения кода системы остаточных классов, представленного в однопозиционном коде. Если во входном регистре инфор.мация представляется в однопозиционном коде, то необходимость в дешифраторах отпадает. Нреобразователь 3 служит для преобразования чисел А, представленных в сиеTejvie остаточных классов в полиадический код: -f а,Р.Рг. Преобразователь может быть реализован на логических элементах И, ИЛИ. Преобразование осуществляется за один такт. При поступлении первого тактового импульса по входу 11 значение коэффициента а поступает на вход элемента 9 задержки, реализованного на элементе ИЛИ. При поступлении второго тактового импульса по входу 12 формируется произведение и результат подается на вход соответствующих логических элементов ИЛИ 8. При поступлении третьего тактового импульса по входу 13 формируется произведение .. и результат подается на вход соответствующих логических элементов ИЛИ 8 и 9. Логические элементы ИЛИ .8 и задержки 9 служат для передачи значений произведений в двоичном коде на вход су.мматора 10. При конкретной системе модулей Pf 2, Р, 3, Pj 5 для представления полученного двоичного кода требуется 5 двоичных разрядов. Сумматор 10 предназначен для последовательного суммирования произведений а, agP,, ,-- При выбранной системе модулей время суммирования определяется в три такта. Для п - .модулей время суммирования определяется п-тактами. На выходе сумматора 10 на выходах сумматора образуется двоичный код. Устройство работает следующим обрз,зом. Число А ( ) представленное в системе остаточных классов своими вычетами по основаниям Ру, Рг., Р, которое требуется преобразовать в двоичный код, хранится на регистре 1. Так как дещифратор 2 и преобразователь 3 реализованы на комбинационных элементах, то сигналы на выходе блока 3 появляются чере времся, равное сумме средних задержек . nj-) |де к - количество логических элементов, соединенных в блоках последовательно. Поэтому первый тактовый импульс, поступающий по входу 11, подается через время 1 Второй тактовый импульс, поступающий по входу 12, подается через время Тг tcy одного логического элемента и третий тактовый импульс, поступающий по входу 13, подается через время Tj 2t tf , так как элементы ИЛИ и И включены последовательно. После каждого тактового импульса происходит суммирование на сумматоре 10. Таким образом, через три такта (при выбранных модулях) на выходах сумматора формируется двоичный код. Таким образом, время преобразования числа равно времени выполнения трех операций, а в общем случае равно вре.мени выполнения п-операций, где п - количество модулей системы. Формула изобретения Преобразователь кодов из системы остаточных классов в двоичный позиционный код, содержащий входной -регистр и три дещифратора, причем вы.оды разрядов первой, второй и третьей групп входного

Авторы

Даты

1981-03-15—Публикация

1979-04-13—Подача