Изобретение относится к-автоматике и вычислительной технике и может быть использовано в системах передачи и обработки информации.

Наиболее близким по технической сущности к заявляемому является устройство преобразования двоичного кода в код по модулю К, содержащее преобразователь параллельного кода в последовательности импульсов, группу элементов И, груг-пу узлов подсчета единиц по модулю К, генератор тактовых импульсов, счетчик по модулю К, элемент И, первый и второй элементы ИЛИ и блок управления.

Недостатками известного устройства являются низкое быстродействие и узкая область применения.

Целью изобретения является повышение быстродействия vi расширение области применения путем обеспечения возможности изменения величины модуля К.

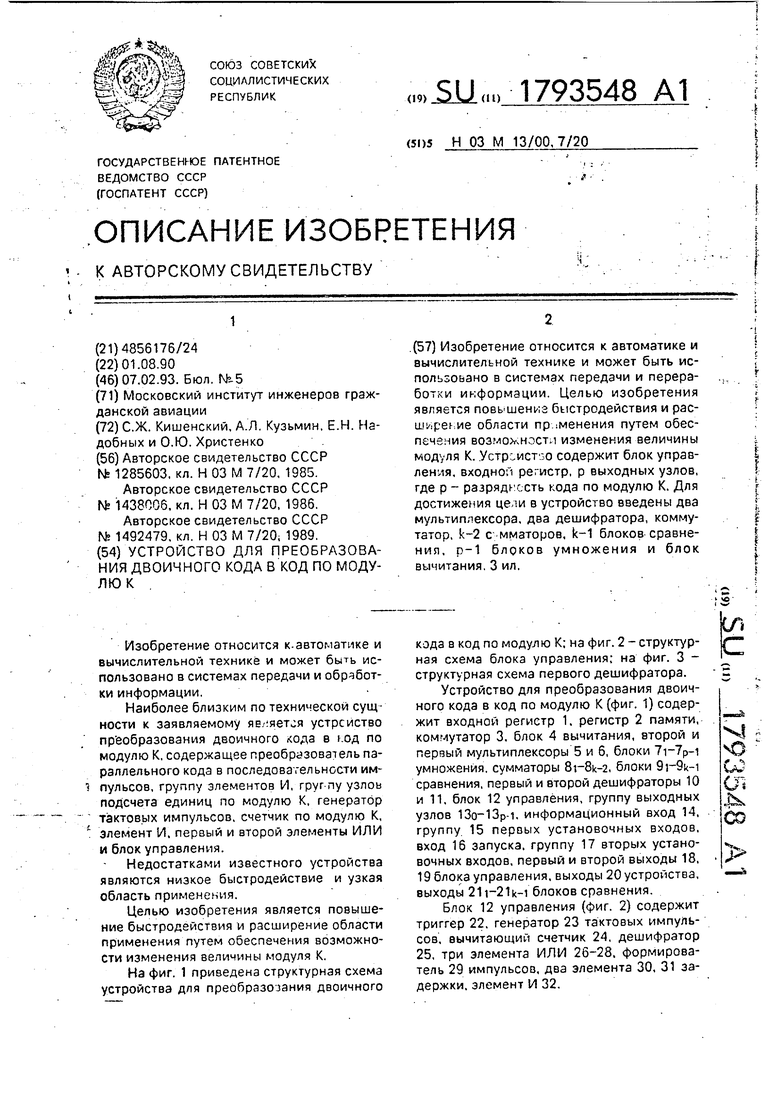

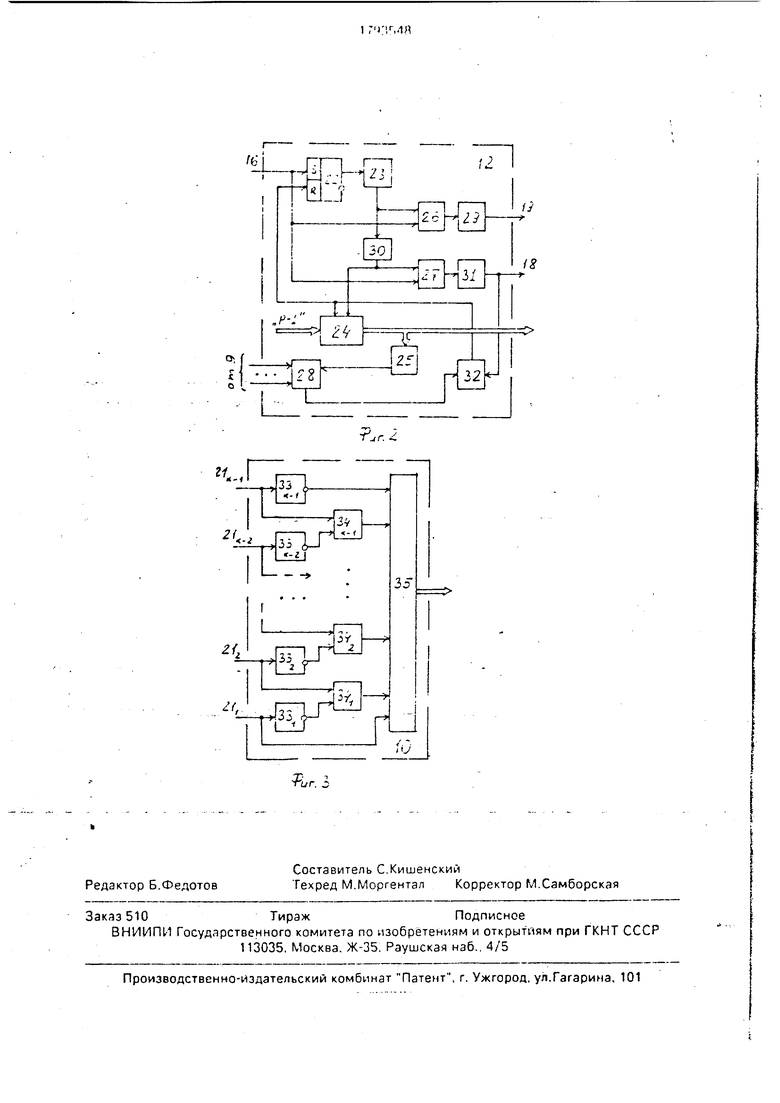

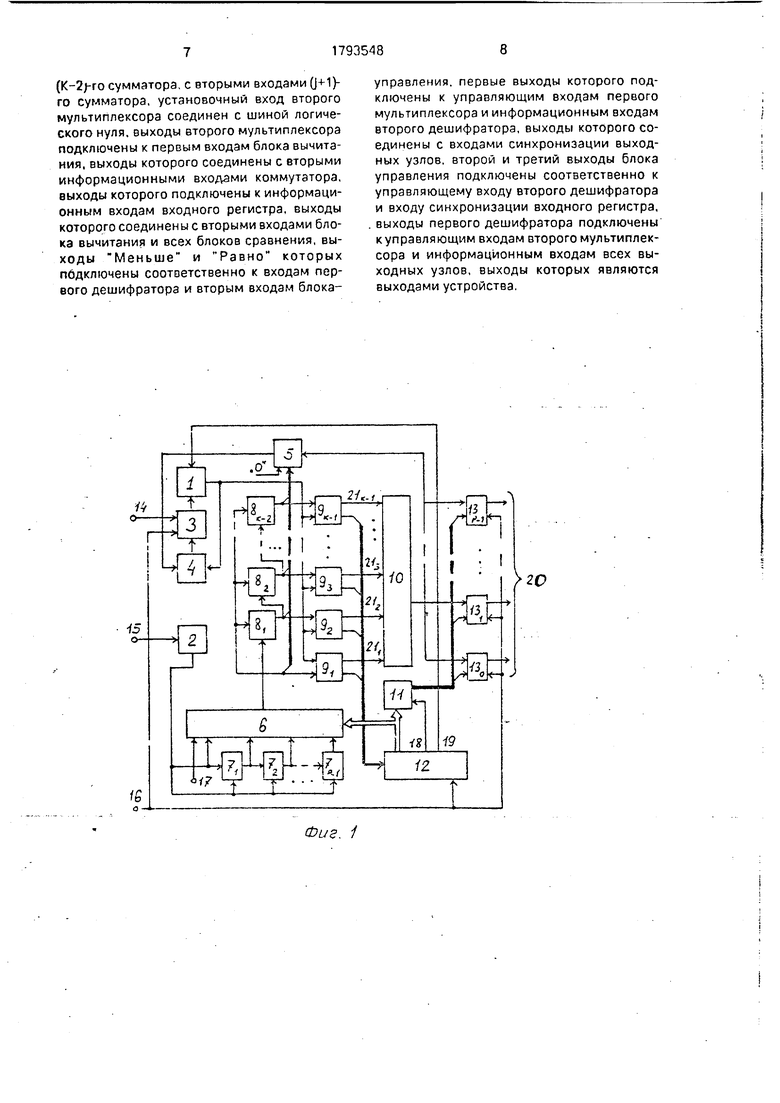

На фиг. 1 приведена структурная схема устройства для преобразования двоичного

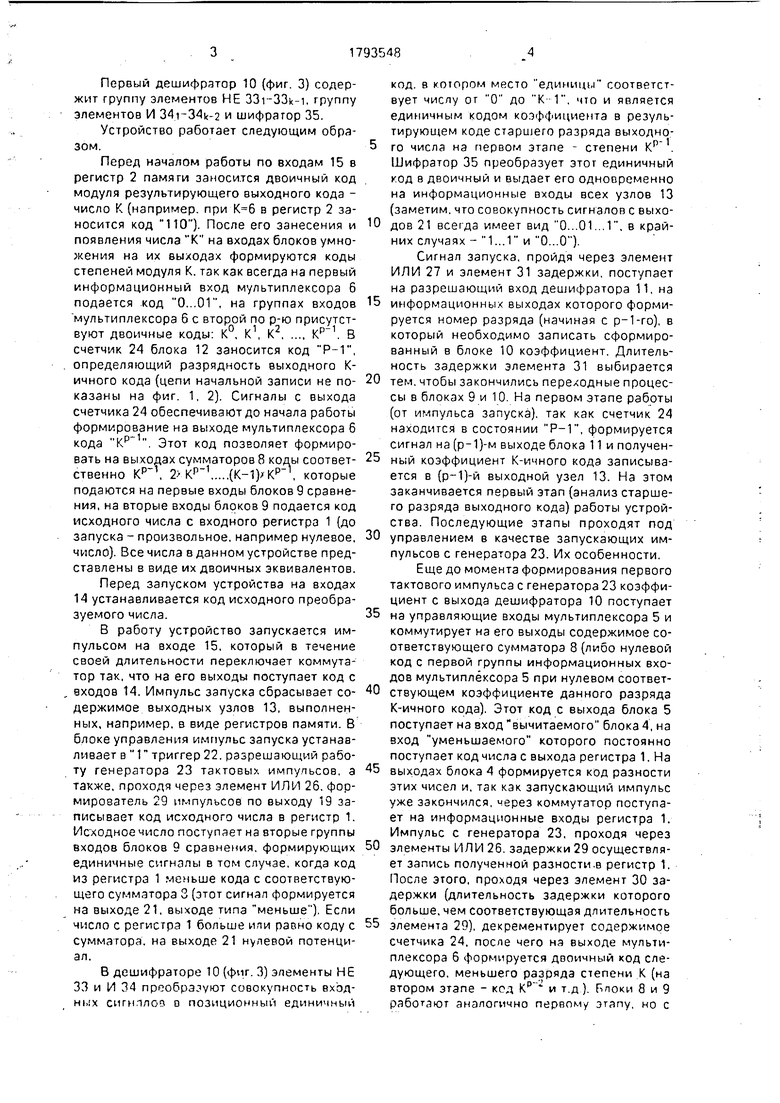

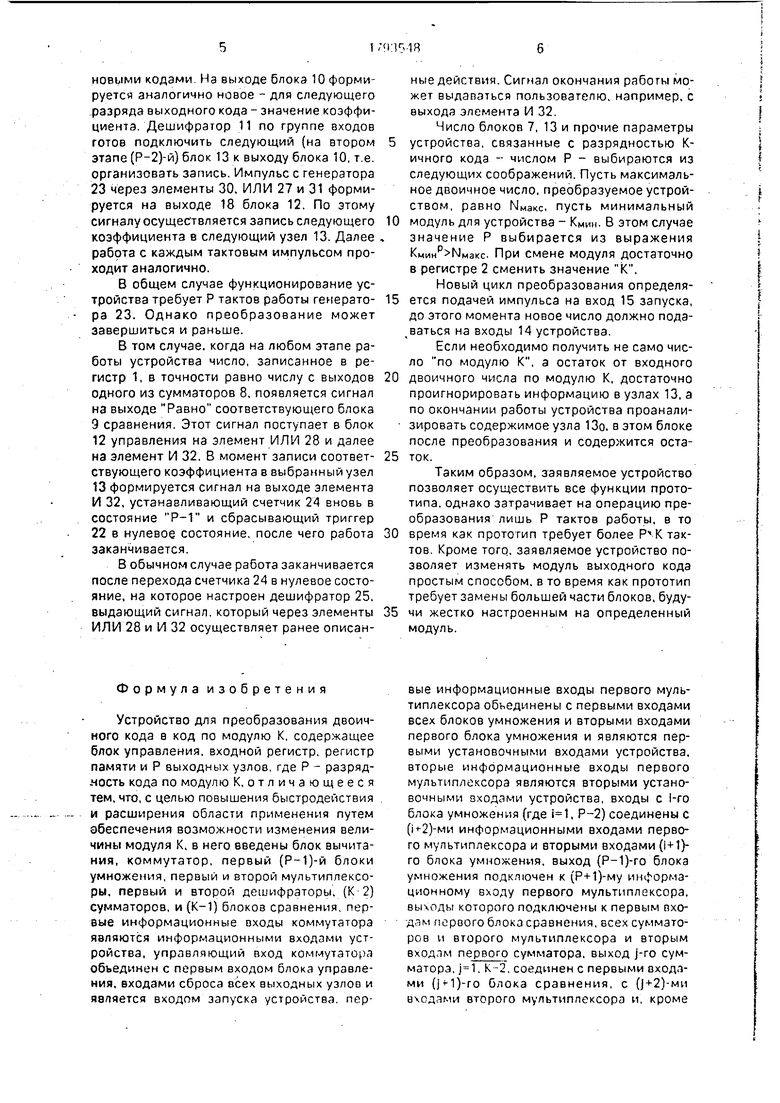

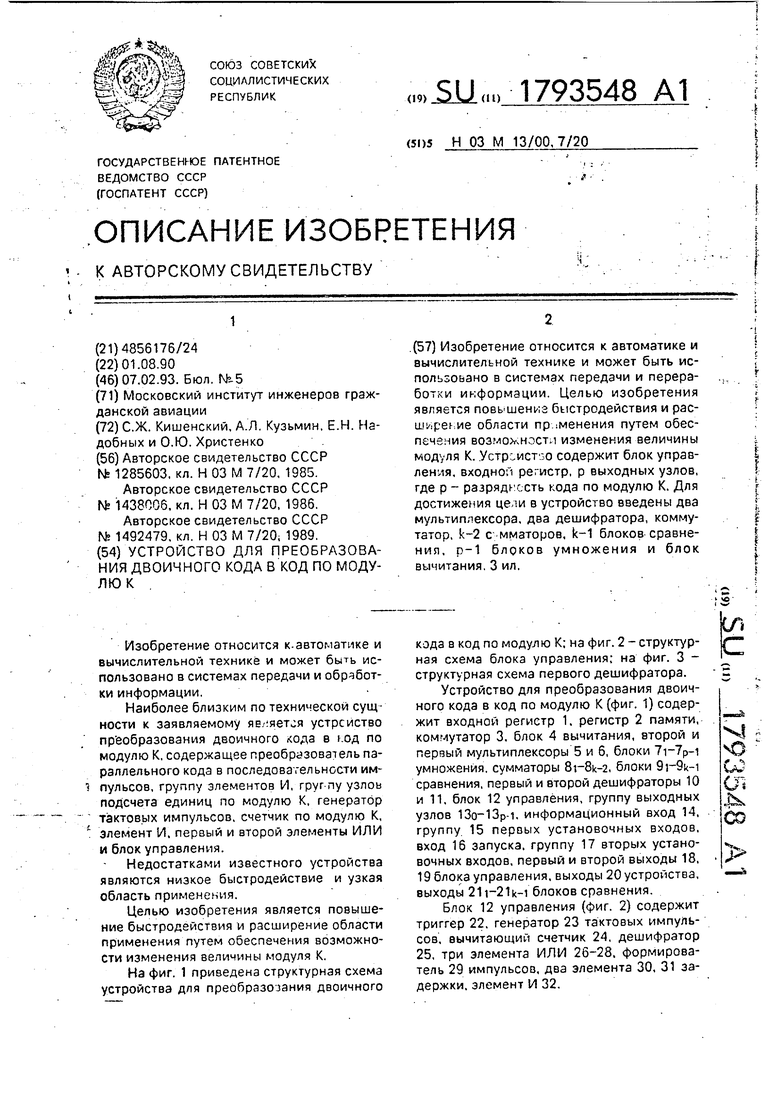

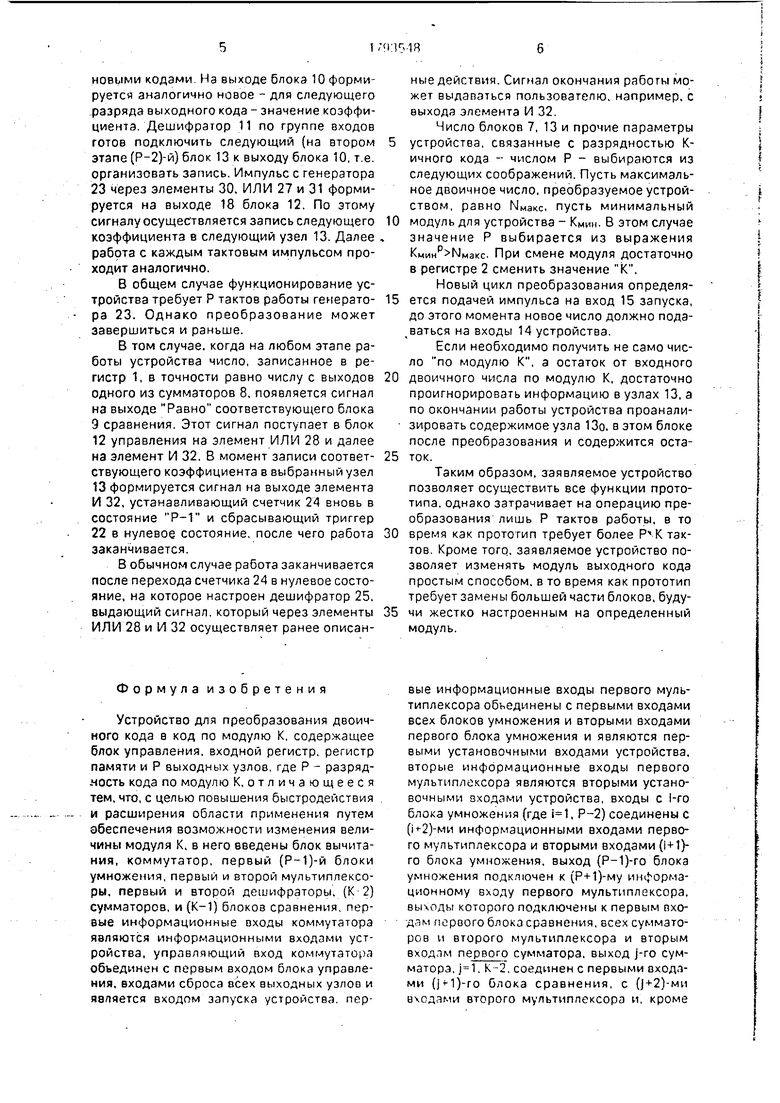

кода в код по модулю К; на фиг. 2 - структурная схема блока управления; на фиг. 3 - структурная схема первого дешифратора.

Устройство для преобразования двоичного кода в код по модулю К (фиг. 1) содержит входной регистр 1. регистр 2 памяти, коммутатор 3, блок 4 вычитания, второй и первый мультиплексоры 5 и 6, блоки 7i-7p-i умножения, сумматоры 8;-8ic-2, блоки сравнения, первый и второй дешифраторы 10 и 11, блок 12 управления, группу выходных узлов 13о 13р-1. информационный вход 14, группу 15 первых установочных входов, вход 16 запуска, группу 17 вторых установочных входов, первый и второй выходы 18, 19 блока управления, выходы 20 устройства, выходы 21 i-21k-i блоков сравнения.

Блок 12 управления (фиг. 2) содержит триггер 22, генератор 23 тактовых импульсов, вычитающий счетчик 24, дешифратор 25, три элемента ИЛИ 26-28. формирователь 29 импульсов, два элемента 30, 31 задержки, элемент И 32.

ел

с

VI ч

W

01

J

Первый дешифратор 10 (фиг. 3) содержит группу элементов НЕ 33i-33k-i, группу элементов И и шифратор 35.

Устройство работает следующим образом.

Перед началом работы по входам 15 в регистр 2 памяти заносится двоичный код модуля результирующего выходного кода - число К (например, при в регистр 2 заносится код 110). После его занесения и появления числа К на входах блоков умножения на их выходах формируются коды степеней модуля К. так как всегда на первый информационный вход мультиплексора 6 подается .код 0...01, на группах входов мультиплексора 6 с второй по р-ю присутствуют двоичные коды: К°, К1, К2, .... . В счетчик 24 блока 12 заносится код Р-Т, определяющий разрядность выходного К- ичного кода (цепи начальной записи не показаны на фиг. 1, 2). Сигналы с выхода счетчика 24 обеспечивают до начала работы формирование на выходе мультиплексора 6 кода . Этот код позволяет формировать на выходах сумматоров 8 коды соответственно . ,....(К-1)/Кр , которые подаются на первые входы блоков 9 сравнения, на вторые входы блоков 9 подается код исходного числа с входного регистра 1 {до запуска - произвольное, например нулевое, число). Все числа в данном устройстве представлены в виде их двоичных эквивалентов.

Перед запуском устройства на входах 14 устанавливается код исходного преобразуемого числа.

В работу устройство запускается импульсом на входе 15, который в течение своей длительности переключает коммутатор так, что на его выходы поступает код с входов 14. Импульс запуска сбрасывает содержимое выходных узлов 13, выполненных, например, в виде регистров памяти. В блоке управления импульс запуска устанавливает в 1 триггер 22. разрешающий работу генератора 23 тактовых импульсов, а также, проходя через элемент ИЛИ 26, формирователь 29 импульсов по выходу 19 записывает код исходного числа в регистр 1. Исходное число поступает на вторые группы входов блоков 9 сравнения, формирующих единичные сигналы в том случае, когда код из регистра 1 меньше кода с соответствующего сумматора 3 (этот сигнал формируется на выходе 21, выходе типа меньше). Если число с регистра 1 больше или равно коду с сумматора, на выходе 21 нулевой потенциал.

В дешифраторе 10 (фиг. 3) элементы НЕ 33 и И 34 преобразуют совокупность входных сигналов о позиционный единичный

код. в котором место единицы соответствует числу от О до К-1. что и является единичным кодом коэффициента в результирующем коде старшего разряда выходного числа на первом этапе - степени Кр . Шифратор 35 преобразует этот единичный код в двоичный и выдает его одновременно на информационные входы всех узлов 13 (заметим.что совокупность сигналов с выходов 21 всегда имеет вид 0...01...1, в крайних случаях - 1...1 и 0...0).

Сигнал запуска, пройдя через элемент ИЛИ 27 и элемент 31 задержки, поступает на разрешающий вход дешифратора 11, на

5 информационных выходах которого формируется номер разряда (начиная с р-1-го), в который необходимо записать сформированный в блоке 10 коэффициент. Длительность задержки элемента 31 выбирается

0 тем. чтобы закончились переходные процессы в блоках 9 и 10. На первом этапе работы (от импульса запуска), так как счетчик 24 находится в состоянии Р-1, формируется сигнал на (р-1)-м выходе блока 11 и получен5 ный коэффициент К-ичного кода записывается в (р-1)-й выходной узел 13. На этом заканчивается первый этап (анализ старшего разряда выходного кода) работы устройства. Последующие этапы проходят под

0 управлением в качестве запускающих импульсов с генератора 23. Их особенности.

Еще до момента формирования первого тактового импульса с генератора 23 коэффициент с выхода дешифратора 10 поступает

5 на управляющие входы мультиплексора 5 и коммутирует на его выходы содержимое соответствующего сумматора 8 (либо нулевой код с первой группы информационных входов мультиплексора 5 при нулевом соответ0 ствующем коэффициенте данного разряда К-ичного кода). Этот код с выхода блока 5 поступает на вход вычитаемого блока 4, на вход уменьшаемого которого постоянно поступает код числа с выхода регистра 1. На

5 выходах блока 4 формируется код разности этих чисел и, так как запускающий импульс уже закончился, через коммутатор поступает на информационные входы регистра 1. Импульс с генератора 23, проходя через

0 элементы ИЛИ 26. задержки 29 осуществляет запись полученной разности .в регистр 1. После этого, проходя через элемент 30 задержки (длительность задержки которого больше, чем соответствующая длительность

5 элемента 29), декрементирует содержимое счетчика 24. после чего на выходе мультиплексора 6 формируется двоичный код следующего, меньшего разряда степени К (на втором этапе - код Кр и т.д.). Блоки 8 и 9 работают аналогично первому этапу, но с

новыми кодами. На выходе блока 10 формируется аналогично новое - для следующего разряда выходного кода - значение коэффициента. Дешифратор 11 по группе входов готов подключить следующий (на втором этапе (Р-2)-й) блок 13 к выходу блока 10, т.е. организовать запись. Импульс с генератора 23 через элементы 30, ИЛИ 27 и 31 формируется на выходе 18 блока 12. По этому сигналу осуществляется запись следующего коэффициента в следующий узел 13. Далее работа с каждым тактовым импульсом проходит аналогично.

В общем случае функционирование устройства требует Р тактов работы генерато- рэ 23. Однако преобразование может завершиться и раньше.

В том случае, когда на любом этапе работы устройства число, записанное в регистр 1, в точности равно числу с выходов одного из сумматоров 8, появляется сигнал на выходе Равно соответствующего блока 9 сравнения. Этот сигнал поступает в блок

12 управления на элемент ИЛИ 28 и далее на элемент И 32. В момент записи соответ- ствующего коэффициента в выбранный узел

13 формируется сигнал на выходе элемента И 32, устанавливающий счетчик 24 вновь в состояние Р-1 и сбрасывающий триггер 22 в нулевое состояние, после чего работа заканчивается.

В обычном случае работа заканчивается после перехода счетчика 24 в нулевое состояние, на которое настроен дешифратор 25, выдающий сигнал, который через элементы ИЛИ 28 и И 32 осуществляет ранее описанные действия. Сигнал окончания работы может выдаваться пользователю, например, с выхода элемента И 32.

Число блоков 7, 13 и прочие параметры устройства, связанные с разрядностью К- ичного кода - числом Р - выбираются из следующих соображений. Пусть максимальное двоичное число, преобразуемое устройством, равно NMSKC- пусть минимальный модуль для устройства - КМин. В этом случае значение Р выбирается из выражения Кминр Ммакс. При смене модуля достаточно в регистре 2 сменить значение К.

Новый цикл преобразования определяется подачей импульса на вход 15 запуска, до этого момента новое число должно подэ- ваться на входы 14 устройства.

Если необходимо получить не само число по модулю К, а остаток от входного двоичного числа по модулю К, достаточно проигнорировать информацию в узлах 13, а по окончании работы устройства проанализировать содержимое узла 13о, в этом блоке после преобразования и содержится остаток.

Таким образом, заявляемое устройство позволяет осуществить все функции прототипа, однако затрачивает на операцию преобразования лишь Р тактов работы, в то время как прототип требует более Рх К тактов. Кроме того, заявляемое устройство позволяет изменять модуль выходного кода простым способом, в то время как прототип требует замены большей части блоков, будучи жестко настроенным на определенный модуль.

| название | год | авторы | номер документа |

|---|---|---|---|

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| Устройство для определения позиционных характеристик непозиционного кода | 1985 |

|

SU1283948A1 |

| Кодек квазициклического кода | 1986 |

|

SU1349010A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1413645A1 |

| Пороговый декодер @ -ичного кода | 1989 |

|

SU1642589A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| Преобразователь код-ШИМ | 1987 |

|

SU1462488A1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

Формула изобретения

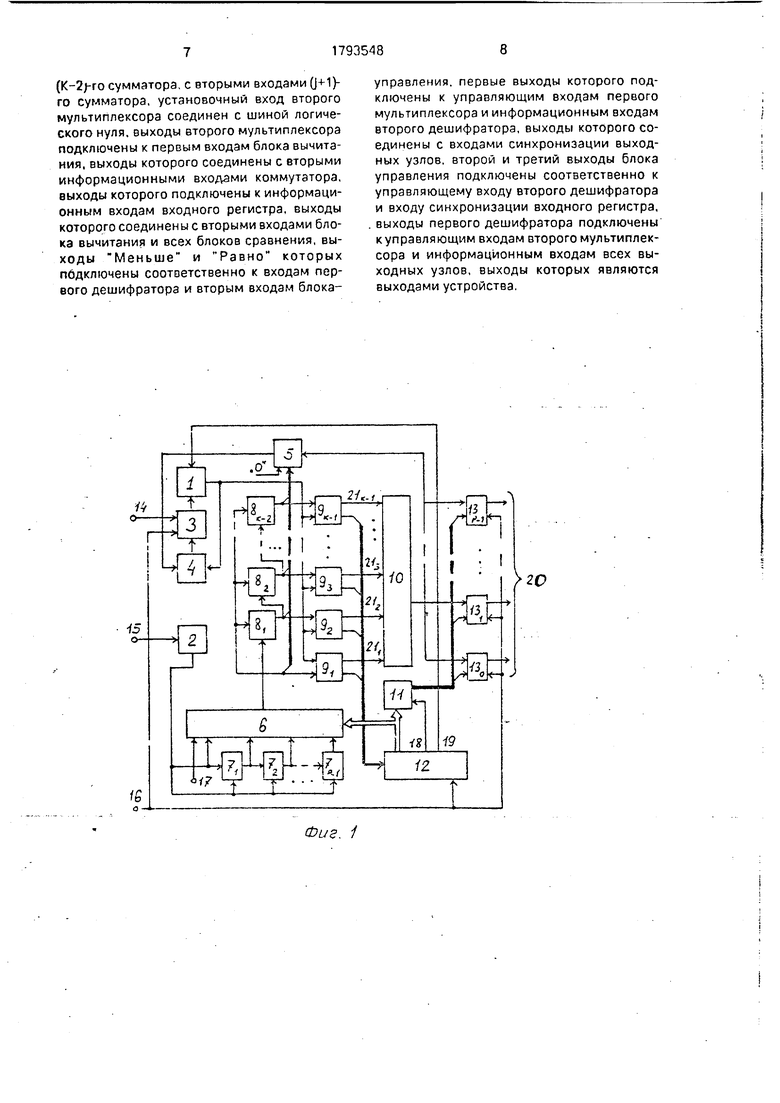

Устройство для преобразования двоичного кода в код по модулю К, содержащее блок управления, входной регистр, регистр памяти и Р выходных узлов, где Р - разрядность кода по модулю К, отличающееся тем, что, с целью повышения быстродействия и расширения области применения путем обеспечения возможности изменения величины модуля К. в него введены блок вычитания, коммутатор, первый (Р-1)-й блоки умножения, первый и второй мультиплексоры, первый и второй дешифраторы (К-2) сумматоров, и (К-1) блоков сравнения, первые информационные входы коммутатора являются информационными входами устройства, управляющий вход коммутаторе объединен с первым входом блока управления, входами сброса всех выходных узлов и является входом запуска устройства, первые информационные входы первого мультиплексора обьединены с первыми входами всех блоков умножения и вторыми входами первого блока умножения и являются первыми установочными входами устройства, вторые информационные входы первого мультиплексора являются вторыми установочными входами устройства, входы с 1-го блока умножения (где , P-2) соединены с (к2)-ми информационными входами первого мультиплексора и вторыми входами (1+1)- го блока умножения, выход (Р-1)-го блока умножения подключен к (Р+1)-му информационному входу первого мультиплексора, выходы которого подключены к первым входам первого блока сравнения, всех сумматоров и второго мультиплексора и вторым входам первого сумматора, выход j-ro сумматора. 1. К -2, соединен с первыми входами (jH)-ro блока сравнения, с (+2)-ми входами второго мультиплексора и, кроме

(K-2j-ro сумматора, с вторыми входами (j+1)- го сумматора, установочный вход второго мультиплексора соединен с шиной логического нуля, выходы второго мультиплексора подключены к первым входам блока вычитания, выходы которого соединены с вторыми информационными входами коммутатора, выходы которого подключены к информационным входам входного регистра, выходы которого соединены с вторыми входами блока вычитания и всех блоков сравнения, выходы Меньше и Равно которых подключены соответственно к входам первого дешифратора и вторым входам блокаФиг. 1

управления, первые выходы которого подключены к управляющим входам первого мультиплексора и информационным входам второго дешифратора, выходы которого соединены с входами синхронизации выходных узлов, второй и третий выходы блока управления подключены соответственно к управляющему входу второго дешифратора и входу синхронизации входного регистра, выходы первого дешифратора подключены к управляющим входам второго мультиплексора и информационным входам всех выходных узлов, выходы которых являются выходами устройства.

fe L S- -rj

--И 7 J i Л : i

LU.i

,P l

JT

Ы

t,

r

О ч

f2

/y

rtL

/г

i

Г

32

| Преобразователь кодов | 1985 |

|

SU1285603A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для подсчета числа единиц двоичного кода по модулю К | 1986 |

|

SU1438006A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования двоичного кода в код по модулю К | 1987 |

|

SU1492479A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1993-02-07—Публикация

1990-08-01—Подача