f

Изобретение относится к электротехнике и может быть использовано - при разработке источников электропитания интегральньпс схем.

Цель изобретения - повышение функциональных возможностей путем повышения коэффициента умножения, нагрузочной способности и упрощение управления.

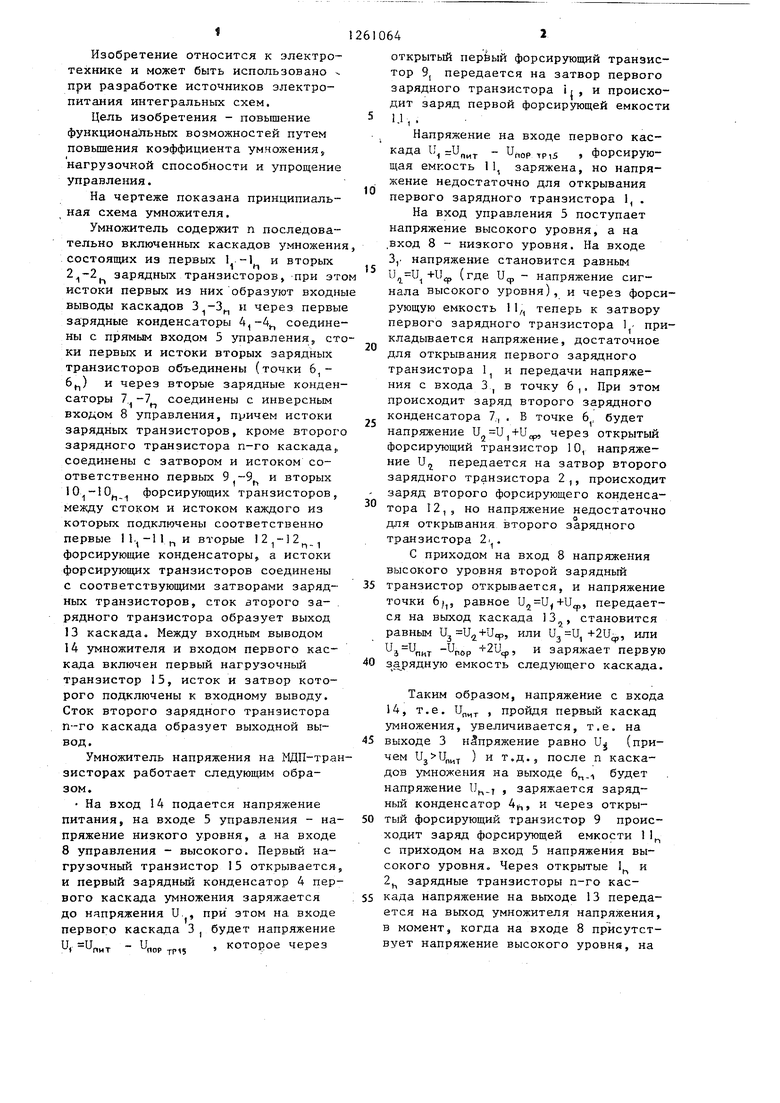

На чертеже показана принципиальная схема умножителя.

Умножитель содержит п последовательно включенных каскадов умножени состоящих из первых 1, 1 и вторых зарядных транзисторов, при эт истоки первых из них образуют входн выводы каскадов и через первы зарядные конденсаторы 4,-4 соединены с прямым входом 5 управления,, стки первых и истоки вторых зарядных транзисторов объединены (точки 6,и через вторые зарядные конден6.)

саторы 7, -7 соединены с инверсным входом 8 управления, причем истоки зарядных транзисторов, кроме второг зарядного транзистора п-го каскада,, соединены с затвором и истоком соответственно первых 9-9 и вторых 10-10. . форсирующих транзисторов,

1 г1 I

между стоком и истоком каждого из которых подключены соответственно первые П.-11 и вторые форсирующие конденсаторы, а истоки форсирующих транзисторов соединены с соответствующими затворами зарядных транзисторов, сток второго зарядного транзистора образует выход

13каскада. Между входным выводом

14умножителя и входом первого каскада включен первый нагрузочньй транзистор 15, исток и затвор которого подключены к входному выводу. Сток второго зарядного транзистора П--ГО каскада образует выходной вывод.

Умножитель напряжения на ВДП-тра зисторах работает следующим образом.

На вход 14 подается напряжение питания, на входе 5 управления - напряжение низкого уровня, а на входе 8 управления - высокого. Первый нагрузочный транзистор 15 открывается и первый зарядный конденсатор 4 первого каскада умножения заряжается до напряжения U., при зтом на входе

первого каскада 3

и, Up

- и,

ПОР -i-plS

будет напряжение которое через

261064

открытый перйый форсирующийтранзистор 9| передается на затворпервого зарядного транзистора ij, ипроисхо10

15

20

дит заряд первой форсирующей емкости 1.1,Напряжение на входе первого каскада и и„ - ,5 , форсирующая емкость 11 заряжена, но напряжение недостаточно для открывания первого зарядного транзистора 1, .

На вход управления 5 поступает напряжение высокого уровня, а на .вход 8 - низкого уровня. На входе 3,. напряжение становится равньм (где U;p - напряжение сигнала высокого уровня), и через форсирующую емкость 1 1,, теперь к затвору первого зарядного транзистора Ь прикладывается напряжение, достаточное для открывания первого зарядного транзистора 1, и передачи напряжения с входа 3j в точку 6,. При зтом происходит заряд второго зарядного

конденсатора 7.,

В точке 6,

будет

напряжение U,.,U,+U через открытый форсирующий транзистор 10, напряжение и передается на затвор второго зарядного транзистора 2,, происходит заряд второго форсирующего конденсатора 12,, но напряжение недостаточно для открьюания второго зарядного транзистора 2..

С приходом на вход 8 напряжения высокого уровня второй зарядный транзистор открывается, и напряжение точки 6;,5 равное , передается на выход каскада 13,, становится равным , или , или - пор +2U, и заряжает первую здрядную емкость следующего каскада.

Таким образом, напряжение с входа 14, т.е. и„ , пройдя первый каскад умножения, увеличивается, т.е. на выходе 3 нЗпряжение равно U (причем и,и„.

)

и т.д.

после п каскадов умножения на выходе б, будет напряжение U., , заряжается зарядный конденсатор 4, и через открытый форсирующий транзистор 9 происходит заряд форсирующей емкости 1 с приходом на вход 5 напряжения высокого уровня. Через открытые и 2 зарядные транзисторы п-го каскада напряжение на выходе 13 передается на выход умножителя напряжения, в момент, когда на входе 8 присутствует напряжение высокого уровня, на

31/61064

ыходе умножителя напряжения происодит подкачка-заряда, т.е. . Применение изобретения позволяет омпенсировать влияние напряжения мещения подложки.

ормула изобретения

чен а с выв из рог кас щег ком с я рав воз фиц и н вве вкл фор тво ра, вто кас сво обр ва.

Умножитель напряжения на МДП-тран зисторах, содержащий первый нагрузоч ный транзистор, исток которого подключен к выходному выводу, а сток - к входу умножителя напряжения, состо ящему из п последовательно включен- .ных каскадов умножения напряжения, каждый из которых состоит из первого и второго зарядных транзисторов, при этом исток первого из них образует входной вывод каскада и через первый зарядный конденсатор соединен с прямым входом управления, сток первого и исток второго объединены и через второй зарядный конденсатор подклюСоставитель И. Никитин Редактор Л. Веселовская Техред Л.Олейник Корректор А. Тяско

Заказ 52А1/55Тираж 631

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

to

t5

20

чены к инверсному входу.управления, а сток - второго образует выходной вывод каскада, причем исток каждого из зарядных транзисторов, кроме второго зарядного транзистора п-го каскада, соединен с истоком форсирующего транзистора, а затвор - со стоком последнего, отлича ющий- с я тем, что, с целью упрощения управления и расшипрния функциональных возможностей путем повышения коэффициента умножения каждого каскада и нагрузочной способности, в него введены форсирукицие конденсаторы, включенные между истоком и стоком форсирующих транзисторов, причем затворы первого нагрузочного транзистора, всех форсирующих транзисторов и второго зарядного транзистора п-го каскада подключены соответственно к своим истокам, а сток последнего образует выходной вывод устройс г- ва.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер на МДП-транзисторах | 1985 |

|

SU1330654A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| КЛЮЧЕВОЙ КАСКОДНЫЙ УМНОЖИТЕЛЬ НАПРЯЖЕНИЯ ПОСТОЯННОГО ТОКА ВЫСОКОВОЛЬТНЫЙ ККУНПТВВ | 2007 |

|

RU2340082C1 |

| Генератор импульсов | 1973 |

|

SU561293A1 |

| Триггер на МДП-транзисторах | 1985 |

|

SU1330655A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Формирователь импульсов на МОП-транзисторах | 1988 |

|

SU1653142A1 |

| Буферное устройство на мдп-транзисторах | 1973 |

|

SU458099A1 |

| БЕСПРОВОДНАЯ ЗАРЯДНАЯ СИСТЕМА (ВАРИАНТЫ) | 2006 |

|

RU2306654C1 |

| Усилитель-формирователь импульсов на мдп транзисторах | 1974 |

|

SU525247A1 |

Умножитель напряжения на МДП- транзисторах может быть использован при разработке источников электропитания интегральных схем. Цель изобретения - повышение функциональных возможностей путем повьшения коэффициента умножения, нагрузочной способности и упрогдение управления. Умножитель содержит п последовательно включенных каскадов умножения, состоящих из первых зарядных транзисторов (ЗТ) 1-1. и вторых ЗТ 2,-2 , Л л 1 Истоки 3X1 образуют входные выводы каскадов 3 -3 и через первые зарядные конденсаторы (ЗК) соединены с прямым входом блока управления (БУ) 5, вторые ЗК 7.,-7 - с инверсным входом управления 8. Введение форсирующих транзисторов 9, 10 и их включение позволяет заряжать форсирующие емкости 11 , 12. в момент напряжения низкого уровня на выходных шинах прямого и инверсного сигналов БУ 5 и препятствуют разряду этих емкостей в момент напряжения высокого уровня на выходных шинах прямого и инверсного сигналов БУ 5. Повышение напряжения на затворах ЗТ1 и ЗТ2 в момент подачи фазного напряжения на выходную шину прямого сигнала БУ 5 либо на выходную шину инверсного сигнала БУ 5 обеспечивает умножение напряжения. Устройство позволяет использовать проектирование схемы с одним источником питания. 1 ил. с 9 КчЭ Од

| IEEE Journal of Solid St | |||

| Cir | |||

| Vol | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| p | |||

| 532 | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Cir | |||

| Vol | |||

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| 539 | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1986-09-30—Публикация

1984-06-28—Подача