в

-

iO

ел со

Ј ,го

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсного сигнала по переднему и заднему фронтам адресных сигналов на МОП -транзисторах | 1985 |

|

SU1381694A1 |

| Устройство обнаружения смены адресного сигнала в интегральном исполнении на МОП-транзисторах | 1984 |

|

SU1249695A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

| Формирователь сигналов записи | 1986 |

|

SU1345257A1 |

| Реверсивный счетчик на мдп-транзисторах | 1977 |

|

SU711690A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

| Формирователь тактовых импульсов | 1975 |

|

SU566355A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

Изобретение относится к импульсной технике, может быть использовано в цифровой технике на МОП-транзисторах и позволяет уменьшить ток потребления при сохранении быстродействия Формирователь импульсов на МОП-транзисторах содержит входной инвертор 1, динамический драйвер 2 входного сигнала, первый повторитель 3 и повторитель 4 выходного сигнала Шина 5 является влодом формирователя импульсов шина 6 шина выхода входного инвертора шина 7 - шина выхода динами ческого драйвера шина 8 - выход первого повторителя и шина 9 выход повторителя выходного сигнала и выход формирователя импульсов При возрастании потенциала в точке 5 на входе формирователя импульсов возрастают потенциалы точек 7 9, что приводит из-за наличия положительной обратной связи к ускорению переходного процесса по входу динамического драйвера 2 таким образом, что потенциал точки 7 пре вышает напряжение источника питания В установившемся режиме единственным потребляющим узлом будет входной инвертор 1 При нулевом входном уровне формирователь импульсов не имеет статического потребления 1зп ф-лы 4 ил (Л С

Щиг.1

Изобретение относится к импульсной технике и может быть использовано в цифровой технике на МОП-транзисторах.

Цель изобретения - уменьшение тока потребления при сохранении быстродейсг- вия.

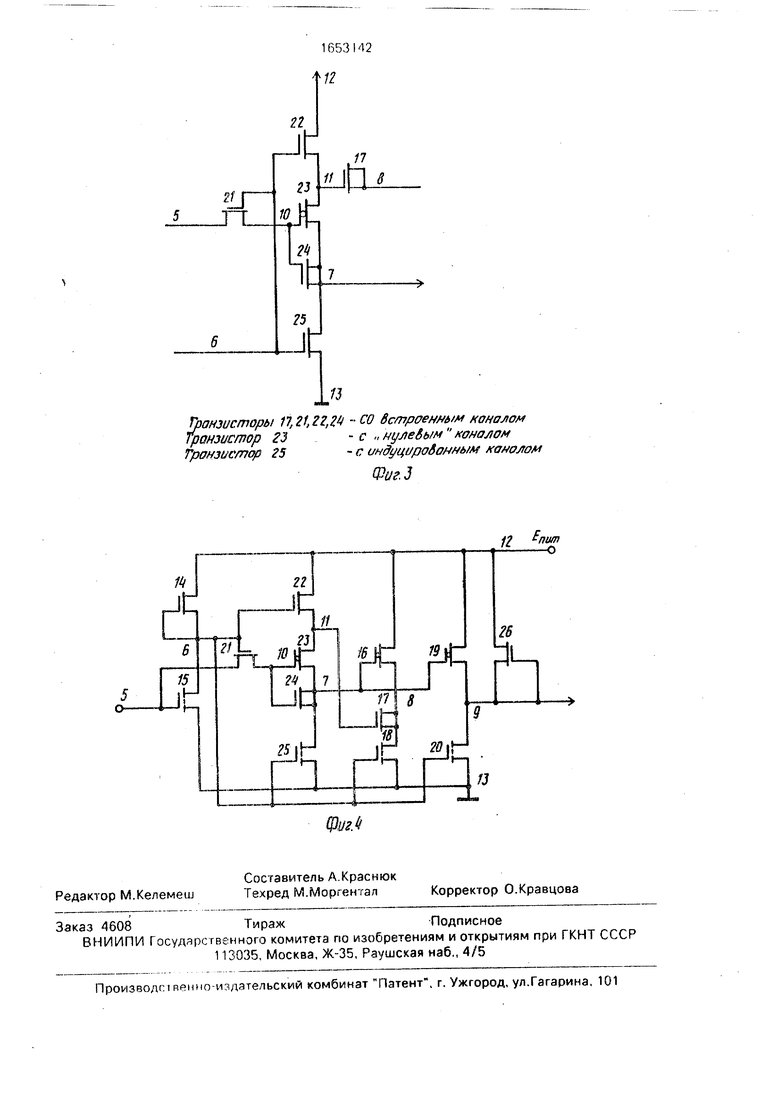

Нафиг 1 предстзвченз фугкционэльнля схема формирователя импульсов, на Фиг.2 - временные диаграммы, поясняющие его работу; на фиг.З - принципиальная электриче- екая схема динамического драйвера входного сигнала.; на фиг 4 принципиальная электрическая схема формирователя импульсов на МОП-транзисторах,

Формирователь импульсов содержит входной инвертор 1. динамический драйвер 2 входного сигнала, первый повторитель 3 и посюритель 4 выходного сигнала, Шина 5 является входом формирователя импульсов - в нее включены вход входного инвертора и прямой вход динамического драйвера. Шина 6 является выходом входного инвертора - к ней подключены инверсный вход динамического драйвера, инверсный вход первого повторителя и инверсный вход по- вторителя выходного сигнала. Шина 7 является выходом динамического драйвера - в нее включены прямой вход первого повторителя и прямой вход повторителя выходно го сигнала. Шчна 8 является выходов первого повторителя - в .tee включен фсо- мирующий вход ложи ельной обр j мои связи динамически о драйвера. Шиьп 9 является ВЫХОДОМ Повторителя БЬ.лОДМСГ С 1Гнала и выходом формирователя имиульсоь

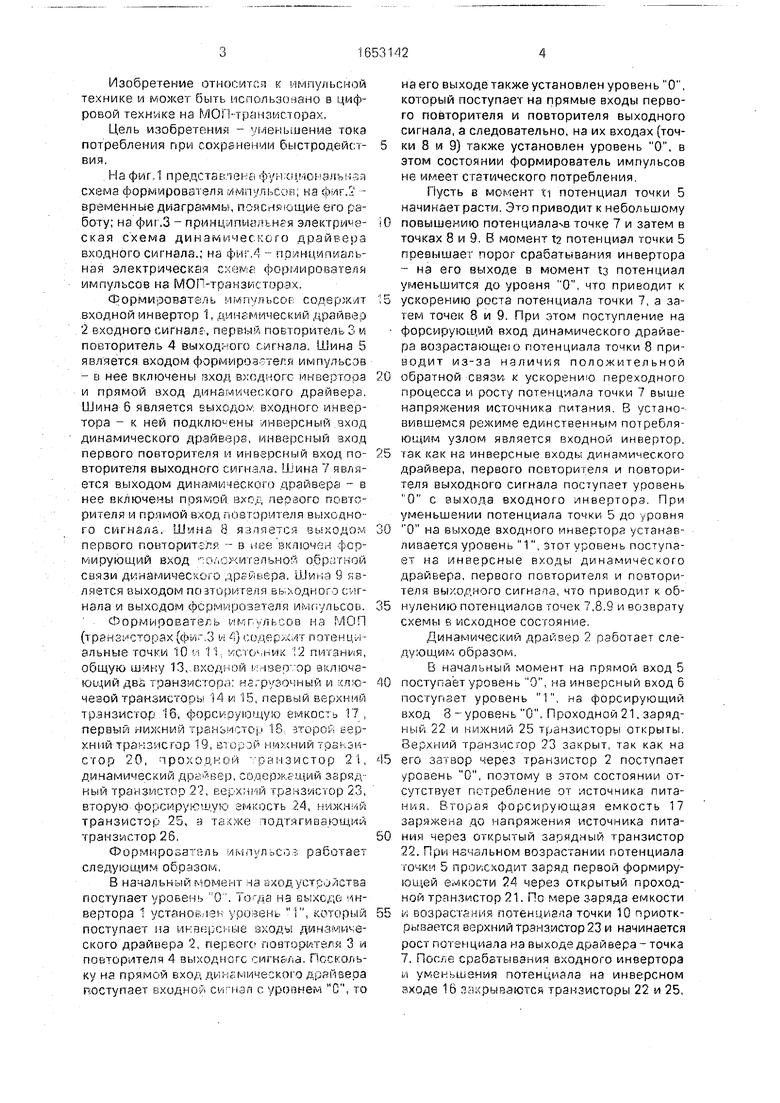

Формирователь игт.v/ii- оо нн МОП (трапа.1 :торэу ((и. 3 и .) M;и т ттенц.1- альные точки 10 1 I исю-.ми 12 пигзния, общую шину 13, входной мнвегпор включающий два транзистора нагрузочный и клю- чееой транзисторы 14 и 15, первый верхний трянзиссор 6, форсирующую емкость 7 , первый нижним транзистор 18, зторо унпй транзистор 19, второй нихний тракзи- с гор 20, .аной резистор 21, динамический драйвер, спдепх-чщий заряд ный транзистор 22, верхний транзистор 23, вторую форсирующую змкость 24, нижней транзистор 25, а также подтягивающий транзистор 26.

Формирователь импульсов работает следующим

В начальный N-омент на вход устройства поступает уровень 0. Тогда на вьхсде инвертора 1 установлен уровень , который поступает на индексные входы динамического драйвера 2. первого повторителя 3 и повторителя 4 выходного сигнала. Поскольку на прямой вход динамического драйвера поступает ехидной сигнол с уровнем С, то

на его выходе также установлен уровень О, который поступает на прямые входы первого повторителя и повторителя выходного сигнала, а следовательно, на их входах (точки 8 и 9) также установлен уровень О, в этом состоянии формирователь импульсов не имеет статического потребления

Пусть в момент ti потенциал точки 5 начинает расти. Это приводит к небольшому повышению потенциалам точке 7 и затем в точках 8 и 9. В момент т.2 потенциал точки 5 превышает порог срабатывания инвертора - на его выходе в момент t3 потенциал уменьшится до уровня О, что приводит к ускорению роста потенциала точки 7, а затем точек 8 и 9. При этом поступление на форсирующий вход динамического драйвера возрастающею потенциала точки 8 приводит из-за наличия положительной обратной связи к ускорению переходного процесса и росту потенциала точки 7 выше напряжения источника питания В установившемся режиме единственным потребляющим узлом является входной инвертор, гак как на инверсные входк; динамического драйвера, первого повтори)еля и повторителя выходного сигнала поступает уровень О с выхода входного инвертора При уменьшении потенциала точки 5 до vposna О на выходе входного инвертора устанавливается уровень 1, этот уровень поступает на инверсные входы динамического драйвера, первого повторителя и повторителя выходного сигнапа что приводит к об- н/лению потенциалов точек 7,8.9 и возврату схемы R исходное состояние

Динамический драйвер 2 работаетсле- д.ощим образом

В начальный момент на прямой вход 5 посту,,ает уровень О, на инверсный вход 6 поступает уровень 1, на форсирующий вход 3 - уровень О. Проходной 21,заряд- | кй 22 и нижний 25 транзисторы открыты. 3ер.ний транзистор 23 закрыт, так как на его з. пвор через транзистор 2 поступает уровень О, поэтому в этом состоянии отсутствует потребление от источника питания, Вторая Форсирующая емкость 17 заряжена до напряжения источника питания через открытый зарядный транзистор 22. При начальном возрастании потенциала ючки 5 происходит заряд первой формирующей емкости 24 через открытый проходной транзистор 21. По мере заряда емкости и оозраскчния потенциапа точки 10 приотк- оывается верхний транзистор 23 и начинается рост потенциала на выходе драйвера - точка 7. После срабатывания входного инвертора и уменьшения потенциала на инверсном зходе 16 гк- хрыеаются транзисторы 22 и 25,

что приводит к ускорению роста потенциала точки 7. Вследствие наличия сильной емко стной связи через емкость 17 потенциал том ки 11 растет синхронно с ростом потенциала на форсир/ющем входе 8 выше напряжения источника питания. Для эффек- ь |гзнои г гого чотенциала на выход драйвера чррез i, OHJI 23 введена пер ая (Ьорсирую дая емкость 24 и проходной транзистор 21, и .ЛОДСТВИР че.о потенциал на затзоре 23 в период рьбатнеания драйвера превышает потенциал на эг1 истоке и транзистор 22 остается все время откры 1ым В установившемся состсчиии, как и г предыдущем протекание тока orcyiCTpyei, Tr.i-- как закрыт транзистор 25. При переклю иг;;нии входного сигнала с уровня 1 до уровня 0 сработает входной иньер jp от крываюгся трангисгоры 21,22 и Ь оон/ля ются потенциалы точек 10 и 1 схемj возвращается в мгхот,ное состояние

Форм/па изобретения 1 Формирователь импульсов на МОП транзисторах, содержащий входной инвертор, перчый повторитель, повторитель выходного сигнала, причем первый повто ригель и повторитель выходного сигнал - niv-еют прямой и инверсный входи, инваре нь1 вход первого повтори гепя соединен с инверсным входом повторителя выходною сигнала и выходом -/одного инвертора вы- хо;; повюри еля является выходом формм рователя импулюов, отличающийся тем что, с целью уменьшения питребпяемои мощности при сохранении Ьыстродеист вия, в кто введен динамический дрзгвер входного г.и1наля, солержзщий прямом инверсный и форсирующий причем прямой в,од соединен с входами формирователя и

t, ii

(йодного инвертора инверсный вход соодч нен г инверсными входами первою повтори теля и повторителя выходного сигнала и выходом входного инвертора фоосирую щий вход - с выходом первого повторителя выход динамического и вера - с прямыми вхолчми первою г,,, о. opt ч пя и поюор гр ля выходною си,1 нала

2 Формировании, по ri 1 т л и « 0 щ и и с ч тем, ч .о ) чг iui драйгег входного сигнала годерясит верхний нижний, проходной и ч,1ряднчи тран истопь , первую ti вторую фороир ющие емкости причем сток нижнего тргнэисторд -( едичен

S с выходом г.инлмического драйвера этгор ч ЖНРГО тоанзисгора - с инверснь м динамического дрлйвеиг1 исток нижнею транзистора - с общей шиной феомирова- еля импульсов, сток зарядного транзисто

0 оас шиной источьика питания

формирователя импульсов исток - с затвором второй форсирующей емкости, выполненной на МОП-транзисторе затвор зарядною транзистора соединен с инверс5 ным входом динамического драйвера, сток- исток второй формирующей емкости соединены с Форсирующим входом динамического доайвера, исток верхнего трзнзи- гюра со стоком нижнего транзистора, со

0 с током IVTOCOM форсирующей емкости на МОП-транзисторе п выходом динамического драйвера, пек воихн гс транзистора соединен с истоком зарчдн гг гр,чмзистора и за г юром второй форсирующем емкости,

5 затвор верхнего транэистооа - с затвором первс.м форсирующей емкости и истоком проходного транзистора сток проходного транзит гора - с прямым вводом динамического драйвера, а затвор - с инверсным вхо0 дом динамического драйвера.

Г- t

йг2

., л 1

Ч 5 -б

/3

Транзисторы П,21,22,М СО встроенным каналом Транзистор 23- с , нулебь/м каналом

Транзистор 25-синдуцированным каналом

Фиг.З

| Номографический прибор | 1935 |

|

SU44066A1 |

Авторы

Даты

1991-05-30—Публикация

1988-04-06—Подача