Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных устройствах динамической логики.

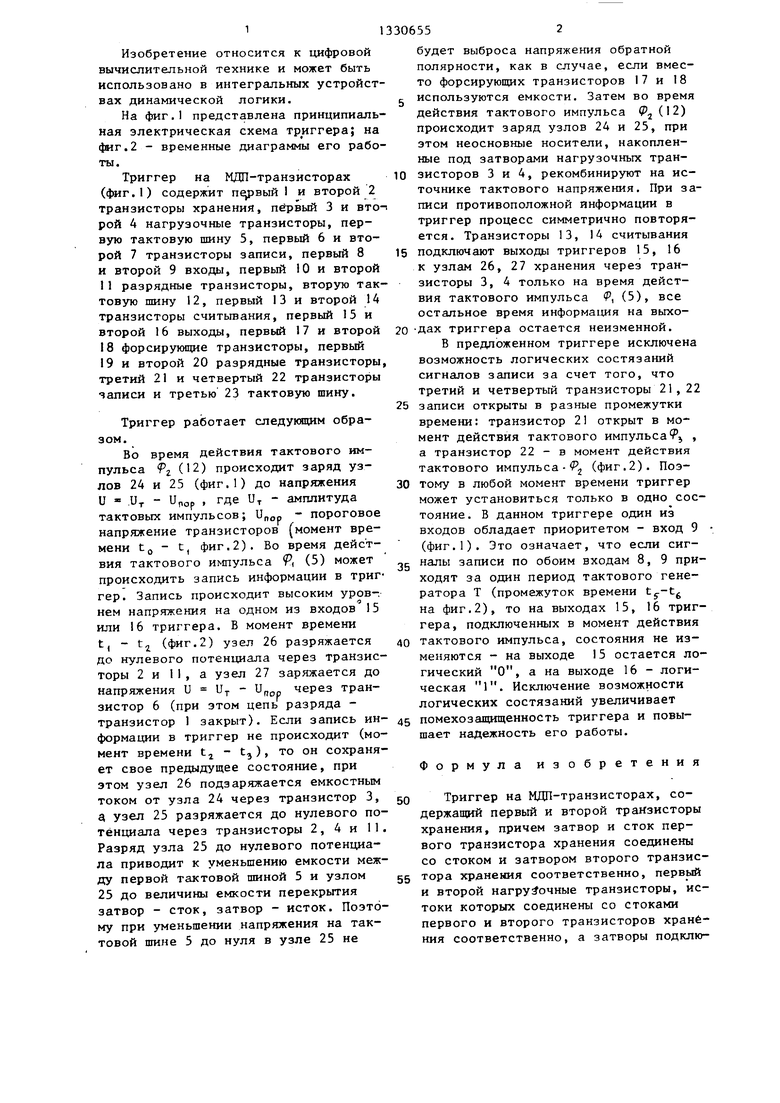

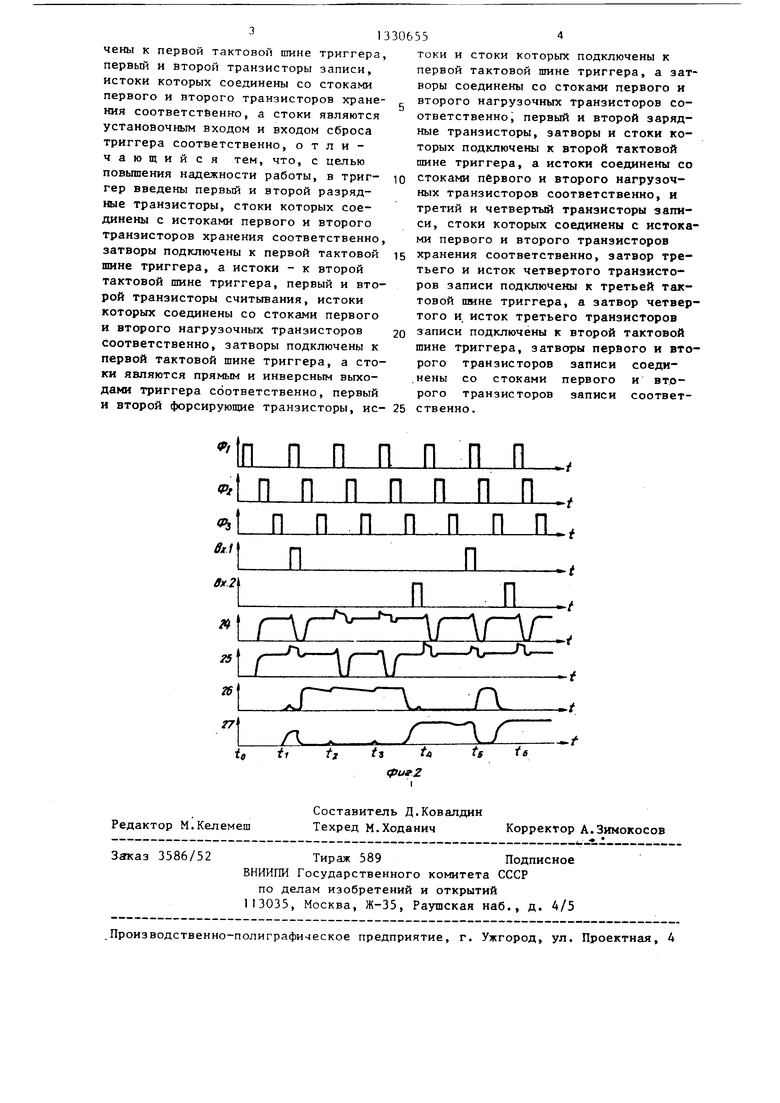

На фиг.1 представлена принципиальная электрическая схема триггера; на фиг.2 - временные диаграммы его работы.

Триггер на МДП-транзисторах (фиг.1) содержит 1 и второй 2 транзисторы хранения, первый 3 и BTO рой 4 нагрузочные транзисторы, первую тактовую шину 5, первый 6 и второй 7 транзисторы записи, первый 8 и второй 9 входы, первый 10 и второй I1 разрядные транзисторы, вторую тактовую шину 12, первый 13 и второй 14 транзисторы считьгаания, первый 15 и второй 16 выходы, первый 17 и второй

18форсирующие транзисторы, первый

19и второй 20 разрядные транзисторы третий 21 и четвертый 22 транзисторы записи и третью 23 тактовую шину.

Триггер работает следующим образом.

Во время действия тактового импульса 2. ( 2) Происходит заряд узлов 24 и 25 (фиг.1) до напряжения и .UT - и pop , где и т - амплитуда тактовых импульсов; „оо пороговое напряжение транзисторов (момент времени to - t, фиг.2). Во время действия тактового импульса Р, (5) может

происходить запись информации в триггер. Запись происходит высоким уров-. нем напряжения на одном из входов 15 или 16 триггера. В момент времени t, - t,, (фиг.2) узел 26 разряжается до нулевого потенциала через транзисторы 2 и 11, а узел 27 заряжается до напряжения U U - через транзистор 6 (при этом цепь разряда - транзистор 1 закрыт). Если запись ин- формации в триггер не происходит (момент времени t - t,), то он сохраняет свое предыдущее состояние, при этом узел 26 подзаряжается емкостным током от узла 24 через транзистор 3, а узел 25 разряжается до нулевого потенциала через транзисторы 2, 4 и 11. Разряд узла 25 до нулевого потенциала приводит к уменьшению емкости между первой тактовой шиной 5 и узлом 25 до величины емкости перекрытия затвор - сток, затвор - исток. Поэтому при уменьшении напряжения на тактовой шине 5 до нуля в узле 25 не

будет выброса напряжения обратной полярности, как в случае, если вместо форсирующих транзисторов 17 и 18 используются емкости. Затем во время действия тактового импульса Ф (2) происходит заряд узлов 24 и 25, при этом неосновные носители, накопленные под затворами нагрузочных транзисторов 3 и 4, рекомбинируют на источнике тактового напряжения. При записи противоположной информации в триггер процесс симметрично повторяется. Транзисторы 13, 14 считывания подключают выходы триггеров 15, 16 к узлам 26, 27 хранения через транзисторы 3, 4 только на время действия тактового импульса Р, (5), все остальное время информация на выхо- дах триггера остается неизменной.

В предложенном триггере исключена возможность логических состязаний сигналов записи за счет того, что третий и четвертый транзисторы 21,22 записи открыты в разные промежутки времени: транзистор 21 открыт в момент действия тактового импульса Pj , а транзистор 22 - в момент действия тактового импульса- Pj (фиг.2). Поэтому в любой момент времени триггер может установиться только в одно состояние. В данном триггере один из входов обладает приоритетом - вход 9 (фиг.1). Это означает, что если сигналы записи по обоим входам 8, 9 приходят за один период тактового генератора Т (промежуток времени на фиг.2), то на выходах 15, 16 триггера, подключенных в момент действия тактового импульса, состояния не изменяются - на выходе 15 остается логический О, а на выходе 16 - логическая 1. Исключение возможности логических состязаний увеличивает помехозащищенность триггера и повышает надежность его работы.

Формула изобретения

Триггер на МДП-транзисторах, содержащий первый и второй транзисторы хранения, причем затвор и сток первого транзистора хранения соединены со стоком и затвором второго транзистора хранения соответственно, первый и второй нагрузочные транзисторы, истоки которых соединены со стоками первого и второго транзисторов хранения соответственно, а затворы подклюJ 1

чены к первой тактовой шине триггера первый и второй транзисторы записи, истоки которых соединены со стоками первого и второго транзисторов храме кия соответстбенн-о, а стоки являются установочным входом и входом сброса триггера соответственно, отличающий ся тем, что, с целью повышения надежности работы, в триггер введены первый и второй разрядные транзисторы, стоки которых соединены с истоками первого и второго транзисторов хранения соответственно затворы подключены к первой тактовой шине триггера, а истоки - к второй тактовой пшне триггера, первый и вто рой транзисторы считывания, истоки которых соединены со стоками первого и второго нагрузочных транзисторов соответственно, затворы подключены к первой тактовой шине триггера, а сто ки являются прямым и инверсным выходами триггера соответственно, первый и второй форсирующие транзисторы, ис

п п п п п п . п п п п п п п ,

«51 П П П П П П П ,

30655токи и стоки которых подключены к

первой тактовой шине триггера, а затворы соединены со стоками первого и

второго нагрузочных транзисторов соответственно, первый и второй зарядные транзисторы, затворы и стоки которых подключены к второй тактовой шине триггера, а истоки соединены со

10 стоками первого и второго нагрузочных транзисторов соответственно, и третий и четвертый транзисторы записи, стоки которых соединены с истока- ми первого и второго транзисторов

15 хранения соответственно, затвор третьего и исток четвертого транзисторов записи подключены к третьей тактовой шине триггера, а затвор четвертого и исток третьего транзисторов

20 записи подключены к второй тактовой шине триггера, затворы первого и второго транзисторов записи соеди- .нены со стоками первого и второго транзисторов записи соответ25 ственно.

f

ге

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер на МДП-транзисторах | 1985 |

|

SU1330654A1 |

| Усилитель считывания | 1983 |

|

SU1134965A1 |

| Формирователь суммы на мдп-транзисторах | 1972 |

|

SU516038A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Запоминающий элемент | 1979 |

|

SU773738A1 |

| Статическая ячейка памяти на мдп- ТРАНзиСТОРАХ | 1979 |

|

SU799004A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Усилитель считывания для матрицы однотранзисторных запоминающих элементов | 1976 |

|

SU661605A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в интегральных устройствах динамической логики. Цель изобретения - повьппение надежности работы. Цель достигается за счет введения транзисторов 13, 14 считывания, разрядных транзисторов 10 и 11, фор- сируницих транзисторов 17 и 18, зарядных транзисторов 19 и 20, дополнительных транзисторов 21, 22 записи и второй 12 и третьей 23 тактовых шин, позволяющих исключить возможность логических состязаний сигналов записи, исключить паразитные ёмкостные выбросы и ускорить рекомбинаци- онные процессы в подпожке. 2 ил. i (Л с &0 со о Од ел ел срир.1

Редактор М.Келемеш

Составитель Д.Ковалдин

Техред М.ХоданичКорректор А.Зимокосов

. .

Заказ 3586/52

Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

.Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 0 |

|

SU277856A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| СПОСОБ ЗАЩИТЫ ОТ КОРРОЗИИ ЗОНЫ СВАРНОГО СОЕДИНЕНИЯ ТРУБОПРОВОДА | 1995 |

|

RU2103592C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

Авторы

Даты

1987-08-15—Публикация

1985-12-10—Подача