1

Изобретение относится к имлульспой технике.

Известно буферное устройство на МДПтранзисторах, содержащее инвертор с неперекрывающимися |фазами, инвертор с предзарядом, предвыходной и выходной каскады.

Целью изобретения является повышение бы-стродействия и расширение функциональных возможностей.

Для этого вход устройства соединен с входа.ми о:боих инверторов, а выход инвертора с неперекрывающимися фазами соединен с затвором разрядного транзистора выходного каскада, исток которого соединен с общим выводом, а сток - с выходом устройства, рричем выход инвертора с предзарядом соединен с затворами разрядных тран зисторов предвыходного каскада, истоки которых соединены с общей шиной, сток первого разрядного транзистора соединен с истоком первого зарядного транзистора, сток и затвор которого соединены с первой шиной импульсного наиряжения, и € затвором второго зарядного транзистора, сток которого соединен с второй щиной импульсного напряжения, а между его истоком и затвором включен конденсатор положительной обратной связи, причем исток второго зарядного транзистора соединен -со стоком второго разрядного транзистора и с затвором зарядного транзистора выходного каскада, сток

которого соединен с источником постоянного напряжения, а исток - с выходом устройства. Кроме того, исток первого разрядного транзистора соединен с первой шиной импульсного напряжения.

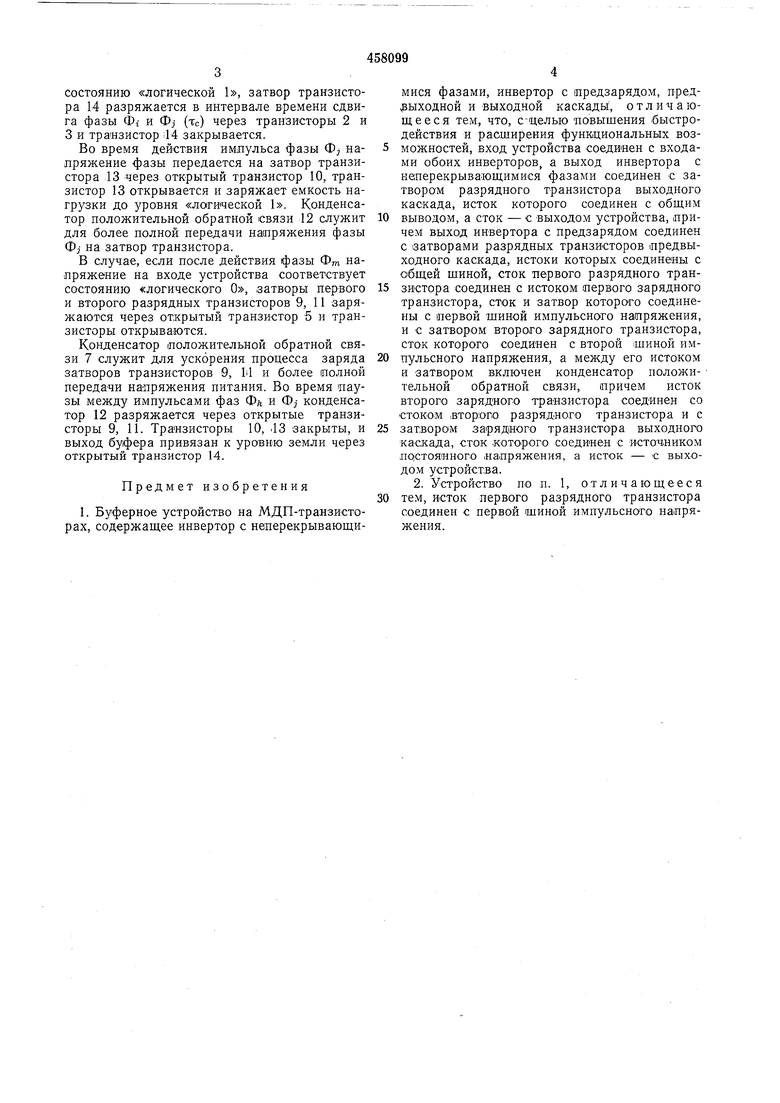

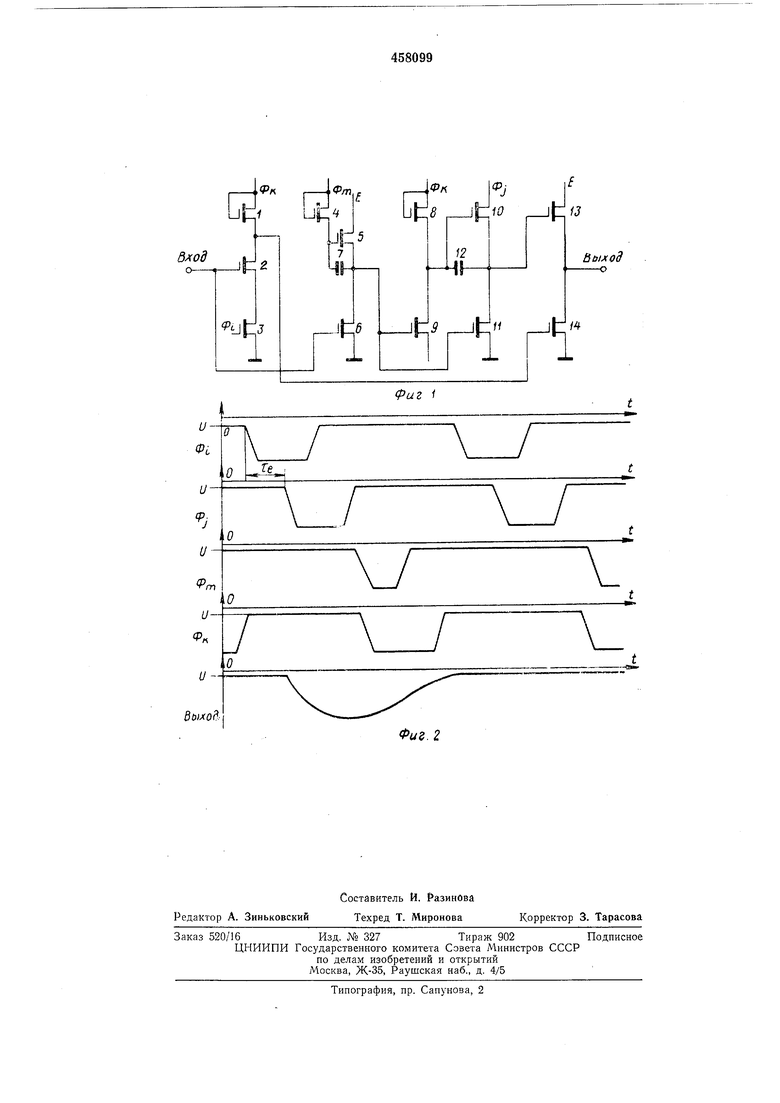

Изобретение пояснено чертежами.

На фиг. 1 приведена принципиальная электрическая схема устройства; на фиг. 2- последовательность фаз, необходимая для работы устройства.

Буферное устройство иа МДП-транзисторах содержит входной инвертор с неперекрывающимися фазами на транзисторах 1-3, инвертор с предзарядом на транзисторах 4-6 и конденсаторе обратной связи 7, предвыходной каскад на транзисторах 8-11 и конденсаторе обратной связи 12 и выходной каскад на транзисторах 13, 14.

Устройство работает следующим образом. Импульсом фазы Ф™ заряжается конденсатор 7 через транзисторы 4 и 6. Одновременно импульсом фазы Фk заряжается конденсатор 12 через зарядные транзисторы 8, 10 и разряжается распределенный копденсатор нагрузки через транзистор 14.

Транзистор 13 закрыт, так как напряжение на его затворе привязано к уровню зе.мли фазы Ф; через открытый транзистор 10.

В случае, если иосле действия фазы Ф,„ иапряжение иа входе устройства соответствует состоянию «логической 1, затвор транзистора 14 разряжается в интервале времени сдвига фазы Фг и Ф (тс) через транзисторы 2 и 3 и транзистор 14 закрывается. Во время действия имлульса фазы Ф напряжение фазы передается на затвор транзистора 13 через открытый транзистор 10, транзистор 13 открывается и заряжает емкость нагрузки до уровня «логической 1. Конденсатор положительной обратной связи 12 служит для более полной передачи напряжения фазы на затвор транзистора. В случае, если после действия фазы Фт напряжение на входе устройства соответствует состоянию «логического О, затворы первого и второго разрядных транзисторов 9, 11 заряжаются через открытый транзистор 5 и транзисторы открываются. Конденсатор положительной обратной связи 7 служит для ускорения пропесса заряда затворов транзисторов 9, Ы и более полной передачи напряжения питания. Во время паузы между импульсами фаз Фk и Ф-,- конденсатор 12 разряжается через открытые транзисторы 9, 11. Транзисторы 10, il3 закрыты, и выход буфера привязан к уровню земли через открытый транзистор 14. Предмет изобретения 1. Буферное устройство на МДП-транзисторах, содержащее инвертор с неперекрывающимися фазами, инвертор с предзарядом, пред,рыходной и выходной каскады, отличающееся тем, что, Сщелью повышения быстродействия и расширения функциональных возможностей, вход устройства соединен с входами обоих инверторов, а выход инвертора с неперекрывающимися фазами соединен с затвором разрядного транзистора выходного каскада, исток которого соединен с общим выводом, а сток - с выходом устройства, лричем выход инвертора с предзарядом соединен с затворами разрядных транзисторов лредвыходного каскада, истоки которых соединены с общей шиной, сток первого разрядного транзистора соединен с истоком первого зарядного транзистора, сток и затвор которого соединены с первой шиной импульсного напряжения, и с затвором второго зарядного транзистора, сток которого соединен с второй шиной импульсного напряжения, а между его истоком и затвором включен конденсатор положи- тельной обратной связи, причем исток второго зарядного транзистора соединен со стоком BTOpioro разрядного транзистора и с затвором зарядного транзистора выходного каскада, сток которого соединен с источником постояяного напряжения, а исток - с выходом устройства. 2. Устройство по п. 1, отличающееся тем, исток первого разрядного транзистора соединен с первой шиной импульсного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Устройство согласования на мпд-транзисторах | 1973 |

|

SU661797A1 |

| Генератор импульсов | 1973 |

|

SU561293A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| Формирователь импульсов на МОП-транзисторах | 1984 |

|

SU1236604A1 |

| Формирователь парафазных импульсов | 1981 |

|

SU984013A1 |

| Импульсный генератор (его варианты) | 1980 |

|

SU911693A1 |

| Запоминающая ячейка для регистра сдвига | 1974 |

|

SU519763A1 |

Авторы

Даты

1975-01-25—Публикация

1973-08-09—Подача