Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях при обработке чисел с плавающей точкой.

Целью изобретения является повышение точности вычислений за счет предварительной нормализации аргументов модуля комплексного числа,

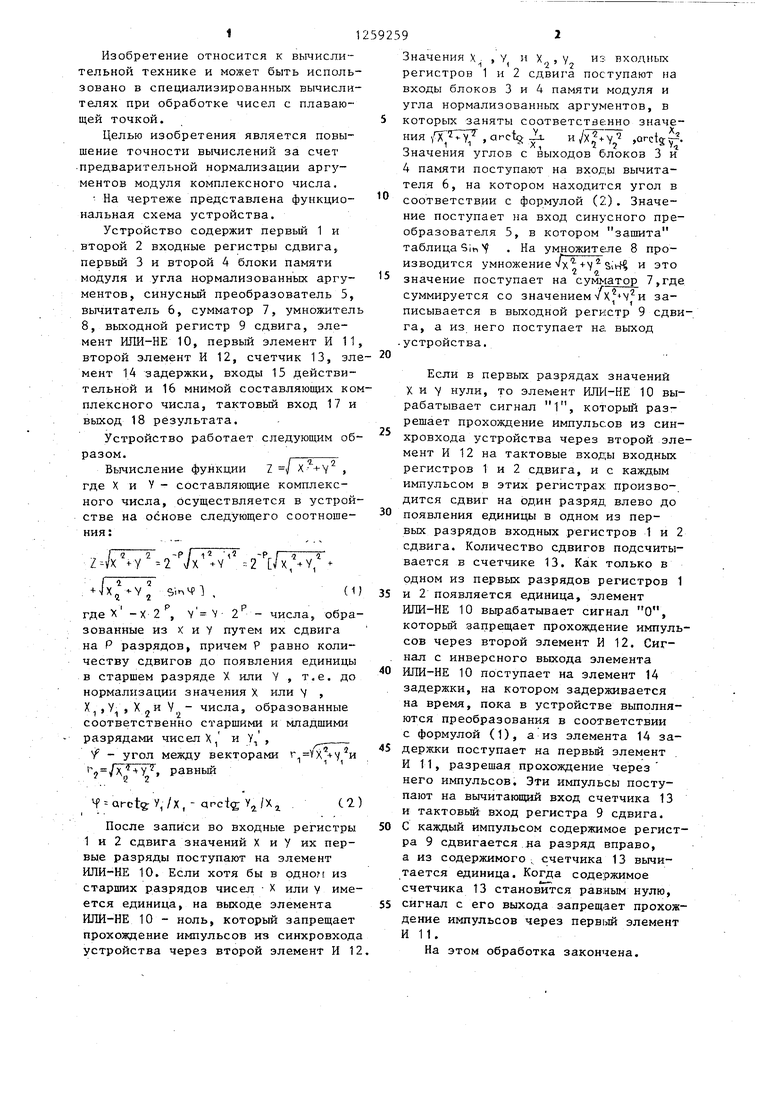

На чертеже представлена функциональная схема устройства.

Устройство содержит первый 1 и второй 2 входные регистры сдвига, первый 3 и второй 4 блоки памяти модуля и угла нормализованных аргументов, синусный преобразователь 5, вычитатель 6, сумматор 7, умножитель 8, выходной регистр 9 сдвига, элемент ИЛИ-НЕ 10, первый элемент И 11, второй элемент И 12, счетчик 13, зле мент 14 задержки, входы 15 действительной и 16 мнимой составляющих ком плексного числа, тактовый вход 17 и выход 18 результата.

Устройство работает следующим образом.

Вычисление функции

где X и V - составляющие комплексного числа, осуществляется в устройстве на основе следующего соотношения :

12 -,5 -Р Г -bV :--2 и

,(1)

гдеХ -х 2, 2 - числа, образованные из X и Y путем их сдвига на Р разрядов, причем Р равно количеству сдвигов до появления единицы в старшем разряде X или Y , т.е. до нормализации значения X или V X ,У , Х„и V, - числа, образованные соответственно старшими и млaдши lи

разрядами чисел X, и Y, ,

У - угол между векторами +у и г„ /х +Y, равный

/ г) 9

M arctey,/X,- ,/X,

С2)

После записи во входные регистры 1 и 2 сдвига значений X и у их первые разряды поступают на элемент ИЛИ-НЕ 10. Если хотя бы в одном из старших разрядов чисел X или у имеется единица, на выходе элемента ИЛИ-НЕ 10 ноль, который запрещает прохождение импульсов из синхровхода устройства через второй элемент И 12,

10

15

20

Значения X , У и X , у из входных регистров 1 и 2 сдвига поступают на входы блоков 3 и 4 памяти модуля и угла нормализованных аргументов, в которых заняты соответственно значения , arctg А И/х|Ту ,Qrctg. Значения углов с выходов блоков 3 и 4 памяти поступают на входы вычита- теля 6, на котором находится угол в соответствии с формулой (2). Значение поступает на вход синусного преобразователя 5, в котором зашита таблица Sin S . На умножителе 8 производится умножение Sih и это значение поступает на сумматор 7,где суммируется со значением и записывается в выходной регистр 9 сдвига, а из него поступает на выход .устройства.

Если в первых разрядах значений X и Y нули, то элемент ИЛИ-НЕ 10 вырабатывает сигнал 1, которьй разрешает прохождение импульсов из синхровхода устройства через второй элемент И 12 па тактовые входы входных регистров Т и 2 сдвига, и с каждым импульсом в этих регистрах производится сдвиг на один разряд влево до

появления единицы в одном из первых разрядов входных регистров 1 и 2 сдвига. Количество сдвигов подсчитывается в счетчике 13. Как только в одном из первых разрядов регистров 1

и 2 появляется единица, элемент ИЛИ-НЕ 10 вырабатывает сигнал О, который зацрещает прохождение импульсов через второй элемент И 12. Сиг- нал с инверсного выхода элемента

ИЛИ-НЕ 10 поступает на элемент 14 задержки, на котором задерживается на время, пока в устройстве выполняются преобразования в соответствии с формулой (1), а из элемента 14 задержки поступает на первьй элемент И 11, разрешая прохождение через него импульсов. Эти импульсы поступают на вычитающий вход счетчика 13 и тактовый вход регистра 9 сдвига.

С каждый импульсом содержимое регистра 9 сдвигается на разряд вправо, а из содержимого, счетчика 13 вычитается единица. Когда содержимое счетчика 13 становится равным нулю,

сигнал с его выхода запрещает прохождение импульсов через первый элемент И 11.

На этом обработка закончена.

Формула изобрете

Устройство для вычисления модуля комплексного числа, содержащее выходной регистр сдвига, сумматор, первый блок памяти модуля и угла нормализованных аргументов и умножитель, причем выход сумматора соединен с информационным входом выходного регистра сдвига, вькод значения модуля первого .блока памяти модуля и угла нормализованных аргументов соединен с входом первого сомножителя умножителя, отличающееся тем, что, с целью повышения точности вычислений за счет нормализации аргументов комплексного числа, в него дополнительно введены два входных регистра сдвига, вычитатель, счетчик элемент задержки, злемент ИЛИ-НЕ, дв злемента И, второй блок памяти модуля и угла нормализованных аргументов и синусный преобразователь, причем входы действительной и мнимой составляющих комплексного числа уст- ройства соединены с информационными входами соответственно первого и второго входных регистров сдвига, выходы старших разрядов первого и второго регистров сдвига соединены соответственно с первыми и-вторыми адресными входами второго блока памяти модуля и угла нормализованных аргументов, выходы младших разрядов первого и второго регистров сдвига сое- динены с первым и вторым адресными входами первого блока памяти модуля

Составитель С. Ку 1иков Редактор О. Юрковецкая Техред И.Попович Корректор Л. Тяско

Заказ 5122/46Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

2542

10

t5

, а 20 25 3035

594

и угла нормализованных аргументов, выходы значений угла первого и второго блоков памяти модуля и угла нормализованных аргументов соединены с входами соответственно вычитаемого и уменьшаемого вычитателя, выход которого соединен с входом синусного преобразователя, выход которого соединен с входом второго сомножителя умножителя, выход которого соединен . с входом первого слагаемого сумматора, вход второго слагаемого которого соединен с выходом значения модуля второго блока памяти модулл и угла нормализованных аргументов, тактовый вход выходного регистра сдвига соединен с выходом первого злемента И и входом вычитания счетчика, первый вход первого элемента И соединен через элемент задержки с инверсным выходом элемента ИЛИ-НЕ, прямой выход которого соединен с первым входом второго элемента И, второй йход которого соединен с тактирующим входом устройства и вторым входом первого элемента И, третий вход которого соединен с выходом сдвига счетчика, счетный вход которого соединен с вы- ходом второго элемента И и тактирующими входами первого и второго входных регистров сдвига, выходы двух старших разрядов которых соединены соответственно с первьм и вторым входами элемента ИЛИ-НЕ, выход выходного регистра сдвига является выходом результата устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для вычисления корня третьей степени | 1985 |

|

SU1288695A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1262486A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160429A1 |

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для возведения в степень | 1985 |

|

SU1290308A1 |

Изобретение относится к вычислительной технике и может быть применено в специализированных цифровых вычислителях для вычисления модели комплексного числа. Цель изобретения - повышение вычисления модуля комплексного числа за счет нормализации аргументов комплексного числа. Устройство для вычисления модуля комплексного числа содержит первый 1 и второй 2 входные регистры сдвига, первый 3 и второй 4 блоки памяти модуля и угла нормализованных аргументов, синусный преобразователь 5, вы- читатель 6, сумматор 7, умножитель 8, выходной регистр 9 сдвига, элемент ИЛИ-НЕ 10, первый элемент И 11, второй элемент И 12, счетчик 13 элемент 14 задержки, входы 15 действительной и 16 мнимой составляющих комплексного числа, тактовый вход 17, выход 18 результата. 1 ил. с е (Л с ivd ел Ф 1С ел о

| Устройство для вычисления квадратного корня из суммы квадратов двух чисел | 1981 |

|

SU997034A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для извлечения квадратного корня из суммы квадратов двух чисел | 1983 |

|

SU1101818A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-04-08—Подача