j о ел

00 GO СЛ

Изобретение относится к цифровой электроизмерительной технике и предназначено для аппаратурного определения в масштабе реального времени корреляционных функций случайных процессов.

Цель изобретения - расширение частотного диапазона обрабатываемых сигналов и упрощение устройства.

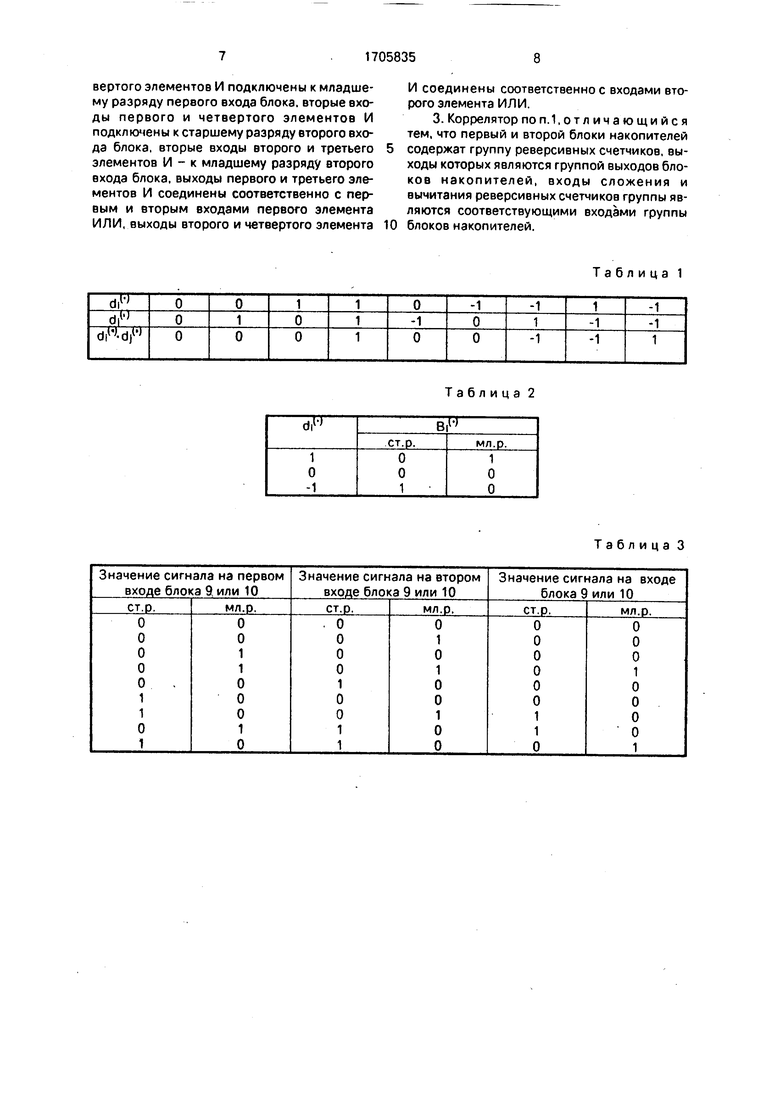

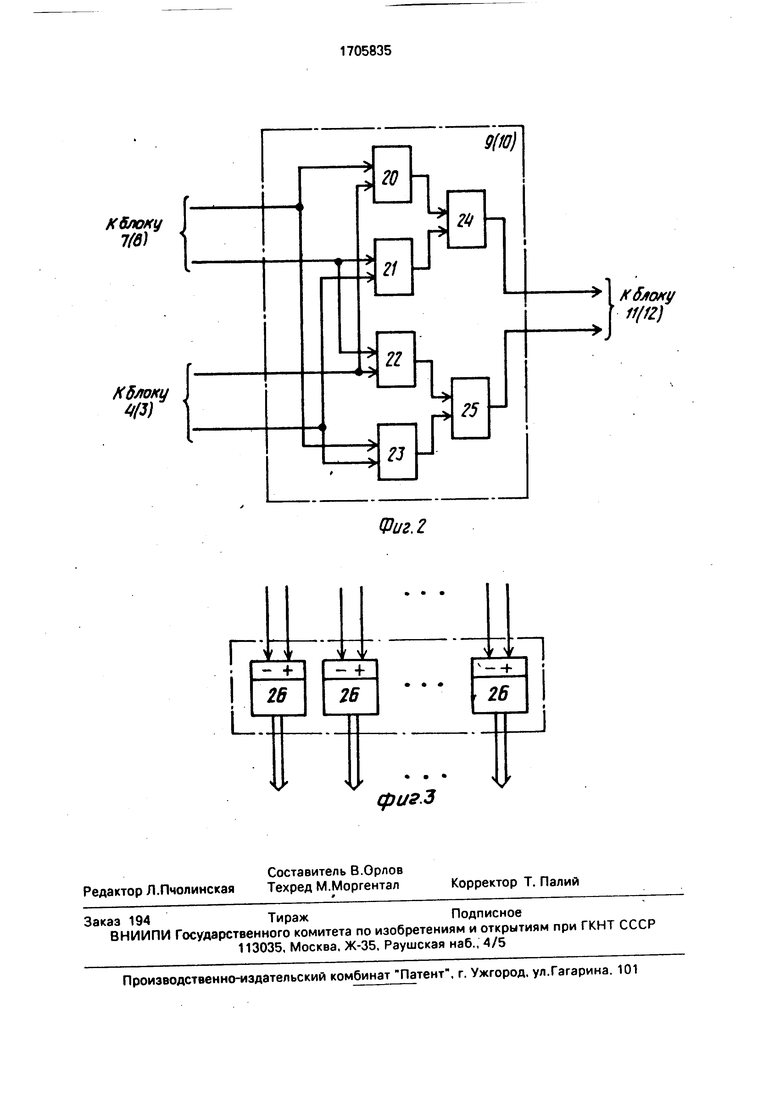

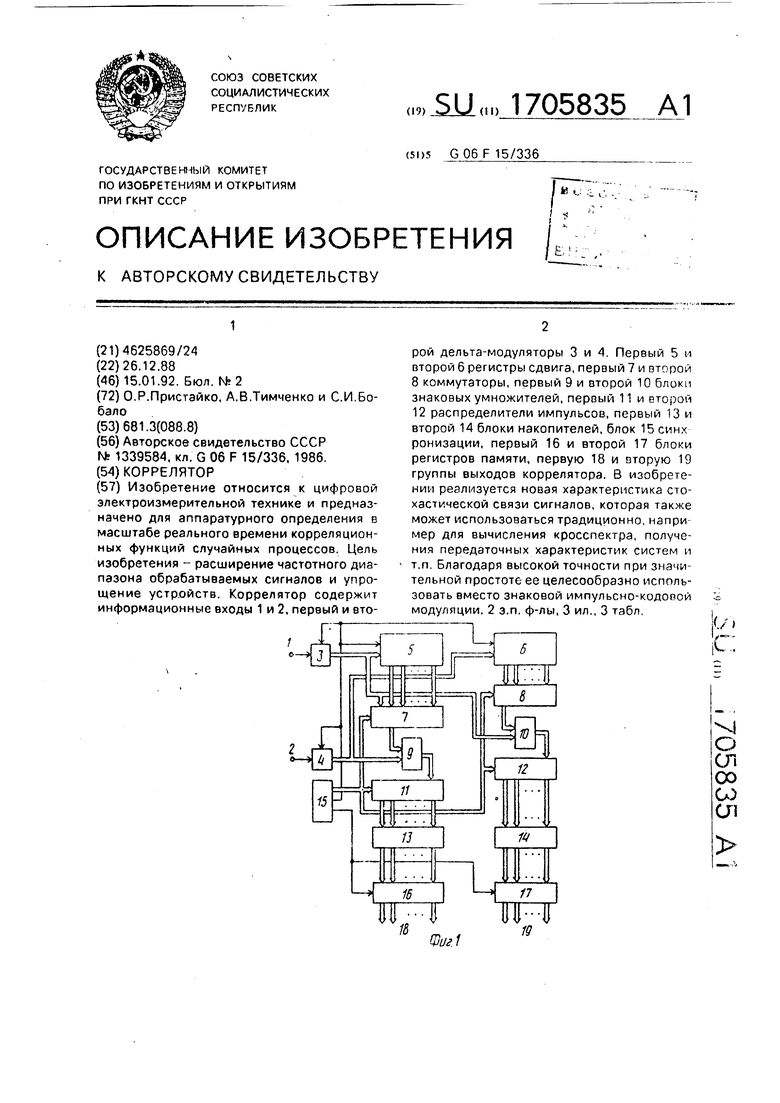

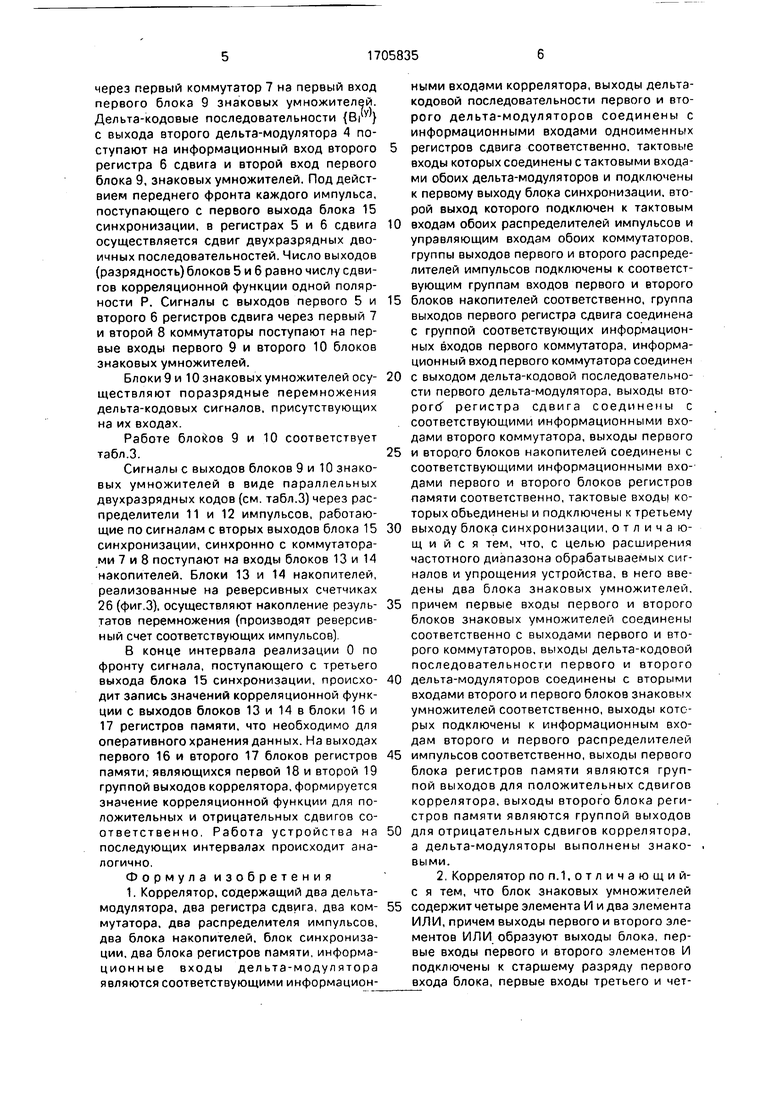

На фиг. 1 изображена структурная схема коррелятора; на фиг.2 - схема блока знаковых умножителей; на фиг.З - схема блока накопителей.

Коррелятор содержит первый 1 и второй 2 информационные входы, первый 3 и второй 4 знаковые дельта-модуляторы, первый 5 и второй б регистры сдвига, первый 7 и второй 8 коммутаторы, первый 9 и второй 10 блоки знаковых умножителей, первый 11 и второй 12 распределители импульсов, первый 13 и второй 14 блоки накопителей, блок 15 синхронизации, первый 16 и второй 17 блоки регистров памяти, первую 18 и вторую 19 группы выходов коррелятора.

Блок знаковых умножителей 9 (10) состоит из четырех элементов И 20-23 и двух элементов ИЛИ 24 и 25.

Блок накопителей 13 (14) выполнен на реверсивных счетчиках 26.

В корреляторе реализуется новая характеристика стохастической связи сигналов, которая может быть использована и традиционно. Благодаря высокой точности при значительной простоте ее целесообразно использовать вместо знаковой импульс- но-кодовой модуляции.

Реализуется следующий алгоритм вычисления кросскорреляционной функции к двух входных сигналов x(t) и y(t):

«r(m) X dЈx) dWm0)

k 1

для положительных сдвигов ,1,.... P, и

14-lmL ч , s m) 2dkx)dM.m(2)

k 1

для отрицательных сдвигов mf{-P...., -1.

В (1) и (2) {dk(x)} и {dk(y)} Vdk(0t {-1.0,1} являются знаковыми дельта-кодовыми последовательностями входных сигналов x(t) и y(t) и формируются по правилу:

P, Х| -Xi-i Ј

di

,М

-|0 ,-Ј Х| -Х|-м Ј -1,Х| -Х|-1 -Ј

Л.У d|(y) 0 ,-Ј yi -yi-| Ј

-yi-н -с 1. N;

N ENT(0/T).

(3)

$иТ - интервал реализации и частота дискретизации входных сигналов соответственно;

{xi}, {yi} - отсчеты входных сигналов.

Алгоритм (3) предусматривает запоминание текущих отсчетов входных сигналов на время Т 1/Т , формирование разностных сигналов yxi xi-xi-i и 7yi yi-yi-i. их сравнение с соответствующими порогами

ЈИ-Ј , определяющими разрешающую способность метода.

Коды {dr } несут информацию о знаке разности между текущими и задержанными отсчетами входных сигналов и позволяют

выявить характер изменения последних. Появление положительной единицы в знаковой дельта-кодовой последовательности свидетельствует о росте входного сигнала; отрицательной - о спаде входного сигнала;

нуля - о постоянстве входного сигнала в пределах выбранного разностного окна {-Ј,Ј} Таким образом, знаковые дельта- модулированные сигналы не несут какой- либо количественной информации о

величине входного сигнала, а указывают лишь на его характер изменения (поведение). Поэтому согласно теории информации частота следования знаковых дельтэ-моду- лированных сигналов может быть равна частоте Найквиста.

Перемножение знаковых дельта-кодов осуществляется в соответствии с табл.1.

Таким образом, в алгоритмах (1) и (2) оперируют знаками приростов, а не отсчетами входных сигналов, что имело место в корреляторах с импульсно-кодовой модуляцией, или взаимосвязанными шагами квантования как при линейной дельта-модуляции. Приведенный алгоритм реализуется в

предлагаемом устройстве следующим образом.

Входные сигналы x(t) и y(t) с входов 1 и 2 коррелятора поступают на информационные входы первого 3 и второго 4 дельта-модуляторов. С помощью тактовых импульсов, поступающих с первого выхода блока 15 синхронизации, в модуляторах 3 и 4 осуществляется преобразование аналоговых сигналов в знаковые дельта-кодовые

последовательности {di }, согласно алгоритму (3). При этом троичные дельта-кодовые символы преобразуются в двухразрядные двоичные кодовые слова в соответствии с табл.2.

Знаковые дельта-кодовые последовательности {Вгх } с выхода первого дельта-модулятора 3 поступают на информационный вход первого регистра 5 сдвига, второй вход второго блока 10 знаковых умножителей и

через первый коммутатор 7 на первый вход первого блока 9 знаковых умножителей. Дельта-кодовые последовательности {Вг } с выхода второго дельта-модулятора 4 поступают на информационный вход второго регистра 6 сдвига и второй вход первого блока 9, знаковых умножителей. Под действием переднего фронта каждого импульса, поступающего с первого выхода блока 15 синхронизации, в регистрах 5 и 6 сдвига осуществляется сдвиг двухразрядных двоичных последовательностей. Число выходов (разрядность) блоков 5 и 6 равно числу сдвигов корреляционной функции одной полярности Р. Сигналы с выходов первого 5 и второго 6 регистров сдвига через первый 7 и второй 8 коммутаторы поступают на первые входы первого 9 и второго 10 блоков знаковых умножителей.

Блоки 9 и 10 знаковых умножителей осу- ществляют поразрядные перемножения дельта-кодовых сигналов, присутствующих на их входах.

Работе блоков 9 и 10 соответствует табл.3.

Сигналы с выходов блоков 9 и 10 знаковых умножителей в виде параллельных двухразрядных кодов (см. табл.3) через распределители 11 и 12 импульсов, работающие по сигналам с вторых выходов блока 15 синхронизации, синхронно с коммутаторами 7 и 8 поступают на входы блоков 13 и 14 накопителей. Блоки 13 и 14 накопителей, реализованные на реверсивных счетчиках 26 (фиг.З). осуществляют накопление резуль- татов перемножения (производят реверсивный счет соответствующих импульсов).

В конце интервала реализации 0 по фронту сигнала, поступающего с третьего выхода блока 15 синхронизации, происхо- дит запись значений корреляционной функции с выходов блоков 13 и 14 в блоки 16 и 17 регистров памяти, что необходимо для оперативного хранения данных. На выходах первого 16 и второго 17 блоков регистров памяти, являющихся первой 18 и второй 19 группой выходов коррелятора, формируется значение корреляционной функции для положительных и отрицательных сдвигов соответственно. Работа устройства на последующих интервалах происходит аналогично.

Формулаизобретения

1. Коррелятор, содержащий два дельта- модулятора, два регистра сдвига, два ком- мутатора. два распределителя импульсов, два блока накопителей, блок синхронизации, два блока регистров памяти, информа- ционные входы дельта-модулятора являются соответствующими информационными входами коррелятора, выходы дельта- кодовой последовательности первого и второго дельта-модуляторов соединены с информационными входами одноименных регистров сдвига соответственно, тактовые входы которых соединены с тактовыми входами обоих дельта-модуляторов и подключены к первому выходу блока синхронизации, второй выход которого подключен к тактовым входам обоих распределителей импульсов и управляющим входам обоих коммутаторов, группы выходов первого и второго распределителей импульсов подключены к соответствующим группам входов первого и второго блоков накопителей соответственно, группа выходов первого регистра сдвига соединена с группой соответствующих информационных входов первого коммутатора, информационный вход первого коммутатора соединен с выходом дельта-кодовой последовательности первого дельта-модулятора, выходы второго регистра сдвига соединены с соответствующими информационными входами второго коммутатора, выходы первого и второго блоков накопителей соединены с соответствующими информационными входами первого и второго блоков регистров памяти соответственно, тактовые входы которых объединены и подключены к третьему выходу блока синхронизации, отличающийся тем, что, с целью расширения частотного диапазона обрабатываемых сигналов и упрощения устройства, в него введены два блока знаковых умножителей, причем первые входы первого и второго блоков знаковых умножителей соединены соответственно с выходами первого и второго коммутаторов, выходы дельта-кодовой последовательности первого и второго дельта-модуляторов соединены с вторыми входами второго и первого блоков знаковых умножителей соответственно, выходы которых подключены к информационным входам второго и первого распределителей импульсов соответственно, выходы первого блока регистров памяти являются группой выходов для положительных сдвигов коррелятора, выходы второго блока регистров памяти являются группой выходов для отрицательных сдвигов коррелятора, а дельта-модуляторы выполнены знаковыми.

2. Коррелятор поп.1,отличающий- с я тем, что блок знаковых умножителей содержит четыре элемента И и два элемента ИЛИ, причем выходы первого и второго элементов ИЛИ образуют выходы блока, первые входы первого и второго элементов И подключены к старшему разряду первого входа блока, первые входы третьего и четвертого элементов И подключены к младшему разряду первого входа блока, вторые входы первого и четвертого элементов И подключены к старшему разряду второго входа блока, вторые входы второго и третьего элементов И - к младшему разряду второго входа блока, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами первого элемента ИЛИ, выходы второго и четвертого элемента

И соединены соответственное входами второго элемента ИЛИ.

3. Коррелятор по п. 1, о т л и ч а ю щ и и с я тем, что первый и второй блоки накопителей содержат группу реверсивных счетчиков, выходы которых являются группой выходов блоков накопителей, входы сложения и вычитания реверсивных счетчиков группы являются соответствующими входами группы блоков накопителей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1986 |

|

SU1339584A1 |

| Коррелятор | 1985 |

|

SU1262522A1 |

| Коррелятор | 1986 |

|

SU1425711A1 |

| Адаптивный автокоррелятор | 1990 |

|

SU1774345A1 |

| Дельта-модулятор | 1987 |

|

SU1425838A1 |

| Устройство для определения заданной ординаты корреляционной функции | 1990 |

|

SU1777152A1 |

| Коррелятор | 1978 |

|

SU781820A1 |

| Телеметрическая система | 1989 |

|

SU1679515A1 |

| Цифровой фильтр с дельта-модуляцией | 1988 |

|

SU1527713A1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

Изобретение относится к цифровой электроизмерительной технике и предназначено для аппаратурного определения в масштабе реального времени корреляционных функций случайных процессов. Цель изобретения - расширение частотного диапазона обрабатываемых сигналов и упрощение устройств. Коррелятор содержит информационные входы 1 и 2, первый и второй дельта-модуляторы 3 и 4. Первый 5 и второй 6 регистры сдвига, первый 7 и второй 8 коммутаторы, первый 9 и второй 10 блоки знаковых умножителей, первый 11 и етсфой 12 распределители импульсов, первый 13 и второй 14 блоки накопителей, блок 15 синх ронизации, первый 16 и второй 17 блоки регистров памяти, первую 18 и вторую 19 группы выходов коррелятора. В изобретении реализуется новая характеристика стохастической связи сигналов, которая также может использоваться традиционно, например для вычисления кросспектра, получения передаточных характеристик систем и т.п. Благодаря высокой точности при значительной простоте ее целесообразно использовать вместо знаковой импуяьсно-кодовой модуляции. 2 э.п. ф-лы, 3 ил., 3 табл. К./ с:

Таблица 1

Таблица 2

Таблица 3

Г

t

- +

- +

2В

26

Фиг. Z

V t

ч--ь

С1

26

| Коррелятор | 1986 |

|

SU1339584A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-15—Публикация

1988-12-26—Подача