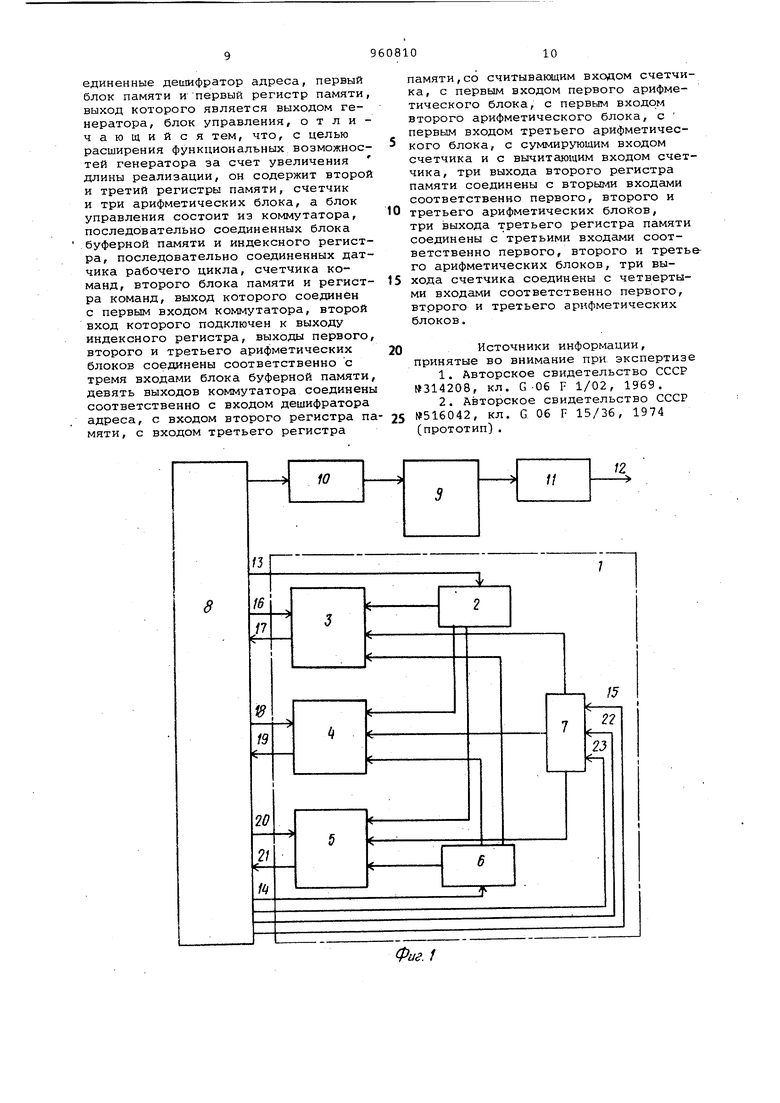

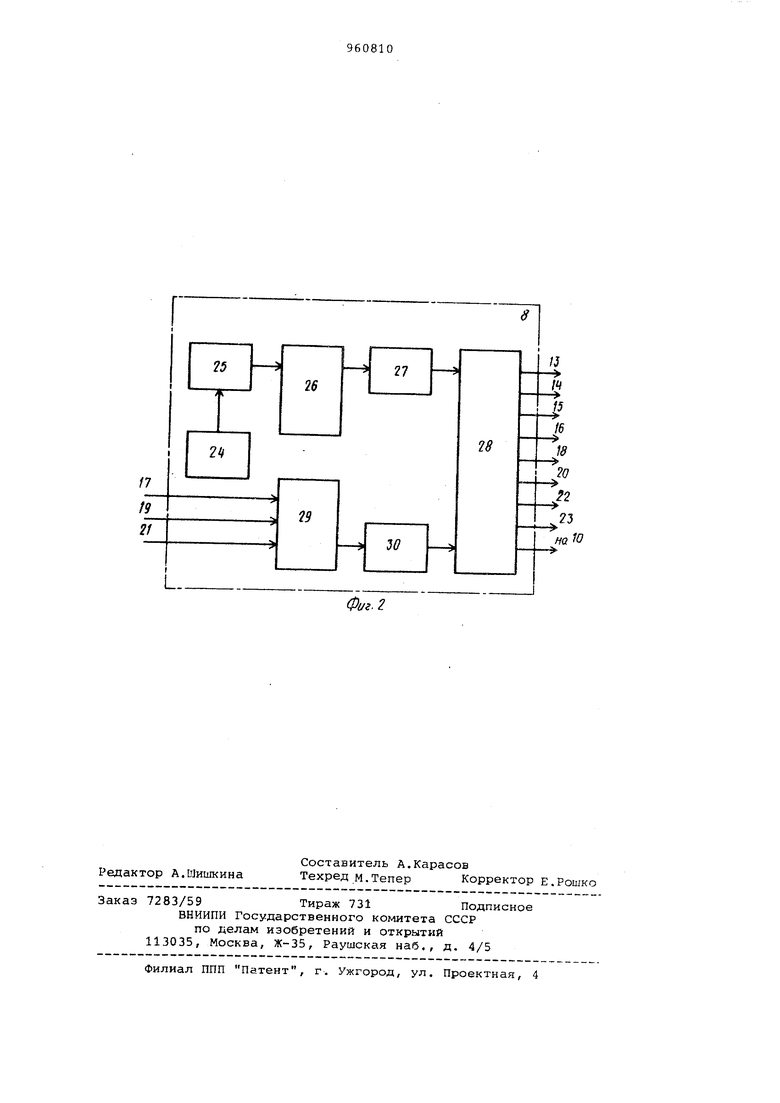

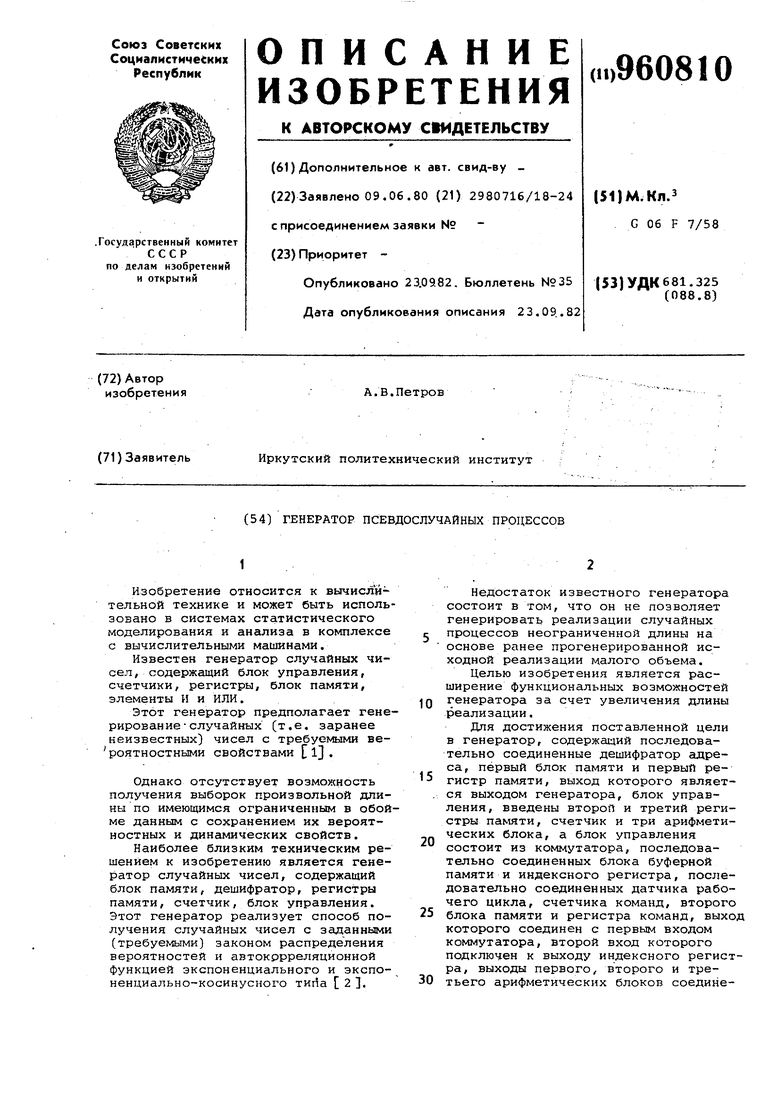

ны соответственно с тремя входами блока буферной памяти, девять выходо коммутатора соединены соответственно с входом дешифратора адреса, с входом второго регистра памяти, с входом третьего регистра памяти, со считывающим в;:одом счетчика, с перBFJM входом первого арифметического блока, с первым входом второго арифметического блока, с первым входом третьего арифметического блока, с cy лмиpyющим входом счетчика и с вычитающим входом счетчика, три выхода второго регистра памяти соединены с вторьп/1И входами соответственно первого, второго и третьего арифметических блоков, три выхода третьего регистра памяти соединены с третьими входами соответственно первого, втор го и третьего арифметических блоков три выхода счетчика соединены с четвертыми входами соответственно первого, второго и третьего арифметических блоков., На фиг. 1 приведена блок-схема генератора; на фиг. 2 - схема блока управления. Генератор включает блок 1 выбора ячейки блока памяти, содержащий регистр 2 памяти, первый 3, второй 4 и третий 5 арифметические блоки, регистр б памяти, счетчик 7. Кроме того, генератор содержит блок 8 управления, блок 9 памяти, входкоторого соединен с выходом дешифратчэра 10 адреса,- а выход - через регистр 11 памяти - с выходом 12 генератора. Выходы 13-16 блока управления соединены с входами регистров 2 и б памяти, счетчика 7 и первого арифметичес кого блока 3 выход 17 которого соединен с входом блока 8 управления, выход 18 которого соединен с входом второго арифметического блока 4, выход 19 которого соединен с входом блока 8 управления, выход 20 которого соединен с входом третьего арифметического блока 5.- выход 21 которо го соединен с входом блока 8 управления, выходы 22 и 23 которого соеди нены соответственно с суммирующим и вычитающим входами счетчика 7. Кроме того, выход блока 8 управления соединен с входом дешифратора 10 адреса. Входы каждого арифметического блока соединены соответстве но с выходами регистров 2 и 6 памят и счетчика 7. Блок 8 управления (фиг.2) содержит последовательно соединенные дат чик 24 рабочего цикла, счетчик 25 циклов, блок 26 памяти, регистр 27 команд и коммутатор 28, а также последовательно соединенные блок 29 б ферной памяти и инлексный регистр 30. выход которого соединен с други входом .1yтaтopa. Принцип работЕл генератора состоит в получегнии реализаций псевдослучайного процесса произвольной длины до ограниченной в объеме исходной реализации с сохранением ее динамических свойств. Иными словами, не ставится цель генерировать случайное-, ти с новыми статистическими свойствами, а предлагается просто увеличить объем исходной выборки путем многократного повторения отрезков исходной реализации фиксированной длины. Это позволяет получать (и в этом смысле генерировать) неограниченные по длине реализации псевдослучайные процессы с известными динамическими (корреляционными и спектральными) свойствами, В соответствии с этим генератор не содержит никаких блоков, задающих и определяющих новые статистические свойства генерируемого процесса. Для генерирования достаточно лишь в первом блоке памяти иметь значения исходной реализации и ее отрезки фиксированной длины передавать на выходную шину устройства . Арифметические блоки имеют следующее назначение. Первый арифметический блок 3 вычисляет количество изменений порядка формирования адреса дешифратором 10 адреса. Под изменением порядка формирования понимается изм ченке на противоположный порядка отсчета адресов. Если адреса первого блока памяти изменяются в сторону увеличения, то противоположное .;у к ;-нение адресов - их уменьшение. Алгоритм работы первого арифметического блока 3 имеет следугащиГ вид.Пусть k- количество чисел исходной реализации, подлежащей передаче на выходную шину (содержимое регистра 2); Н.- объем исходной реализации (содержимое регистра 6); А - текущий номер ячейки первого блока памяти, из которой выбрано последнее число выходной реализации (содерхсимое счетчика 7)V В - число изменений порядка формирования адреса де 1;ифра :ором 10 адреса. Шаг 1. Вычисляется В О и С А + , Шаг 2. Проверяется условие С Н. Если оно выполняется, производится переход к шагу 5, в противном случае (С И) - к шагу 3. Иаг 3 . Вычисляется C C-kHB В 4--1. Шаг 4. Осуществляется переход к .шагу 2 . Шаг 5. Производится передача вычисленного значения В на выходную шину 17 первого арифметического блока 3 . Второй арифметический OJIOK 4 вычисляет количество ячеек блока 9

памяти, содержимое которого передается через регистр 11 на выходную шину 12 при увеличении адресов ячеек блока памяти. Для. этого-из содержимого регистра 6 (объем исходной реализацил) вычитается содержимое счетчика 7 (номер ячейки запоминающего устройства, из которой выбрано последнее число выходной реализации .

Результат вычитания подается по выходной шине Д 9 второго арифмети-ческого блока 4 в блок 8 управления при условии, что он менее количества ячеек, подлежащих передаче на выходную шину (содержимого регистра -2). В противном случае результатом работы второго арифметического блока будет содержимое регистра 2.

Третий арифметический блок 5 вычисляет количество ячеек блока 9 памяти, содержимое которого переда- ется через регистр 1.1 на выходную шину 12 при уменьшении адресов ячеек запоминающего устройства. Результатом работы третьего арифметического блока будет номер ячейки блокапамяти, из которого выбрано последнее .число выходной реализации, уменьшенное на единицу, если этот номер меньше количества чисел, подлежащих передаче на выходную шину . (содержимое регистра 2). В противном случае результатом работы третьего арифметиче-ско.го блока будет содержимое регистра 2.

Блок 8 управления работает следующим образом. .

Датчик 24 рабочего циюла предназначен для выборки управляемых сигналов, определяющих рабочий цикл устройства - такт генерирования случайных чисел.Иными словами, он предназначен для генерации тактовых импульсов устройства-.

Блок 26 памяти содержит жестко закрепленную и предназначенную только :-для данного генератора программу, выраже.нную в командах, кахсдая из которых записана в определенную ячейку блока памяти. Эта программа определяет работу всето генератора на каждом такте его работы.

Счетчик 25 определяет в зависимости

от тактовых, импульсов, генерируемых датчиком рабочего цикла, ячейку блока памяти, содержащую команду, подлежащую выполнению. Регистр 27 команд предназначен для приема и хранения команды, подлежащей выполнению. Коммутатор 28 преобразует команду в управляющий сигнал на выходных шинах блока управления и обеспечивает автоматическое управление работой всего устройства. Причем выбор шины осуществляется также автоматически

в зависимости от кода команды.

Буферный блок 29 памяти предназначен для приема входных сигналов блока управления, причем в зависимости от того, на какой шине появляется сигнал, осуществляется, выдача содержимого соответствующей ячейки буферного блока памяти в индексный регистр.

Индексный регистр предназначен для приема, хранения и выдачи кодов, используемых в дальнейшем для моди-т фикации команд в коммутаторе операций и переадресации управляющего сигнала с одной выходной шины блока управления .на другую.

Таким образом, логика работы генератора псевдослучайных процессов полностью определяется набором команд (программой), записанной в . блоке 26 памятей, и набор этих команд однозначно представлен в описании изобретения.

Генератор работа.ет следующим образом.

УпраЬляющие сигналы по шинам ISIS вызывают передачу содержимого

5 регистра 2 (количество чисел исходной реализации за один такт .работы генератора), содержимого регистра б (объем исходной реализации, хранящийся в блоке 9 памяти) и содержимо0г6 счетчика 7 (текущего номера ячейки блока 9, из.которого выбрано последнее число выходной реализации) в первый, второй и третий арифметические блоки. По. управл-яющему сигналу на

5 шине 16 первый арифметический блок 3 вычисляет количество изменений порядка формирования адреса дешифратором 10 адреса и передает это число по мине 17 в блок 8 управления.

0 По управляющему сигналу на шине

18второй арифметический блок 4 вычисляет и передает по шине 19 в блок 8 управления число ячеек блока 9 памяти, содержимое которого переда5ется через -регистр 11 на выходную шину 12 при увеличении адресов ячеек блока 9 памяти. По управляющему, сигналу на шине 20 третий арифметический блок 5 вычисляет и передает по шине 21 в блок 8 управления число

0 ячеек блока 9 памяти, содержимое которых передается через регистр 11 .на выходную шину 12 при уменьшении адресов блока 9 памяти.

5

Выработка сигнала-отклика на шине

19вызывает передачу из блока 9 памяти через регистр 11 на выходную шину 12 рассчитанного вторым арифметическим- блоком 4 числа значений

0 исходной реализации. Причем параллельно с передачей каждого случайного числа на выходную шину 12 производится увеличение содержимого счетчика 7 посредством .счетного им5пульса на шине 22. Акт передачи

содержимого заданного количества ячеек блока 9 памяти при возрастании адресов завершается вычитанием единицы из информационного сигнала на шине 17 (числа изменений порядка формирования адреса дешифратором 10 адреса). Если число изменений порядка формирования адреса неотрицательно или отсутствует сигнал-отклик на шине 19, то по сигналу на шине 21 производится передача из блока 9 памяти через регистр 11 аа выходную шину 12 рассчитанного третьим арифметическим блоком 5 числа значений исходной реализации. При этом производится уменьшение содержимого счетчика 7 посредством счетного импульса на 23. Отсутствие сигнала-отклика на шине 21 приводит к окончанию такта генерирования. Акт передачи содержимого заданного числа ячеек блока 9 памяти при уменьшении адресов завершается вычитанием единицы из информационного сигнала на шине 17 (числа изменений порядка формирования адреса дешифратором 10 адреса) .

Затем, если число изменений порядка формирования адреса неотрицательно, то осуществляется передача содержимого всех заполненных исходной реализацией ячеек блока 9 памяти. При этом адреса ячеек блока 9 памяти увеличиваются на единицу с .одновременным и параллельным увеличением содержимого счетчика 7 на единицу посредством счетного импульса на шине 22. Акт передачи содержимого всех ячеек блока 9 памяти при возрастании адресов завершается вычитанием единицы из информационного сигнала на шине 17 .

Далее, если число изменений порядка формирозания адреса неотрицательно, осуществляется передача содержимого всех заполненных исходной реализацией ячеек блока 9 памяти при уменьшении адресов ячеек на единицу с одновременным уманьшением содержимого счетчика 7.посредством счетного импульса на шине 23. Акт передачи содержимого всех ячеек блока 9 памяти при убывании адресов завершается вычитанием единицы из информационного сигнала на шине 17

Такт генерирования очередной порции выходного псевдослучайного процесс& на основе хранящейся в блоке 9 памяти исходной реализации заканчивается при отрицательном сигнале на шине 17.

Таким образом, осуществляется генерирование реализации псевдослучайных процессов произвольной длины по ограниченной в объеме исходной реализации о сохранением ее динат-иическкх свойств.

Рассмотрим алгоритм работы устройства на примере.

Пусть в блоке памяти хранится исходная реализация объемом Н 5, т.е регистр содержит число 5, а значения выборки находятся в ячейках блока памяти с номерами 1, 2, 3, 4 и 5, соответствующими адресам ячеек. Пусть также количество чисел выходной реализации, подлежащей передаче на выходную шину за один такт генерирования, или содержимое регистра 2 равно 6 (k 6). Текущий адрес ячейки блока памяти, из которой выбрано последнее число выходной реали зации, равен А 3,

Количество изменений порядка формирования адреса В 1, так как А + + k Н (975) HA + k-KfH (3 5).

Количество чисел, переписываек1ых при увеличении адресов, равно k 2. Соответственно на выходную шину передается содержимое 4 и 5-й ячеек памяти и устанавливается А 5 Hk .

Затем, в связи с тем, что В О, вычи сляется В В-1 Ои определяется число ячеек, переписываемых при уменьшении адресов ячеек блока памяти: (4 5), то k 4.

Содержимое ячеек с номерами 4, 3, 2 и 1 передается на выходную хиину, Устанавливается k k - k О и А 1.

Так как В О и k О, такт генерирования заканчивается, Hci выходной шине получается последоват -льность чисел исходной реализации, хранящейся в ячейках 4, 5, 4, 3, 2 и 1.

Копирование исходной реализации отрезками ааданной длины позволяет сохранить в выходном псевдослучайном процессе динамические свойства, присущие исходной информации, и существенно снизить затраты, производимые при сборе, статистических данных.

Технико-экономическая эффективность изобретения при проведении технологических экспериментов на обогатительной фабрике Коршуновского ГОКа при 100 опытах, с целью накопления достоверных статистических данных для одного технологического эксперимента, стоимости проведения одного опыта (заработная плата обслуживающего персонала с учетом районного коэффициента 1,4,стоимость реактивов, энергозатраты и т.д.) 10 руб, общем количестве экспериментов, проводимых на обогатительной фабрике примерно 30, составит 15 тыс. руб.

Формула изобретения

Генератор псевдослучайных процессов, содержащий посладовательно соединенные дешифратор адреса, первый блок памяти ипервый регистр памяти, выход которого является выходом генератора, блок управления, отличающийся тем, что, с целью расширения функциональных возможностей генератора за счет увеличения длины реализации, он содержит второй и третий регистры памяти, счетчик и три арифметических блока, а блок управления состоит из коммутатора, последовательно соединенных блока буферной памяти и индексного регистра, последовательно соединенных датчика рабочего цикла, счетчика команд, второго блока памяти и регистра команд, выход которого соединен с первым входом коммутатора, второй вход которого подключен к выходу индексного регистра, выходы первого, второго и третьего арифметических блоков соединены соответственно с тремя входами блока буферной памяти, девять выходов коммутатора соединены соответственно с входом дешифратора адреса, с входом второго регистра памяти, с входом третьего регистра

памяти,со считывающим входом счетчика, с первым входом первого арифметического блока, с первьлм входом второго арифметического блока, с первым входом третьего арифметического блока, с суммирующим входом

счетчика и с вычитающим входом счетчика, три выхода второго регистра памяти соединены с вторыми входами соответственно первого, второго и

третьего арифметических блоков,

три выхода третьего регистра памяти соединены с третьими входами соответственно первого, второго и третьего арифметических блоков, три выхода счетчика соединены с четвертыми входами соответственно первого, втррого и третьего арифметических блоков.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР 314208, кл. G -06 F 1/02, 1969.

2.Авторское свидетельство СССР №516042, кл. G 06 F 15/36, 1974

(прототип).

1Z

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных процессов | 1984 |

|

SU1261087A1 |

| Устройство для программного управления | 1980 |

|

SU881676A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

Авторы

Даты

1982-09-23—Публикация

1980-06-09—Подача