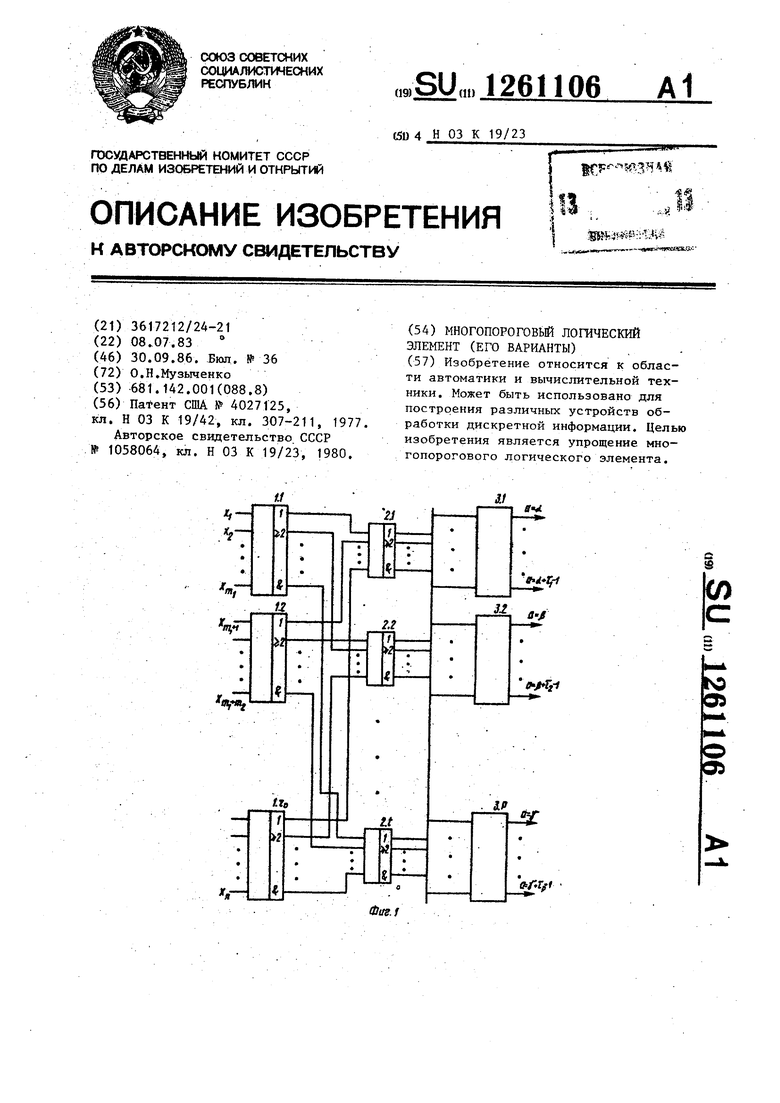

Устройство содержит г 5 2 преобразо вателей 1,1-1.г весов m (,т2,..,. ,тр входов,преобразователи,2.1-2,t весов входов,, по числу групп преобразователей 1.1-1.г с одинаковыми весами, блоюс 3.1-З.р формирования группы с 2 выходов. Поставленная цель достигается предложенными в

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации.

Цель изобретения - упрощение многопорогового логического элемента.

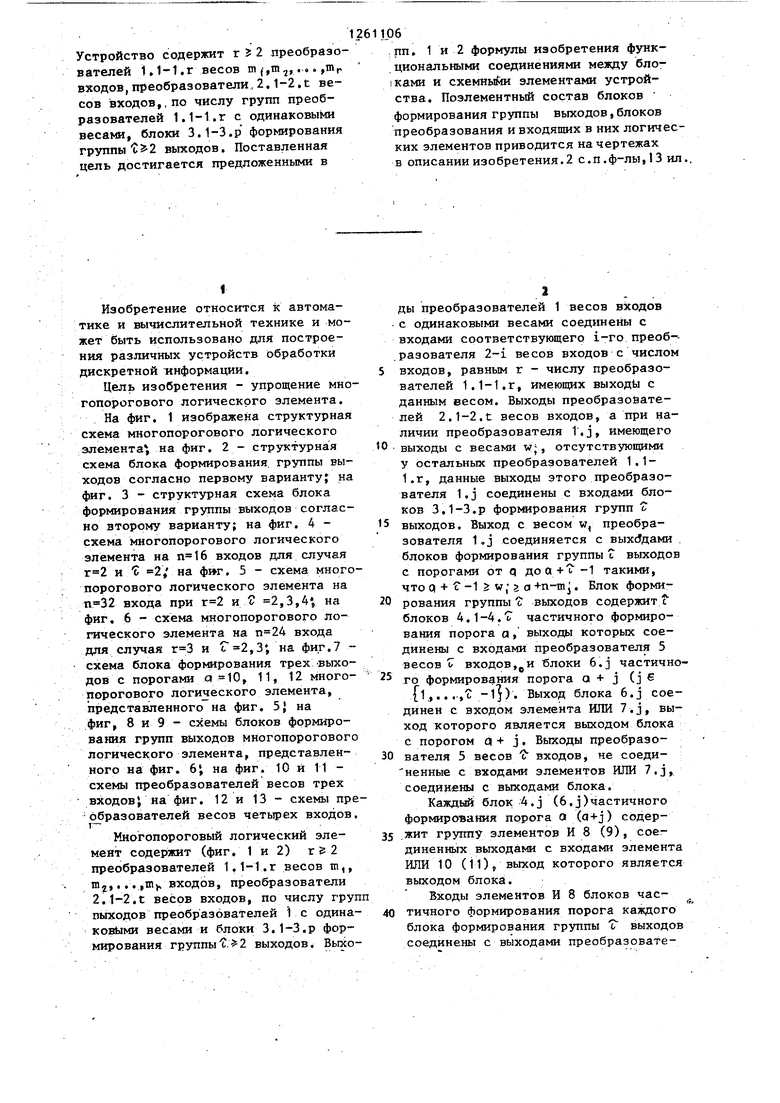

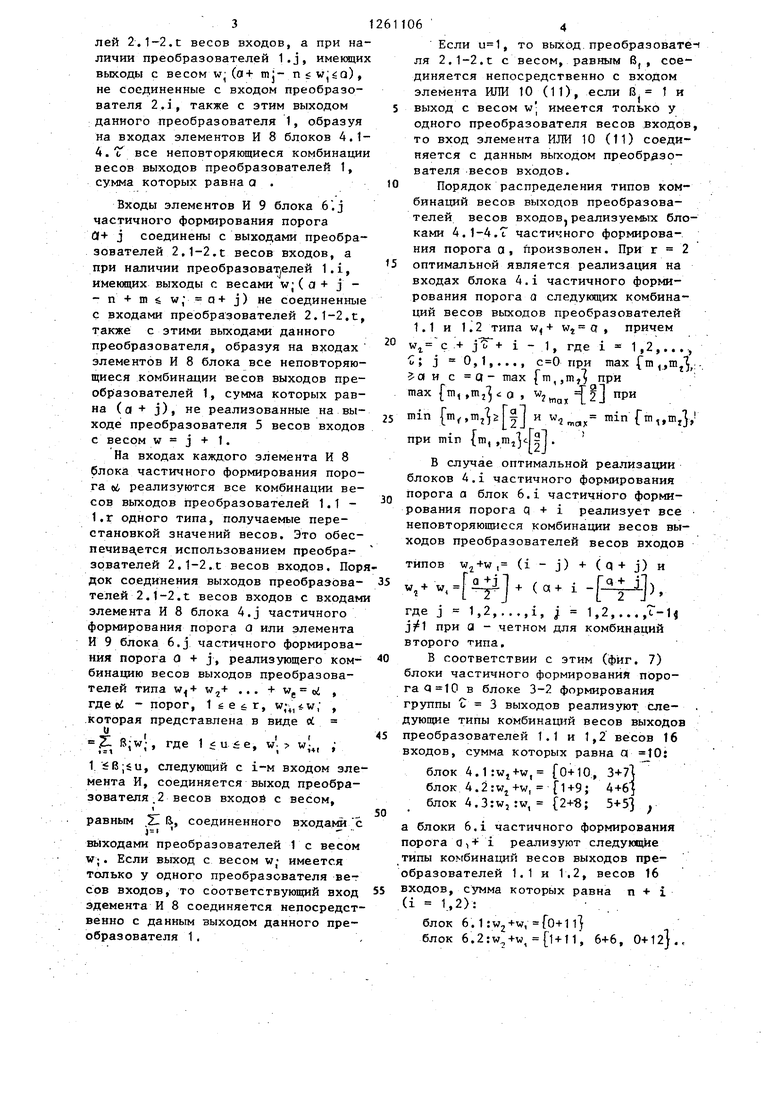

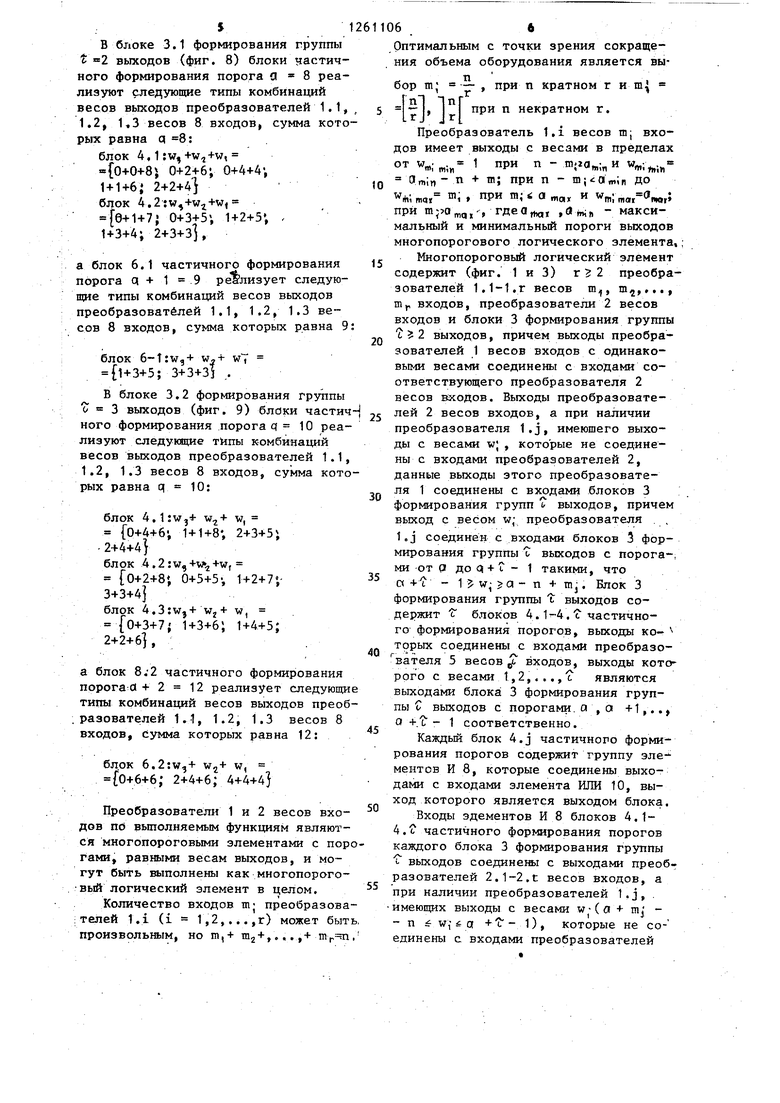

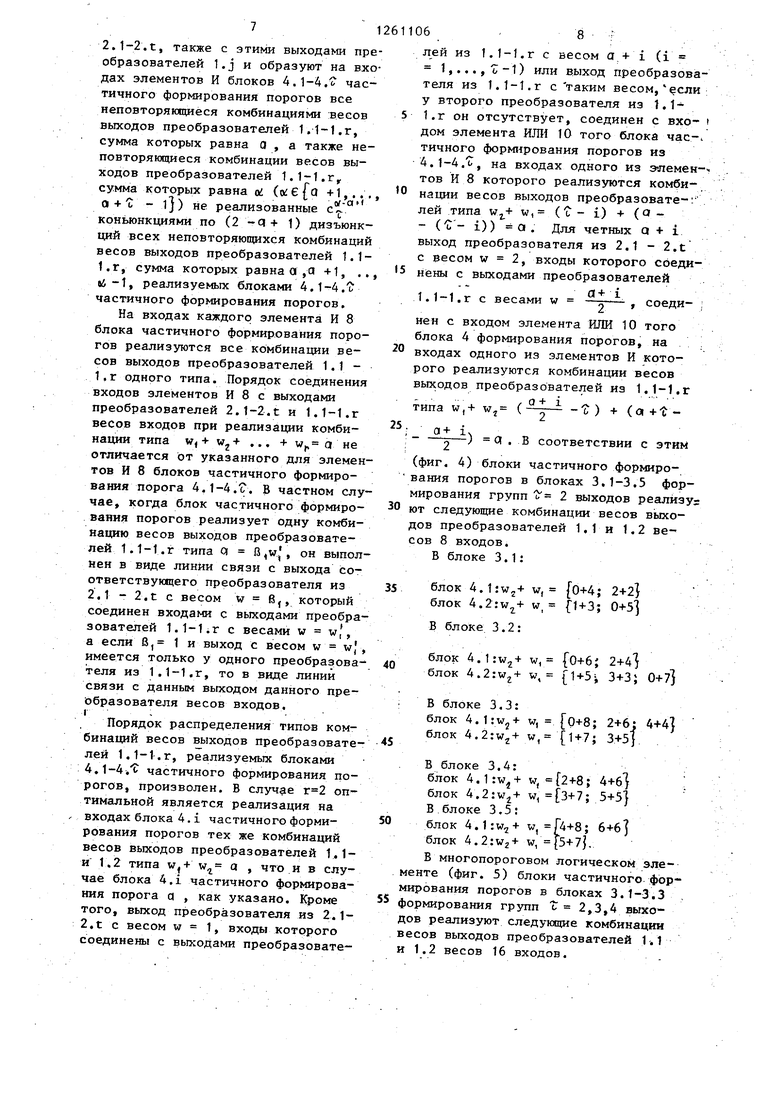

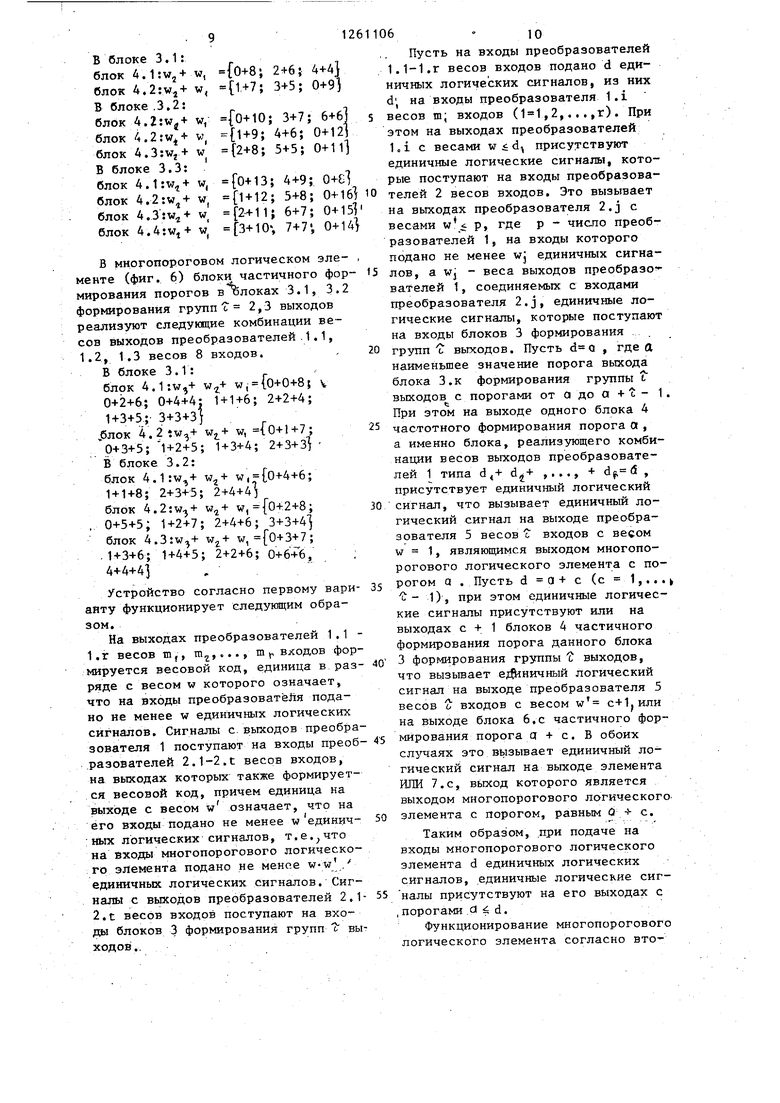

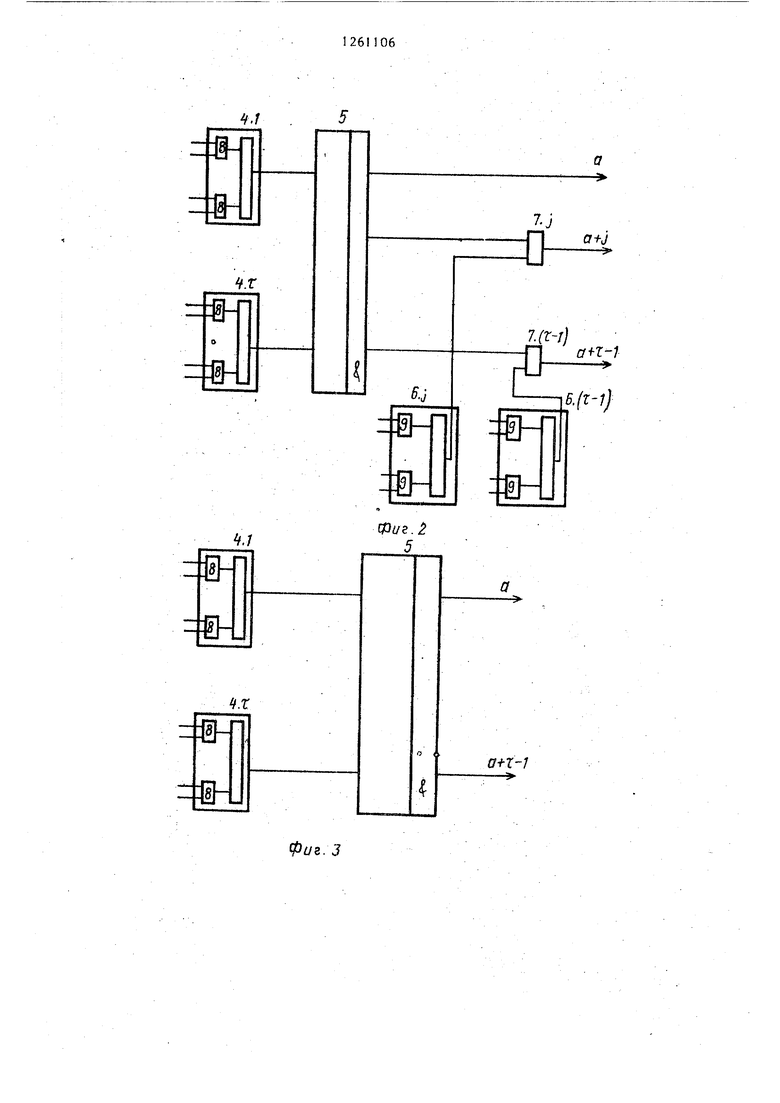

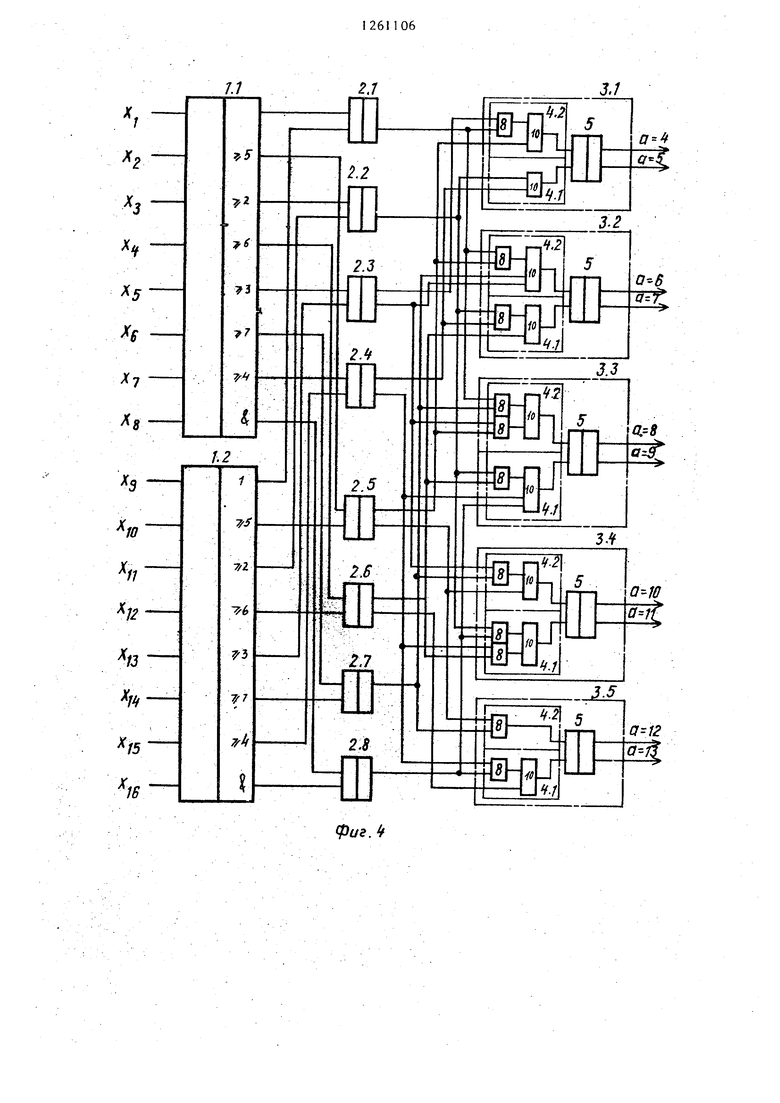

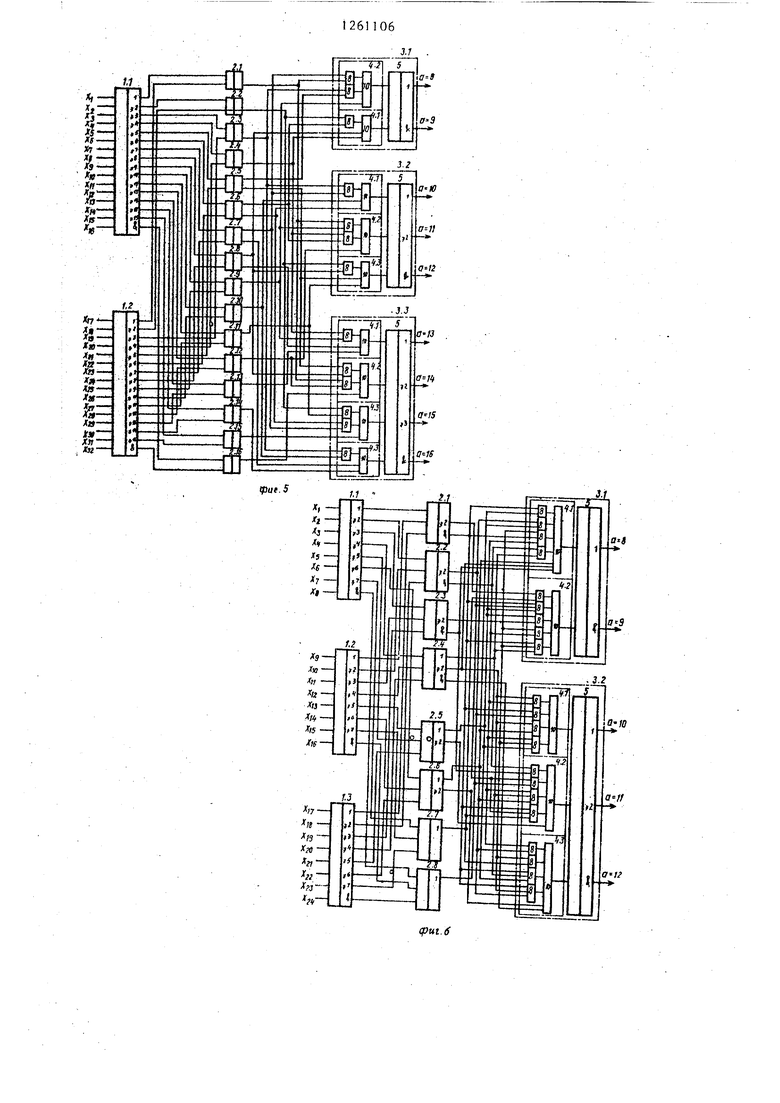

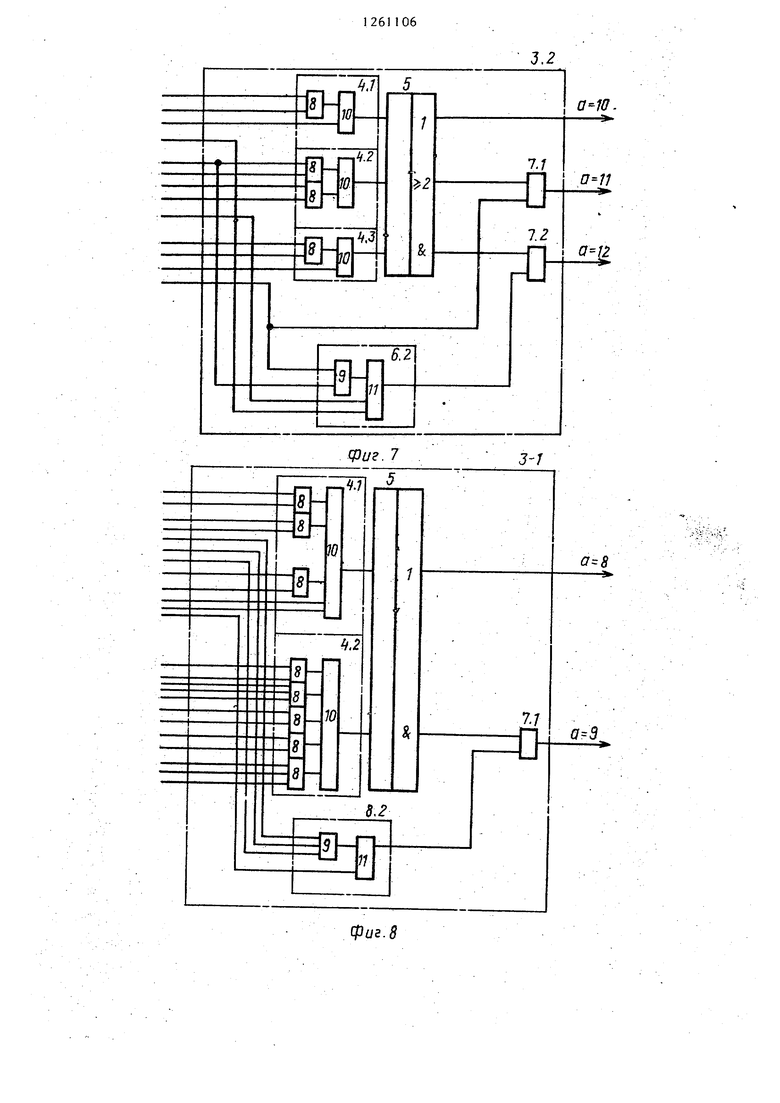

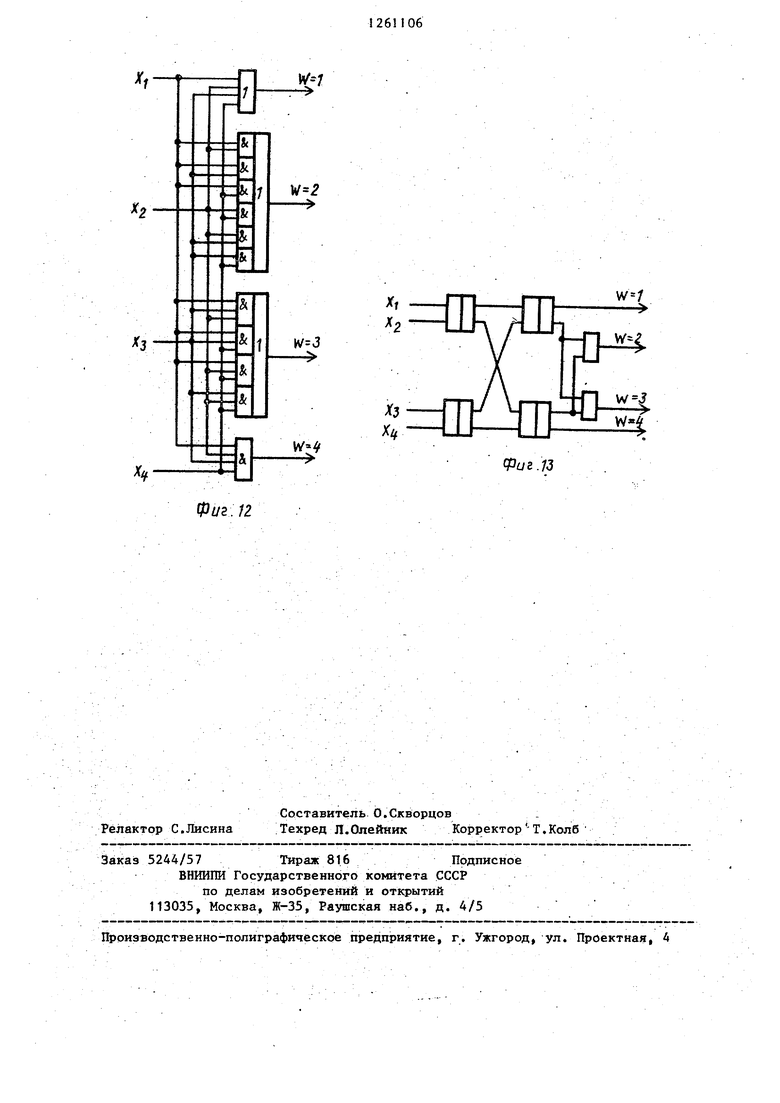

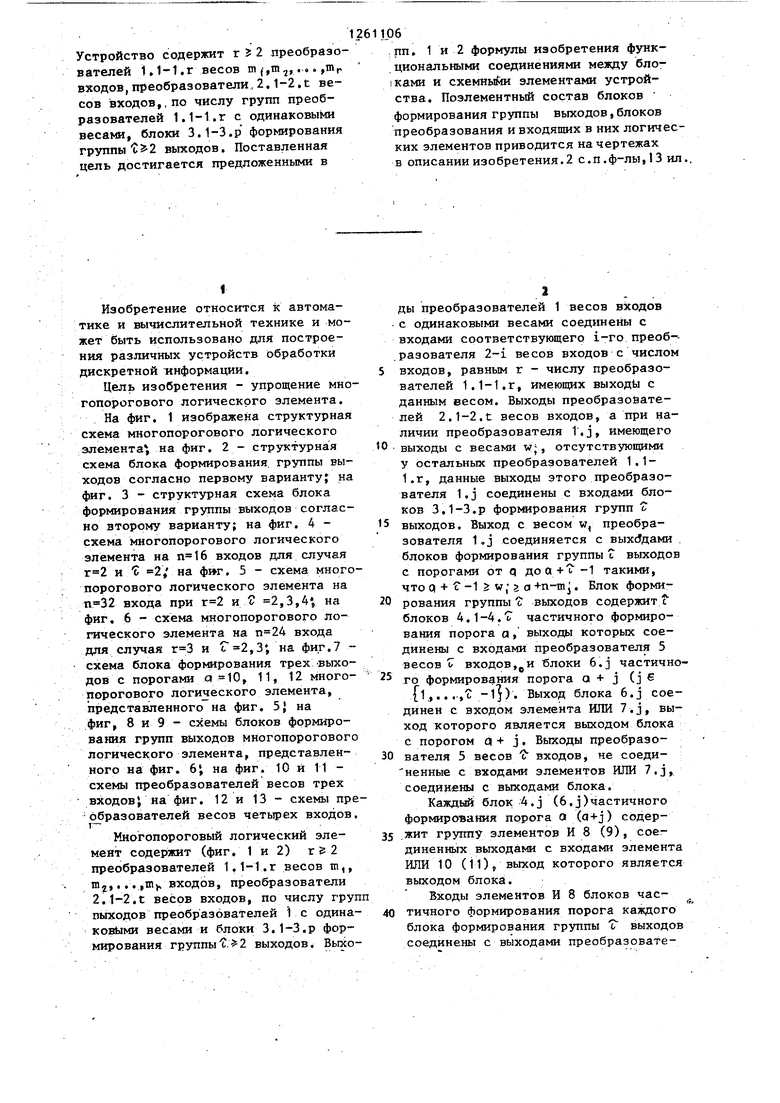

На фиг. 1 изображена структурная схема многопорогового логического элементарна фиг. 2 - структурная схема блока формирования, группы выходов согласно первому варианту; на фиг. 3 - структурная схема блока формирования группы выходов согласно второъгу варианту; на фиг. 4 - схема многопорогового логического элемента на входов для случая и /о 2, на . 5 - схема многопорогового логического элемента на «32 входа при и/ 2,3,4, на фиг. 6 - схема многопорогового логического элемента на входа для случая и ,3 на фиг,7 - схема блока формирования трех выходов с порогами а 10, 11, 12 многопорогового логического элемента, представленного на фиг. 5} на фиг, 8 и 9 - схемы блоков формирования групп выходов многопорогового логического элемента, представленного на Фиг, 6, на фиг. 10 и 11 - схемы преобразователей весов трех входов; на фиг. 12 и 13 - схемы преобразователей весов четырех входов.

.

Многопороговый логический элемент содержит (фиг. 1 и 2) r&2 преобразователей 1,1-1.г весов т,, mj,. ..,П1у, входов, преобразователи 2,1-2,t весов входов, по числу груп пыходов преобразователей 1 с одинаковыми весами и блоки 3,1-3,р формирования группы t. 2 выходов, ВыХо1261L06

пп. 1 и 2 формулы изобретения функциональными соединениями между бло- 1ками и схемнь1ми элементами устройства. Поэлементный состав блоков формирования группы выходов, блоков преобразования и входящих в них логических элементов приводится на чертежах в описании изобретения.2 с.п.ф-лы,3 ил.

ды преобразователей 1 весов входов с одинаковыми весами соединены с входами соответствующего i-ro преоб-- .разователя весов входов с числом

входов, равным г - числу преобразователей 1,1-1,г, имеющих выходу с данным весом. Выходы преобразователей 2,1-2,t весов входов, а при наличии преобразователя l.j, имеющего выходы с весами wj, отсутствующими у остальных преобразователей 1,1- 1,г, данные выходы этого преобразователя 1,j соединены с входами блоков 3,1-3,р форьшрования групп о

выходов. Выход с весом w, преобразователя соединяется с выходами блоков формирования группы Т выходов с порогами от q доа+ ь -1 такими, что Q + t -1 S w; г а +n-mj. Блок формирования группы с выходов содержит блоков 4,1-4,Т частичного формирования порога а, выходы которых соединены с входами преобразователя 5 весов IJ входов,и блоки 6, j частичного формирования порога а + j (j €

l.,,, t,; -lj). Выход блока 6, j соединен с входом элемента ИЛИ 7,j, выход которого является выходом блока с порогом а + j, Выходы преобразователя 5 весов входов, не соеди- ненные с входами элементов ИЛИ 7.J, соединены с выходами блока.

Каждой блок 4.j (6,j)4acTH4Horo формирования порога а (a+j) содер.жит группу элементов И 8 (9), соединенных выходами с входами элемента ИЛИ 10 (11), выход которого является выходом блока,

В:Ходы элементов И 8 блоков частичного формирования порога каждого блока формирования группы Т выходов соединены с выходами преобразовате3

лей 2.1-2.t весов входов, а при наличии преобразователей 1.J, имеющи выходы с весом wj (а+ mj- ), не соединенные с входом преобразователя 2.i, также с этим выходом данного преобразователя 1, образуя на входах элементов И 8 блоков 4.1 4.Т все неповторяющиеся комбинаци весов выходов преобразователей 1, сумма которых равна а .

Входы элементов И 9 блока 6. j частичного формирования порога 0+ j соединены с выходами преобразователей 2,1-2.t весов входов, а при наличии преобразователей 1.1, имеющих выходы с весами w;(а + j - - п + m 6 w; а+ j) не соединенные с входами преобразователей 2.1-2.t, также с этими выходами данного преобразователя, образуя на входах элементов И 8 блока все неповторяющиеся комбинации весов выходов преобразователей 1, сумма которых равна (а + j), не реализованные на выходе преобразователя 5 весов входов с весом W j + 1.

На входах каждого элемента И 8 блока частичного формирования порога «i реализуются все комбинации весов выходов преобразователей 1.1 - 1.Г одного типа, получаемые перестановкой значений весов. Это обес- печивг ется использованием преобразователей 2.1-2.t весов входов. Пор док соединения выходов преобразователей 2.1-2. t весов входов с входам элемента И 8 блока 4.J частичного формирования порога о или элемента И 9 блока 6.J частичного формирования порога О + j, реализующего комбинацию весов выходов преобразователей типа w .. . + Wg cd , где - порог, 1 &e&r, w,-, w; , .которая представлена в виде оС

j|. B;w;, где 1 , w ; w|, ,

1., следующий с i-м входом элемента И, соединяется выход преобразователя, 2 весов входов с весом, 1

равным 51 В, соединенного входами с вь1ходами преобразователей 1 с весом W;. ЕСЛИ выход с весом W; имеется только у одного преобразователя нет сов входов, то соответствующий вход эдемента И 8 соединяется непосредственно с данным выходом данного преобразователя 1,

Если , то выход, преобразовате-1

ля 2.1-2.с с весом, равным

(

сое10

15

20

5

0

5

0

5

0

5

диняется непосредственно с входом элемента ИЛИ 10 (11), если В, 1 и выход с весом w имеется только у одного преобразователя весов .входов, то вход элемента ИЛИ 10 (11) соединяется с данным выходом преобрдзо- вателя весов входов.

Порядок распределения типов комбинаций весов выходов преобразователей весов входов, реализуемьтх блоками 4.1-4.Г частичного формирования порога а, произволен. При г 2 оптимальной является реализация на входах блока 4.i частичного формирования порога а следующих комбинаций весов выходов преобразователей 1.1 и 1.2 типа Wj а , причем w с .+ jT+ i - 1, где i 1,2,...., « j 0 U «i при max f ш ,, ci и с а- max fm,,m, при шах m,, , при

min {т, и w, min (,, при min (m, , Э |.

В случае оптимальной реализации блоков 4.i частичного формирования порога а блок 6.1 частичного формирования порога q + i реализует все неповторяющиеся комбинации весов выходов преобразователей весов входов

типов Wj+w , (1 - j) + (q+ j) и

w, -3- I + ( a

+ 1 q + J

),

где J - 1,2,...,, } 1,2c-l4

при a - четном для комбинаций второго типа,

В соответствии с этим (фиг. 7) блоки частичного формирования порога О 10 в блоке 3-2 формирования группы 0 3 выходов реализуют следующие типы комбинаций весов выходов преобразователей 1.1 и 1,2 весов 16 входов, сумма которых равна а tO:

блок 4.1:wj-bw, 0+10:, 3+7 блок 4.2:wj+w, 1+9; 4+6 блок 4.3:w5:w, 2+в; З+З ;

а блоки 6.1 частичного формирования порога о i 1 реализуют следующие типы комбинатами весов выходов преобразователей 1.1 и 1.2, весов 16 входов, сумма которых равна п + i (1 Ь2): , .

блок 6.1 :w2+w, Го+11

блок 6.2:w,+w, 1 + 11, 6+6, 0+12.,

В блоке 3.1 формирования группы t 2 выходов (фиг. 8) блоки настич- ного формирования порога реализуют следующие типы комбинаций весов выходов преобразователей 1.1, 1.2, 1,3 весов 8 входов, сумма которых равна q 8:

блок 4,1:w,+w,+w,

0+0+8j 0+2+6; 0+4+4;

1+1+6; 2+2+4

блок 4.2:w,+Wj+w,

{0+1+7} 0+3+5; 1+2+5; .

1+3+4; 2+3+3,

а блок 6.1 частичного формирования порога q + 1 .9 ре лизует следующие типы комбинаций весов выходов преобразователей 1.1, 1«2, 1.3 весов 8 входов, сумма которых равна 9:

блок 6-T:w3+ w,+ w7

{1+3+5; 3+3+3i ,.

В блоке 3.2 формирования группы 3 выходов (фиг. 9) блоки частич ного формирования порога q 10 реализуют следующие типы комбинаций весов выходов преобразователей 1.1, 1.2, 1.3 весов 8 входов, сумма которых равна q 10:

блок 4. W2+ W, fo+4+6; 1+1+8; 2+3+5; - 2+4+4}

блок 4.2:W, +щ +W, fo+2+8 , 0+5+5-, 1+2+7 ,- 3+3+4

блок 4.3:w,+ Wj+ w, f0+3+7{ 1+3+6; 1+4+5; 2+2+6 ,

a блок 8. 2 частичного формирования nopora-d +2 12 реализует следующи типы комбинаций весов выходов преобразователей 1.1, 1.2, 1.3 весов 8 входов, сумма которых равна 12:

блок 6.2:w,+ W2+ w, fo+6+6; 2+4+6; 4+4+4

Преобразователи 1 и 2 весов вхо- дов пб вьтолняемым функциям являются многопороговыми элементами с порогами, равными весам выходов, и могут быть выполнены как многопорого- вьй логический элемент в целом.

Количество входов т; преобразова:телей 1.1 (i 1,2,...,г) может быть,

произвольным, но т,+ mj+ ,...,+ ,

5

О

5

0

,

0

5

Q

5

Оптимальным с точки зрения сокращения объема оборудования является выбор т - , при п кратном г и ш 1 некратном г.

Преобразователь l.i весов тп| входов имеет выходы с весами в пределах 1 при

от W

п - и ч«;.

CImin- п РИ m;.:am;r до w,h;mq.° ™1 Ри И Wn,-,,a,; при ,, , ,emiii -максимальный и минимальный пороги выходов многопорогового логического элемента,;

Многопороговый логический элемент содержит (фиг. 1 и 3) преобразователей 1.1-1.г весов т, т,,.., ffif, входов, преобразователи 2 весов входов и блоки 3 формирования группы с 2 выходов, причем выходы преобразователей 1 весов входов с одинаковыми весами соединены с входами соответствующего преобразователя 2 весов входов. Выходы преобразователей 2 весов входов, а при наличии преобразователя 1.J, имеющего выходы с весами w| , которые не соединены с входами преобразователей 2, данные выходы этого преобразователя 1 соединены с входами блоков 3 формирования групп t выходов, причем выход с весом w; преобразователя . .

1,j соединен с входами блоков 3 формирования группы t выходов с порога-, ми -от (J до с| + С - 1 такими, что а + t - 1 J. w- г а - п + mj. Блок 3 формирования группы t выходов содержит (Г блоков 4.. t частичного формирования порогов, выходы ко- торых соединены с входами преобразо- вателя 5 весов входов, выходы которого с весами 1,2, ..., с являются выходами блока 3 формирования группы С выходов с порогами, а ,а +1,.., о +. 1 соответственно.

Каждый блок 4.J частичного форми рования порогов содержит группу эле- ментов И 8, которые соединены выходами с входаш элемента ИЛИ 10, выход которого является выходом блока.

Входы эдементов И 8 блоков 4.1- 4.С частичного формирования порогов каждого блока 3 формирования группы 1. выходов соединены с выходами преобразователей 2.1-2.t весов входов, а при наличии преобразователей 1.J, . имеющих выходы с весами w (а + mj - - п + t - 1), которые не соединены с входами преобразователей

2.1-2.t, также с этими выходами преобразователей 1.J и образуют на входах элементов И блоков 4.1-4. частичного формирования порогов все неповторяющиеся комбинациями весов выходов преобразователей 1.1-1.г, сумма которых равна О , а также неповторяющиеся комбинации весов выходов преобразователей 1.1-1.г, сумма которых равна oL (о: f Q +1,..,

. - - ft

а + г

- 1)

не реализованные с

v-aM

конъюнкциями по (2 - С1+ 1) дизъюнкций всех неповторяющихся комбинаций весов выходов преобразователей 1.1- 1.Г, сумма которых равна а,а +1, .. ei -1, реализуемых блоками 4.1-4. частичного формирования порогов.

На входах каждого элемента И 8 блока частичного формирования порогов реализуются все комбинации весов выходов преобразователей 1.1- 1.г одного типа. Порядок соединения входов элементов И 8 с выходами преобразователей 2.1-2.t и 1.1-1.г весов входов при реализации комбинации типа Wj+ ... + w а не отличается от указанного для элементов И 8 блоков частичного формирования порога 4.1-4. с. В частном случае, когда блок частичного формирования порогов реализует одну комбинацию весов выходов преобразователей 1.1-1. г типа сг В ,w , он выполнен в виде линии связи с выхода соответствующего преобразователя из 2.1 - 2.t с весом w В,, который

соединен входами с выходами преобра I

зователей 1.1-1;г с весами w v а если 8, 1 и выход с весом w wj имеется только у одного преобразователя из 1.1-1.г, то в виде линии связи с данным выходом данного преобразователя весов входов, г - .

Порядок распределения типов комбинаций весов выходов преобразователей 1.1-1.г, реализуемых блоками 4.1-4. t частичного формирования цо- рогов, произволен. В случае оптимальной является реализация на входах блока 4. i частичного формирования порогов тех же комбинаций весов выходов преобразователей 1.1- и 1.2 типа w,+ w а , что и в случае блока 4.1 частичного формирования порога а , как указано. Кроме того, выход преобразователя из 2.1- 2.t с весом w 1, входы которого соединены с вькодами преобразовате

10

261106 8

лей из 1.1-1.г с весом а.+ i (i 1,... , о -1) или выход преобразователя из 1.1-1.г с таким весом, если у второго преобразователя из 1.1- 1.Г он отсутствует, соединен с вхо- i дом элемента HJHf 10 того блока час- тичного формирования порогов из 4. 1-4.о, на входах одного из эяемен-. тов И 8 которого реализуются комбинации весов выходов преобразовате-: лей типа w, (о - i) + (Q - - (С- )) а. Для четных а + i выход преобразователя из 2.1 - 2.t с весом w 2, входы которого соединены с выходами преобразователей

, . i

1.1 -1.г с весами w , соеди- ;

нен с входом элемента ИЛИ 10 того блока 4 формирования порогов, на . входах одного из элементов И которого реализуются комбинации весов выходов преобразователей из 1.1-1.г

15

20

типа W.+ w

7, (

0+ 1

-t) + (а

а+ 1

) 01 . В соответствии с этим

(фиг. 4) блоки частичного формиро- вания порогов в блоках 3.1-3.5 формирования групп и 2 выходов реалйзуг 30 JOT следующие комбинации весов ъых.о- дов преобразователей 1.1 и 1.2 весов 8 входов. В блоке 3.1:

блок 4.1:wj- - w, 0+4;2+2

блок 4. w, f1+3;0+5

В блоке 3.2:

блок 4.1:w2+ w, fO+6;2+4J

блок 4.2:w2+ w, {1+5 3+3; 0+

В блоке 3.3:

блок 4.1:wj+ w, 0+8;2+6; 4+4

блок 4.2:w2+ w, 1+7;3+5}

В блоке 3.4:„

блок 4. w, (2+8; 4+6у ;

блок 4.2:w2+ w, f3+7; 5+5}

В блоке 3.5:

блок 4.1:w,z+ w, /4+8; 6+6

блок 4.2:w2+ w, ,

В многопороговом логическом элементе (фиг. 5) блоки частичного формирования порогов в блоках 3.1-3.3 формирования групп t 2,3,4 выходов реализуют следующие комбинации весов выходов преобразователей 1.1 и 1.2 весов 16 входов.

в блоке 3.1:

блок 4.1 , {0+8; 2+6} 4+4 блок 4.2:wj+ W, {1+7; 3+5; 0+9 В блоке .3.2: блок 4.2:Wj;+ W,

W

блок 4. блок 4.3:wj+ w В блоке 3.3: блок 4.1 W,

(0+10; 3+7; 6+6 {1+9; 4+6; 0+12 {2+8; 5+5; 0+1l

блок 4.

fo+13; 4+9; O+CJ

1261106 - 10

Пусть на входы преобразователей 1.1-1.г весов входов подано d единичных логических сигналов, из них d; на входы преобразователя 1.1 весов т; входов (,2,...,г). При этом на выходах преобразователей 1 о i с весами w &d, присутствуют единичные логические сигналы, которые поступают на входы преобразова 1 + 12; 5+8; 0+1 б Ю телей 2 весов входов. Это вызывает {2-+11; 6+7; на выходах преобразователя 2.j с

весами w. р, где р - число преобразователей 1, на входы которого подано не менее wj единичных сигналов, а WJ - веса выходов преобразо- вателей 1, соединяемых с входами преобразователя 2.j, единичные логические сигналы, которые поступают на входы блоков 3 фop €иpoвaния . групп L выходов. Пусть , где а наименьшее значение порога выхода блока З.к формирования группы t

а до а + t блок 4. w L- ,

блок 4.4:wt+ w, {3+10 7+7 , O+UJ

20

25

30

В многопороговом логическом эле- . менте (фиг. 6) блоки частичного фор- 15 мирования порогов волоках 3.1, 3.2 формирования групп Т 2,3 выходов реализуют следующие комбинации весов выходов преобразователей .1.1, 1.2, 1.3 весов 8 входов.

В блоке 3.1:

блок 4. Wi o+0+8; v

0+2+6; 0+4+4: 1+1+6; 2+2+4;

1+3+5;- З+З+З лок 4.2{w.,+ Wj,+ w, (o+l+7;

P+3+5; 1+2+5; 1+3+4; 2+3+3

В блоке 3.2:

блок 4. w, {0+4+6;

1+1+8; 2+3+5; 2+4+4i

блок 4. W4+ w,{0+2+8; . 0+5+5; 1+2+7; 2+4+6; 3+3+4

блок 4.3:w.+ w, 0+3+7; .1+3+6; 1+4+5; 2+2+6; о+б +6, ;

4+4+4 ,

Устройство согласно первому варианту функционирует следующим образом.

На выходах преобразователей 1.1 - 1.Г весов т,, тп,..., т входов формируется весовой код, единица в раз- ряде с весом w которого означает, что на входы преобразователя подано не менее w единичных логических сигналов. Сигналы с. выходов преобразователя 1 поступают на входы преоб- 45 .разователей 2.1-2.t весов входов, на выходах которых также формируется весовой код, причем единица на выходе с весом w означает, что на

35

ВЫХОДОВ с порогами от а до а + С - 1

t

При этом на выходе одного блока 4 частотного формирования порога О, а именно блока, реализующего комбинации весов выходов преобразователей 1 типа ,..., + , присутствует единичный логический сигнал, что вызывает единичный логический сигнал на выходе преобразователя 5 весов с входов с весом w 1, являющимся выходом многопорогового логического элемента с порогом а . Пусть d а+ с (с 1,... J - 1), при этом единичные логические сигналы присутствуют или на выходах с + 1 блоков 4 частичного формирования порога данного блока 3 формирования группы с выходов, что вызьшает единичный логический сигнал на выходе преобразователя 5 весов о входов с весом w на выходе блока 6.с частичного формирования порога С + с. В обоих случаях это вызывает единичный логический сигнал на выходе элемента ИЛИ 7.с, вькод которого является выходом многопорогового логического элемента с порогом, равным Q + с.

его входы подано не менее w единич- : ньпс логических сигналов, т, е. что на входы многопорогового логического элемента подано не менее w-w . единичных логических сигналов. Сигналы с выходов преобразователей 2.1- 2.t весов входов поступают на входа блоков 3 формирования групп выходов ..

а до а + t

ВЫХОДОВ с порогами от а до а + С - 1 .

t

При этом на выходе одного блока 4 частотного формирования порога О, а именно блока, реализующего комбинации весов выходов преобразователей 1 типа ,..., + , присутствует единичный логический сигнал, что вызывает единичный логический сигнал на выходе преобразователя 5 весов с входов с весом w 1, являющимся выходом многопорогового логического элемента с порогом а . Пусть d а+ с (с 1,... J - 1), при этом единичные логические сигналы присутствуют или на выходах с + 1 блоков 4 частичного формирования порога данного блока 3 формирования группы с выходов, что вызьшает единичный логический сигнал на выходе преобразователя 5 весов о входов с весом w на выходе блока 6.с частичного формирования порога С + с. В обоих случаях это вызывает единичный логический сигнал на выходе элемента ИЛИ 7.с, вькод которого является выходом многопорогового логического элемента с порогом, равным Q + с.

Таким образом, при подаче на входы многопорогового логического элемента d единичных логических сигналов, единичные логические сиг- налы присутствуют на его выходах с .порогами d d.

Функционирование многопорогового логического элемента согласно второму варианту происходит следующим образом.

Пусть на входы преобразователей 1.1-1,г весов входов подано d единичных(потенциалов) логических сигналов, из них d на входы преобразователя 1.1 весов шj входов (i 1,2,...,г). При этом на выходах преобразователя 1.1 с весами widi, присутст ву от единичные логи- чёские сигналь, которые поступают на входы преобразователей 2.1-2.t весов входов. Это вызывает на выходах преобразователя 2.j с весами р, где р - число преобразовате лей 1.1-1.г, на входы которых подано не менее wj единичных логически сигналов, а Wj - веса выходов преобразователей Г. 1-1.г, соединяемых с входами данного преобразователя 2.J, единичные логические сигналы, которые поступают на входы блоков 3.1-З.р формирования групп Г выходов. Пусть d о + с (с 0,1,..., С -1), гд - наименьшее значение порога выхода блока 3-к формирования группы о выходов с порогами от g до а 4 с - 1, При этом на выходах с 1 - го блока частичного формирования порогов из 4.1-4.2 присутствуют единичные логические сигналы, что вызьгоает на выходах преобразователя 5 весов Г входов с весами w с + 1, являющимися выходами многопорогового логического. элемента с порогами а ,..., а + с, единичные логические сигналы. Таким образом, при подаче на входы многопорогового логического элемента d единичных логических сигна- лов, единичные логические сигналы присутствуют на его выходах с порогами aid.

Формула изо.бретения

1. Многопороговый логический элемент, содержащий преобразователей весов т,, тп,.,., га входов, выходы которых, имеюпще одина- ковые веса, соединены с входами соответствующих преобразователей весов входов второго уровня, их выходы, а также;. выходы преобразователей весов

s О 5 0 5 о о

5

m,,m,..., входов, которые не соединены с входами преобразователей второго уровня, соединены с входами соответствующих блоков формирования, содержащих группы элементов И, которые соединены выходами с входами элементов ИЛИ, отличающий- с я тем, что, с целью упрощения, в блоках форьшрования группы Т 2 выходов с порогами а , а + 1, ,.,, о + - 1, группы элементов И, которые соединены выходами с входами элементов ИЛИ, образуют блоки частичного формирования порога а , а + 1,.,,,а+Т- 1, выходы Т блоков частичного формирования порога а соединены с входами преобразователя весов входов, каждый блок час- - тичного формирования порога (J + i (i ,2,..., t-1), соединен вькод ом с входом своего элемента ИЛИ, другой вход которого соединен с выходом преобразователя весов о входов с ве-- сом i + 1, выходы данных элементов ИЛИ, а также выходы преобразователя весов С входов, которые не соединены с входами элементов ИЛИ, соединены с выходами блока формирования грзшпы ( выходов.

2, Многопороговый логический элемент, содержащий г 5 2 преобразова- , теля весов т,, ш,,,., т входов, . выходы которых, имеющие одинаковыми веса, соединены с входами соответствующих преобразователей весо в входов второго уровня, выходы которых, а также остальные преобра- в зователей в.есов т, ш,.,., т. входов, соединены с входами соответствующих блоков формирования, содер- жащих Группы элементов И, выходы которых соединены с входами элементов ИЛИ, отличающийся тем, что, с целью упрощения в блоках формирования группы t выходов с порогами а , а + 1,. . ., d + 1, группы элементов И, выходы которых соединены с входами элементов ИЛИ, образуют блоки частичного формирования порогов, выходы которых соединены с .входами преобразователя ве- сов t входов, выходы которого соединены с входами блока формирования группы выходов.

фиг. 3

1.1

/5

V5

фигЛ

а-

О Э

а-ю

а-Iff.

2

7.7

О

ПЧ1

.9

&

7.2

Л

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом @ | 1981 |

|

SU1027729A1 |

| Преобразователь двоичного кода в код по модулю К | 1989 |

|

SU1732472A1 |

| Пороговый элемент | 1981 |

|

SU1046932A1 |

| Устройство для умножения по модулю К | 1989 |

|

SU1691834A1 |

| Многопороговый логический элемент | 1987 |

|

SU1427563A1 |

| Многопороговый логический элемент | 1990 |

|

SU1803973A1 |

| Пороговый логический элемент | 1981 |

|

SU991612A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Устройство для цифровой фильтрации | 1986 |

|

SU1377872A1 |

| Многопороговый логический элемент | 1990 |

|

SU1728966A2 |

Изобретение относится к области автоматики и вычислительной техники. Может быть использовано для построения различных устройств обработки дискретной информации. Целью изобретения является упрощение мно- гопорогового логического элемента. 3.1 л./ (Л сг , Cb Од

Фи. 7

фиг. 8

Ю

Ю

а--10

2

ю

а-12

(риг.Э

J

Ш

fpuz.W

фиг. 11

Хз

Фиг. 12

Рёлактор С.Лисина

Составитель О.Скворцов Дехред Л.Олейник Корректор -Т. Колб

Заказ 5244/57 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 13

| Патент США № 4027125, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Устройство преобразования весов входов | 1981 |

|

SU1058064A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| fj | |||

Авторы

Даты

1986-09-30—Публикация

1983-07-08—Подача