1261110

цели в устройство введены триггеры 14, 15 и 16. Выходная шина 17 уст- 8 и 9, и ЛЭ 10. Фазовый детектор 3 ройства подключена к первому входу фа- содкржит триггеры 10 и 11, ЛЭ 13, зового детектора 3.1 з.п.ф-лы.1 ил.

f

Изобретение относится к импульсной технике и может быть использовано для построения синтезаторов частот средств связи, а также для генераторного оборудования многоканальных систем передачи.

Цель изобретения - повышение надежности в работе устройства путем устранения ложных выходных импульсов, возникающих при срыве синхро- низации.

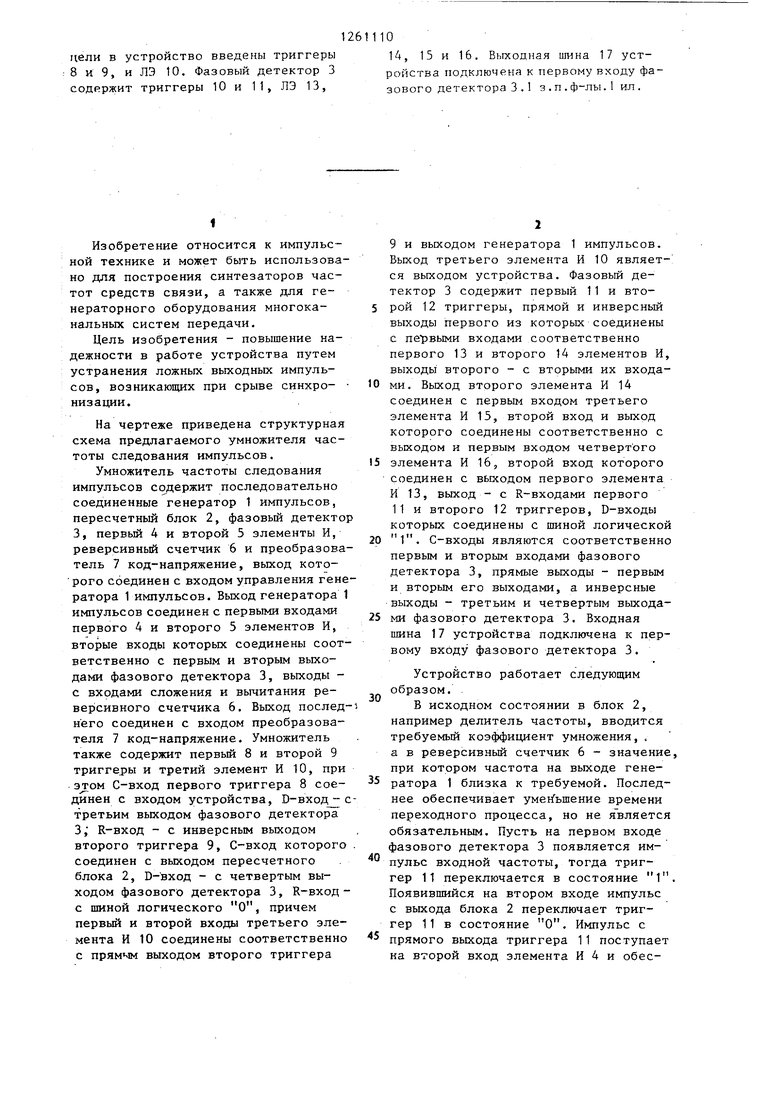

На чертеже приведена структурная схема предлагаемого умножителя частоты следования импульсов.

Умножитель частоты следования импульсов содержит последовательно соединенные генератор 1 импульсов, пересчетный блок 2, фазовый детекто 3, первьй 4 и второй 5 элементы И, реверсивньй счетчик 6 и преобразователь 7 код-напряжение, выход которого соединен с входом управления генератора 1 импульсов. Выход генератора 1 импульсов соединен с первыми входами первого 4 и второго 5 элементов И, вторые входы которых соединены соответственно с первым и вторым выходами фазового детектора 3, выходы - с входами сложения и вычитания реверсивного счетчика 6. Выход послед него соединен с входом преобразователя 7 код-напряжение. Умножитель также содержит первьй 8 и второй 9 триггеры и третий элемент И 10, при 3jroM С-вход первого триггера 8 соединен с входом устройства, В-вход ;-с третьим выходом фазового детектора 3; R-вход - с инверсным выходом второго триггера 9, С-вход которого соединен с выходом пересчетного блока 2, D-вход - с четвертым выходом фазового детектора 3, R-вход - с шиной логического О, причем первый и второй входы третьего элемента И 10 соединены соответственно с прямым выходом второго триггера

9 и выходом генератора 1 импульсов. Выход третьего элемента И 10 являет- ся выходом устройства. Фазовый детектор 3 содержит первый 11 и второй 12 триггеры, прямой и инверсный выходы первого из которых соединены с пе рвыми входами соответственно первого 13 и второго 14 элементов И, выходы второго - с вторыми их входами. Выход второго элемента И 14 соединен с первым входом третьего элемента И 15, второй вход и выход которого соединены соответственно с выходом и первым входом четвертого

элемента И 16, второй вход которого соединен с выходом первого элемента И 13, выход - с R-входами первого 11 и второго 12 триггеров, D-входы которых соединены с шиной логической

1. С-входы являются соответственно первым и вторым входами фазового детектора 3, прямые выходы - первым и вторым его выходами, а инверсные выходы - третьим и четвертым выходами фазового детектора 3. Входная

шина 17 устройства подключена к первому входу фазового детектора 3.

0

Устройство работает следующим образом.

В исходном состоянии в блок 2, например делитель частоты, вводится требуемый коэффициент умножения, . а в реверсивньй счетчик 6 - значение, при котором частота на выходе гене5 ратора 1 близка к требуемой. Последнее обеспечивает умен ьшение времени переходного продесса, но не яЪляется обязательным. Пусть на первом входе фазового детектора 3 появляется импульс входной частоты, тогда триггер 11 переключается в состояние 1. Появившийся на втором входе импульс с выхода блока 2 переключает триггер 11 в состояние О. Импульс с

5 прямого выхода триггера 11 поступает на второй вход элемента И 4 и обес31

печивает прохождение импульсов по первому входу с выхода генератора 1 на шину сложения реверсивного счетчика 6. Сигналы с выхода реверсивного счетчика 6 поступают на преоб- разователь 7, его выходное напряжение увеличивается, что приводит к возрастанию частоты следования импульсов, формируемых генератором 1. Следующий импульс с выхода блока 2 появляется раньше-, чем в предыдущем случае, что приводит к уменьшению разности фаз сравниваемых частот. Этот процесс продолжается до тех пор, пока разность фаз сравниваемых частот не становится равна нулю.

Если импульс: с выхода блока 2 появляется на втором входе фазового детектора 3 раньше, чем импульс на его первом входе, то второй триггер 12 переключается в состояние 1 и формирует импульс на прямом выходе, который поступает на второй вход элемента И 5 и обеспечивает прохождение импульсов с выхода генерато- ра -1 на шину вычитания реверсивного счетчика 6. Сигналы с выхода реверсивного счетчика 6 поступают на преобразователь 7, его выходное напряжение уменьшается, что приводит к уменьшению частоты следования импульсов генератора 1. Указанные циклы повторяются до тех пор, пока разност фаз сравниваемых частот не становится равной нулю.

Устройство на триггерах 8 и 9 осуществляет контроль за синхронной работой -системы фазовой автоподстройки частоты. При синхронной работе, т.е. при поочередном поступлении входных импульсов с входной шины jfCT ройства и импульсов с выхода перес четн го блока 2, оба триггера 8 и 9 находятся в состоянии 1. Таким образом, через элемент И 10 на выходе устройства по являются импульсы, формируемые генератором 1. При нарушении синхронизации на С-вход триггера В поступает подряд два импульса с входа устройства, тогда триггер 8 переключается под воздействием второго импульса в состояние О и импульсы на выходе элемента И 10 отсутствуют. При поступлении на С-вход триггера 9 подряд двух импульсов с выхода бло- ка 2 переключаются всостояние 0 триг- геры 9,а затем 8 и на выходе элемента И 1,0 импульсы также отсутствуют.

104

Таким образом, предлах аемое устройство по сравнению с прототипом Позволяет повысить качество связи путем исключения возможности появления колебаний, отличаемых от задай- ных, что повышает достоверность принимаемой информации по каналам связи Сигналы устройства контроля синхронной работы умножителя на счетчике 6, триггере 9, элементе 10 при появлении неисправности в последнем могут быть использованы для обеспечения автоматического переключения на резервный умножитель, практически без перерыва, что повышает надежность связи.

Ф о рмул а изобретения

1. Умножитель частоты следования импульсов, содержащий последовательно соединенные генератор импульсов, пересчетньй блок, фазовьй детектор, первый и второй элементы И, реверсивный счетчик и преобразователь код-напряжение, выход которого соединен с входом управления генератора импульсов, выход которого соедине с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с первым и вторым выходами фазового детектора, выходы - с входами сложения и вычитания реверсивного счетчика, выход которого соединен с входом преобразователя код-напряжение, а первый вход фазового детектора соединен с входной шиной устройства, отличающийся тем, что, с целью повышения надежности работы устройства, в него введены первый и второй триггеры и третий элемент И при этом С-вход первого триггера соединен с входом, устройства, D-вход с третьим выходом фазового детектора, R-вход - с инверсным выходом второго триггера, С-вход которого соединен с выходом пересчетного блока, D-вход - с четвертым выходом фазового детектора, R-вход - с шиной логического нуля, причем первый и второй входы третьего элемента И соединены соответственно с прямым выходом второго триггера и выходом генератора импульсов,а выход третьего элемента И является выходом устройства.

2. Устройство по п. 1, отличающееся тем, что фазовый

детектор содержит первый и второй триггеры, прямой и инверсный выходы первого из которых соединены с выми входами соответственно первого и второго элементов И, выходы второго - с вторыми их йходами, выход второго элемента И соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с выходом и первым входом четвертого элемента И, второй

Редактор С.Лисина Заказ 5245/58

Составитель С.Клевцов Техред И.Попович

Корректор

Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

вход которого соединен с выходом первого элемента И, выход - с R-BXO- дами первого и второго триггеров, D-входы которых соединены с шиной логической единицы, С-входь1 являются соответственно первым и вторым входами фазового детектора, прямые вы- ходы - первым и вторым его выходами, а инверсные выходы - третьим и четвертым выходами фазового детектора .

Корректор А.Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1983 |

|

SU1119165A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1411952A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1483630A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1429316A1 |

| Умножитель частоты следования импульсов | 1988 |

|

SU1529423A1 |

| Умножитель частоты импульсов | 1984 |

|

SU1238222A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

| Умножитель частоты следования импульсов | 1985 |

|

SU1270882A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1432754A1 |

| Умножитель частоты следования импульсов | 1989 |

|

SU1728964A2 |

Изобретение относится к импульс- ной технике и может быть использовано для построения синтезаторов частот средств связи, а также для генераторного оборудования многоканальных систем передачи. Цель изобретения - повышение надежности работы- достигается путем устранения ложных выходных импульсов, возникаюпщх при срыве синхронизации. Умножитель содержит генератор импульсов 1, пере- счетньм блок 2, фазовый детектор 3, логические элементы (ЛЭ) И 4,5 и 10, реверсивный счетчик 6, преобразователь код-напряжение 7, триггеры 8 и 9. Для достижения поставленной to Од

| Умножитель частоты следования импульсов | 1975 |

|

SU567202A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Умножитель частоты следования импульсов | 1983 |

|

SU1119165A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-30—Публикация

1984-07-09—Подача