24D1+288D2 при Е1 Е2 Ои

Di, D2#).

48Ei + 576E2 при EL Е2Ј0.

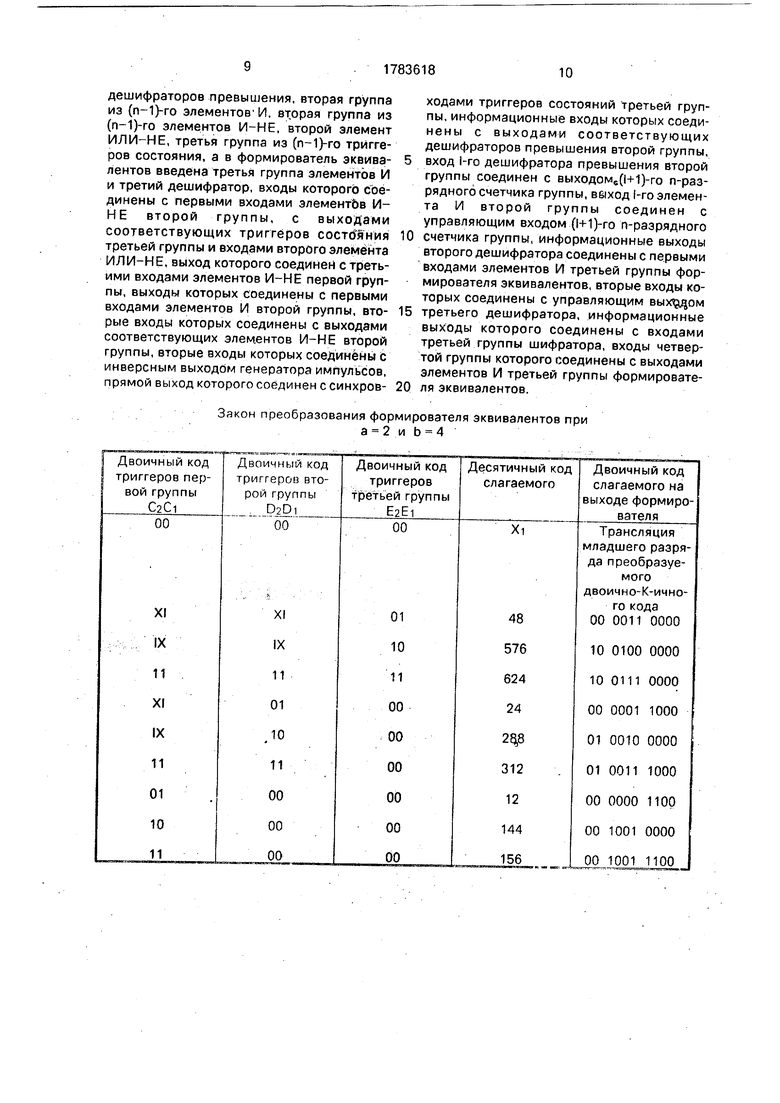

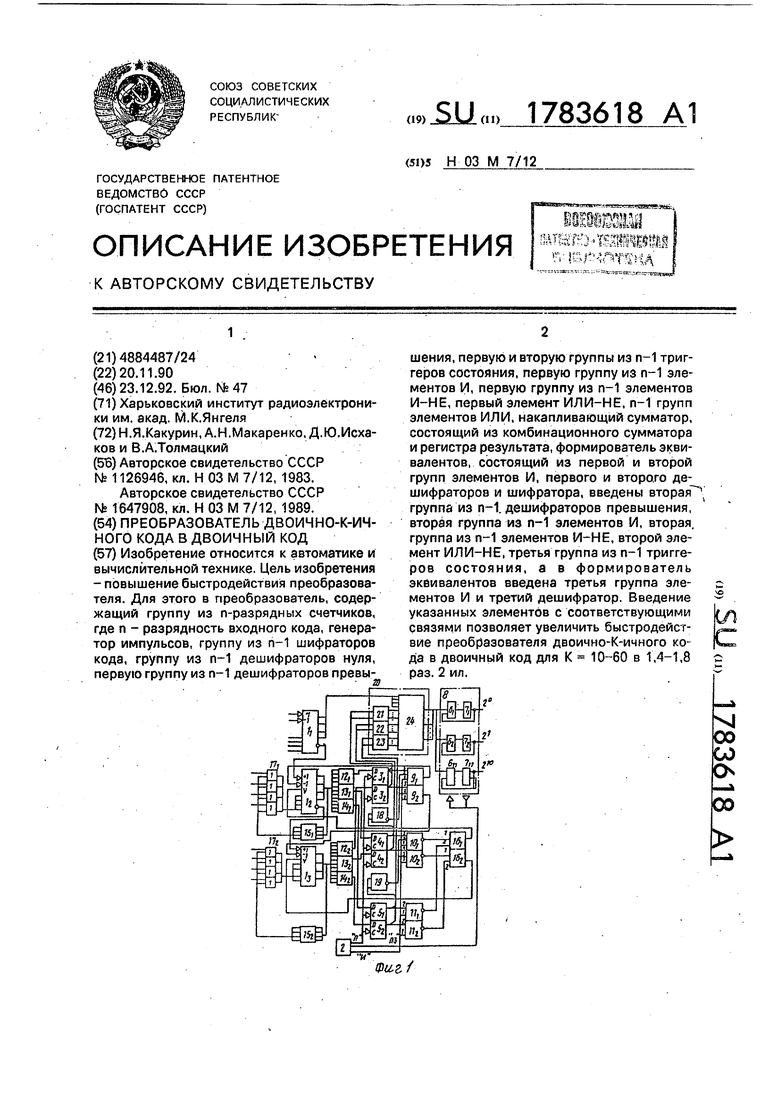

Преобразование двоичных кодов триггеров состояний первой 3. второй 4 и третьей групп соответствует таблице (а 2, Ь 4).

В исходном состоянии регистр 6 результата обнулен, на прямом выходе генератора 2 - низкий уровень, на инверсном выходе генератора 3, на выходах элементов И-НЕ 10 и 11 - высокий уровень. Прибавление и вычитание единицы в разрядных счетчиках 1, сложение в сумматоре б, а также запись информации в триггере состояний первой 3, второй 4 и третьей групп 5 производится перепадом . Запись выходного слова шифраторов 15 через элемент ИЛИ 17 в разрядные счетчики 1 всех разрядов, кроме группы младшего разряда, производится перепадом на управляющем входе V. Запись информации в регистр результата 7 также производится перепадом V-0.

С приходом переднего фронта первого положительного импульса с прямого выхода генератора 2 коды состояний триггеров первой 3, второй 4 и третьей 5 групп изменится: HaC2Ci 11,,E2Ei 11.

Коды триггеров состояний первой 3, второй 4 и третьей 5 групп поступают на входы формирователя эквивалентов 20 и преобразуются в двоичный код числа 624.

С приходом второго импульса коды состояний триггеров первой 3, второй 4 и третьей 5 групп установятся соответственно

C2Ci 11, D2Di 11, EaEi 10.

На выходах формирователя 20 появится двоичный код числа 576. Передний фронт задержанного положительного импульса разрешит сложение чисел 624 и 576, а задний фронт этого же импульса произведет перезапись результата суммирования в регистр 7 результата, установив на вторых суммирующих входах сумматора 6 двоичное значение числа 1200. Задний фронт второго

отрицательного импульса установит в счетчике 1 число.

Аа 0011 00101001.

С приходом переднего фронта третьего положительного импульса коды состояний триггеров первой 3, второй 4 и третьей 5 групп изменятся на CaCi 11, D2Di 11, E2Ei 00.

Следовательно, на выходах формирователя эквивалентов 20 будет двоичный код числа 312. Передний фронт третьего задержанного положительного импульса разрешит сложение чисел 1200 и 312, а задний

фронт этого же импульса установит на вторых суммирующих входах сумматора двоичное значение числа 1512. По заднему фронту третьего отрицательного импульса в счетчике 1 установится число (произойдет

вычитание двух из каждого старшего разряда).

Аз 0001 00001001.

С приходом четвертого импульса состояния триггеров состояний первой 3, второй 4 и третьей 5 групп, изменяется на CsCi ПО, DaDi 00, E2Ei 00, что -приведет к суммированию слагаемого 144 в двоичном коде с двоичным кодом числа 1512, а в старшем разряде 13 счетчика 1 - вычитанию единицы.

Таким образом, после четвертого импульса на вторых суммирующих входах сумматора 6 установится двоичное значение числа 1656, а в счетчике 1 число

А4 0000 0000 1001.

С приходом переднего фронта пятого прямого импульса устанавливается код состояний C2Ci 00. D2Di 00. EaEi - 00. В этом случае формирователь эквивалента 20 транслирует двоичный код младшего разряда 11 счетчика 1 на соответствующие четыре первых суммирующих входа сумматора 6. Передний фронт пятого задержанного положительного импульса разрешит сложение чисел 1656 и 9, а задний фронт этого же импульса установит двоичный код числа 1665 на выходах устройства. На этом процесс преобразования заканчивается.

Перед каждым следующим преобразованием необходимо обнулить регистр 7 результата и счетчик 1.

Наличие двоично-12-ричного реверсивного счетчика обеспечивает возможность работы в счетном режиме и введение поправок в двоичном параллельном коде.

Быстродействие предлагаемого устройства не зависит от разрядности преобразуемого кода и для 12-ричной системы счисления не превышает 5 тактов.

Формула изобретения

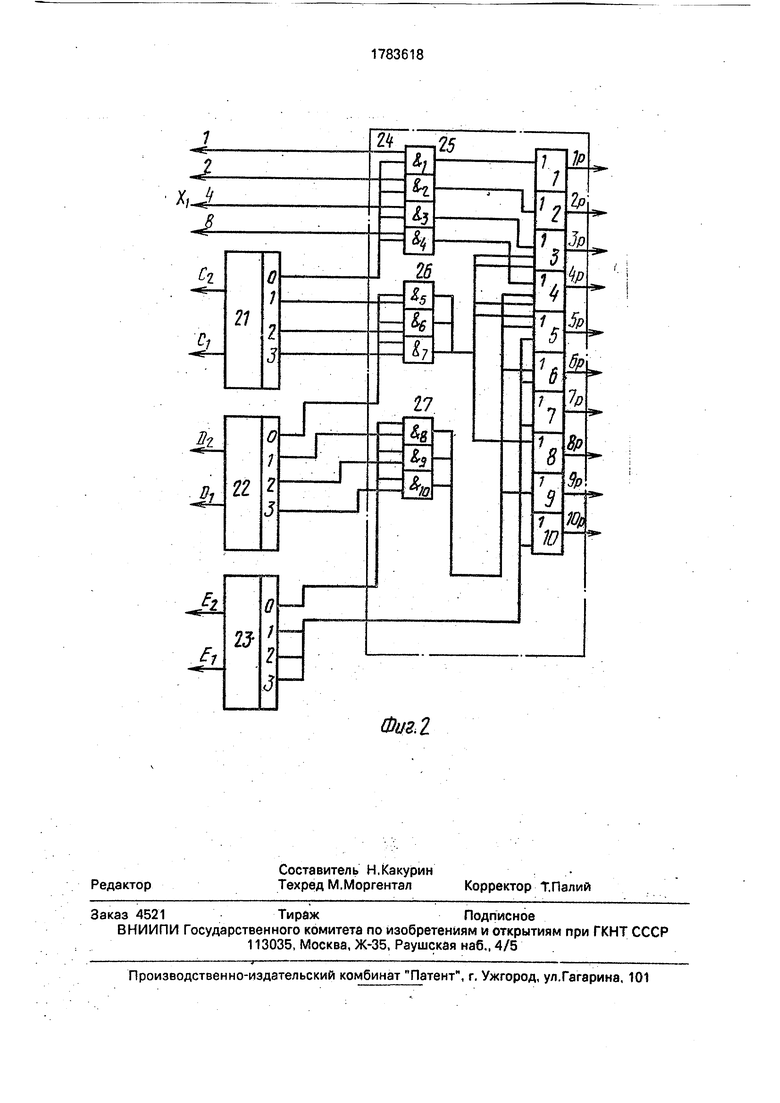

Преобразователь двоично-К-ичного кода в двоичный код, содержащий группу из п разрядных счетчиков, где п - разрядность входного кода, генератор импульсов, группу из п-1 шифраторов кода, группу из п-1 дешифраторов нуля, первую группу из п-1 дешифраторов превышения, первую и вторую группы из п-1 триггеров состояния, первую группу из п-1 элементов И, первую группу из п-1 элементов И-НЕ, первый элемент ИЛИ-НЕ, п-1 группу элементов ИЛИ, накапливающий сумматор и формирователь эквивалентов, содержащий первую и вторую группы элементов И, первый и второй дешифраторы и шифратор, выход которого является выходом формирователя эквивалентов и соединен с информационным входом накапливающего сумматора, выход которого является выходом преобразователя, синхровход накапливающего сумматора

соединен с прямым задержанным выходом генератора импульсов, прямой выход которого соединен с синхровходами триггеров состояний первой и второй групп, информационные входы которых соединены с выходами дешифраторов нуля группы и дешифраторов превышения первой группы соответственно, входы 1-го дешифратора нуля группы и 1-го дешифратора превышения первой группы (где I 1,2п-1) соединены

0 с входами 1-го шифратора кода группы и выходом (i-H)-ro n-разрядного счетчика группы, вход декремента которого соединен с выходом 1-го элемента И первой группы, первый вход которого соединен с первым

5 входом 1-го элемента И-НЕ первой группы и с инверсным выходом генератора импульсов, выход первого элемента ИЛИ-НЕ соединен с вторым входом 1-го элемента И первой группы, третий вход которого соеди0 нен с выходом f-ro триггера состояний первой группы и соответствующим входом первого дешифратора, 1-й вход вторбго дешифратора соединен с выходом 1-го триггера состояний второй группы, с вторым

5 входом 1-го элемента И-НЕ первой группы и 1-м входом первого элемента И-НЕ. выход переноса 1-го n-разрядного счетчика группы соединен с входом инкрементора (i+1)-ro п- разрядного счетчика группы, информацион0 ные входы которого соединены с выходами элементов ИЛИ 1-й группы, первые входы которых соединены с соответствующими выходами 1-го шифратора кода группы, вторые входы элементов ИЛИ 1-й группы явля5 ются параллельными информационными входами старших разрядов преобразователя, информационный параллельный вход первого разряда которого соединен с информационным входом первого п-разряд0 ного счетчика группы, входы инкрементора и декрементора которого соединены с соответствующими последовательными входами преобразователя, выходы первого n-разрядного счетчика группы соединены с

5 первыми входами элементов И первой группы формирователя эквивалентов, вторые входы которых соединены с управляющим выходом первого дешифратора, информационные выходы которого соединены с пер0 выми входами элементов И второй группы формирователя эквивалентов, вторые входы которых соединены с управляющим выходом второго дешифратора, выходы элементов И первой и второй групп форми5 рователя эквивалентов соединены с входами перЁОй и второй групп шифратора, о т- личающийся тем, что. с целью повышения быстродействия, в негодопол- нительно введена вторая группа из (п-1)-го

дешифраторов превышения, вторая группа из (п-1)-го элементов1 И, вторая группа из (п-1)-го элементов И-НЕ, второй элемент ИЛИ-НЕ, третья группа из (п-1)-го триггеров состояния, а в формирователь эквива- лентов введена третья группа элементов И и третий дешифратор, входы которого соединены с первыми входами элементбв И- НЕ второй группы, с выходами соответствующих триггеров состояния третьей группы и входами второго элемента ИЛИ-НЕ, выход которого соединен с третьими входами элементов И-НЕ первой группы, выходы которых соединены с первыми входами элементов И второй группы, вто- рые входы которых соединены с выходами соответствующих элементов И-НЕ второй группы, вторые входы которых соединены с инверсным выходом генератора импульсов, прямой выход которого соединен с синхров-

ходами триггеров состояний третьей группы, информационные входы которых соединены с выходами соответствующих дешифраторов превышения второй группы, вход 1-го дешифратора превышения второй группы соединен с выходомс(1+1)-го п-раз- рядного счетчика группы, выход 1-го элемента И второй группы соединен с управляющим входом (1+1)-го п-раэрядного счетчика группы, информационные выходы второго дешифратора соединены с первыми входами элементов И третьей группы формирователя эквивалентов, вторые входы которых соединены с управляющим выходом третьего дешифратора, информационные выходы которого соединены с входами третьей группы шифратора, входы четвертой группы которого соединены с выходами элементов И третьей группы формирователя эквивалентов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-К-ичного кода в двоичный код | 1983 |

|

SU1126946A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

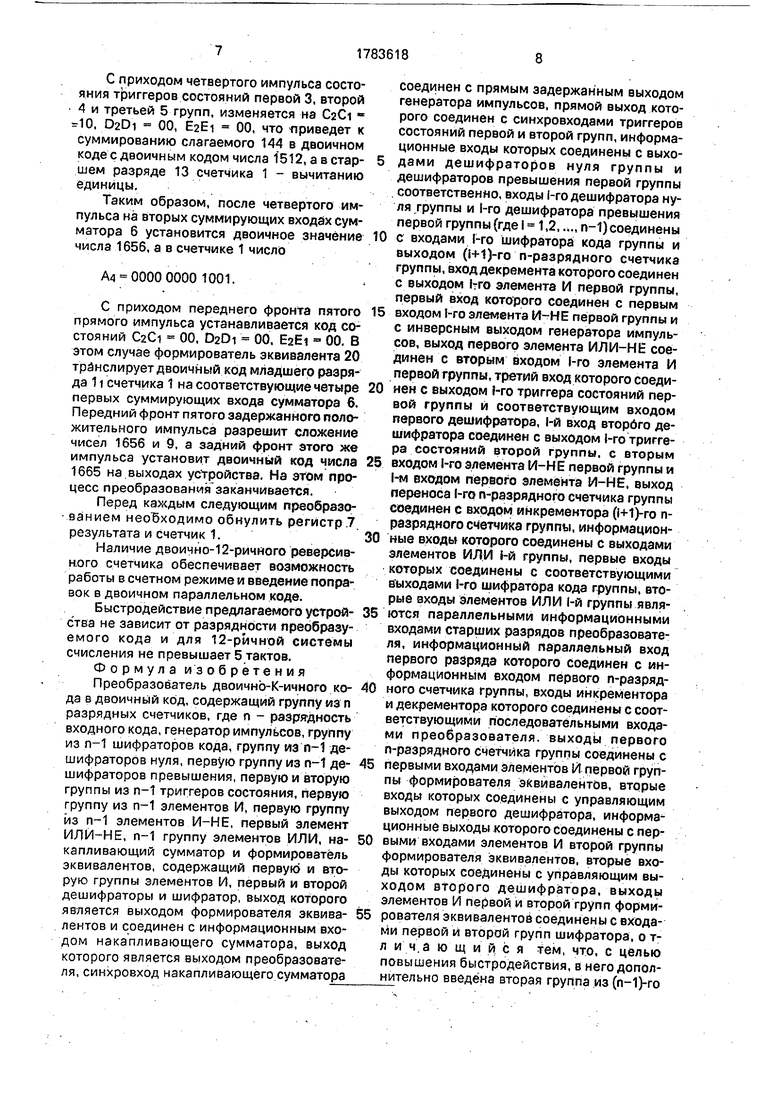

Изобретение относится к автоматике и вычислительной технике. Цель изобретения - повышение быстродействия преобразователя. Для этого в преобразователь, содержащий группу из n-разрядных счетчиков, где п - разрядность входного кода, генератор импульсов, группу из п-1 шифраторов кода, группу из п-1 дешифраторов нуля, первую группу из п-1 дешифраторов превышения, первую и вторую группы из п-1 триггеров состояния, первую группу из п-1 элементов И, первую группу из п-1 элементов И-НЕ, первый элемент ИЛИ-НЕ, п-1 групп элементов ИЛИ, накапливающий сумматор, состоящий из комбинационного сумматора и регистра результата, формирователь эквивалентов, состоящий из первой и второй групп элементов И, первого и второго дешифраторов и шифратора, введены вторая группа из п-1. дешифраторов превышения, вторая группа из п-1 элементов И, вторая, группа из п-1 элементов И-НЕ, второй элемент ИЛИ-НЕ, третья группа из п-1 триггеров состояния, а в формирователь экЁивалентов введена третья группа элементов И и третий дешифратор. Введение указанных элементов с соответствующими связями позволяет увеличить быстродействие преобразователя двоично-К-ичного кода в двоичный код для К 10-60 в 1,4-1,8 раз. 2 ил. С

Закон преобразования формирователя эквивалентов при

а 2 и Ь 4

Фиг. 2

Авторы

Даты

1992-12-23—Публикация

1990-11-20—Подача