ю

о

ts9

nU

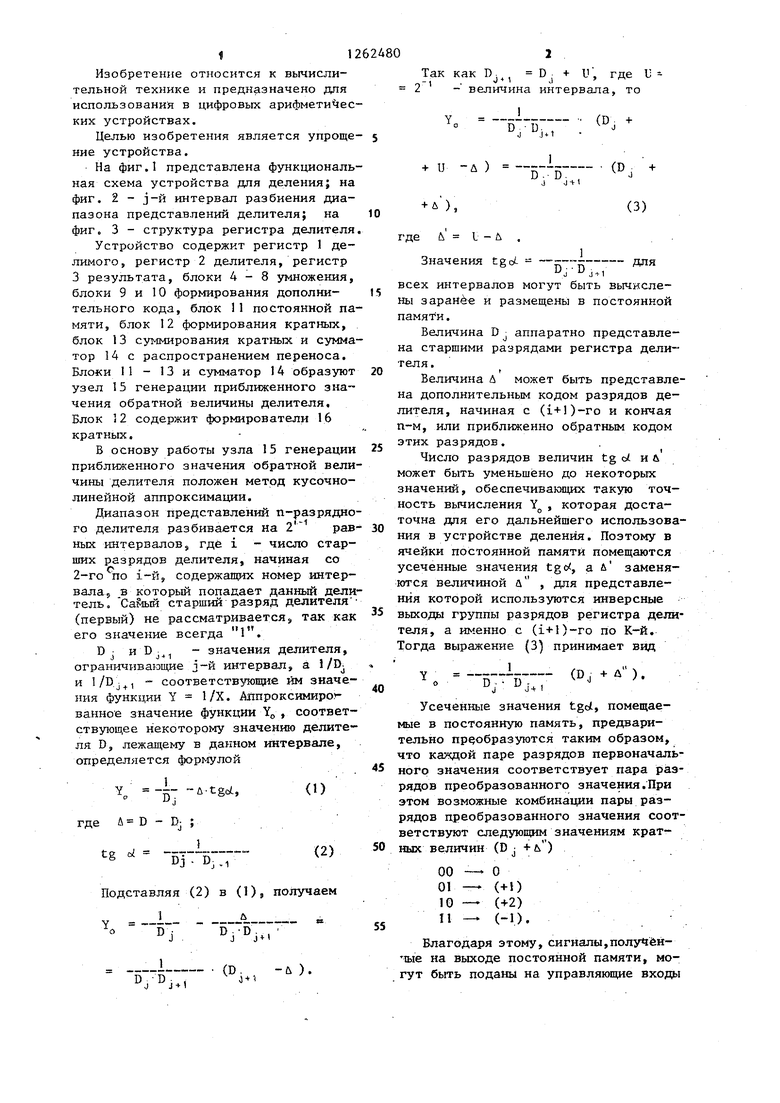

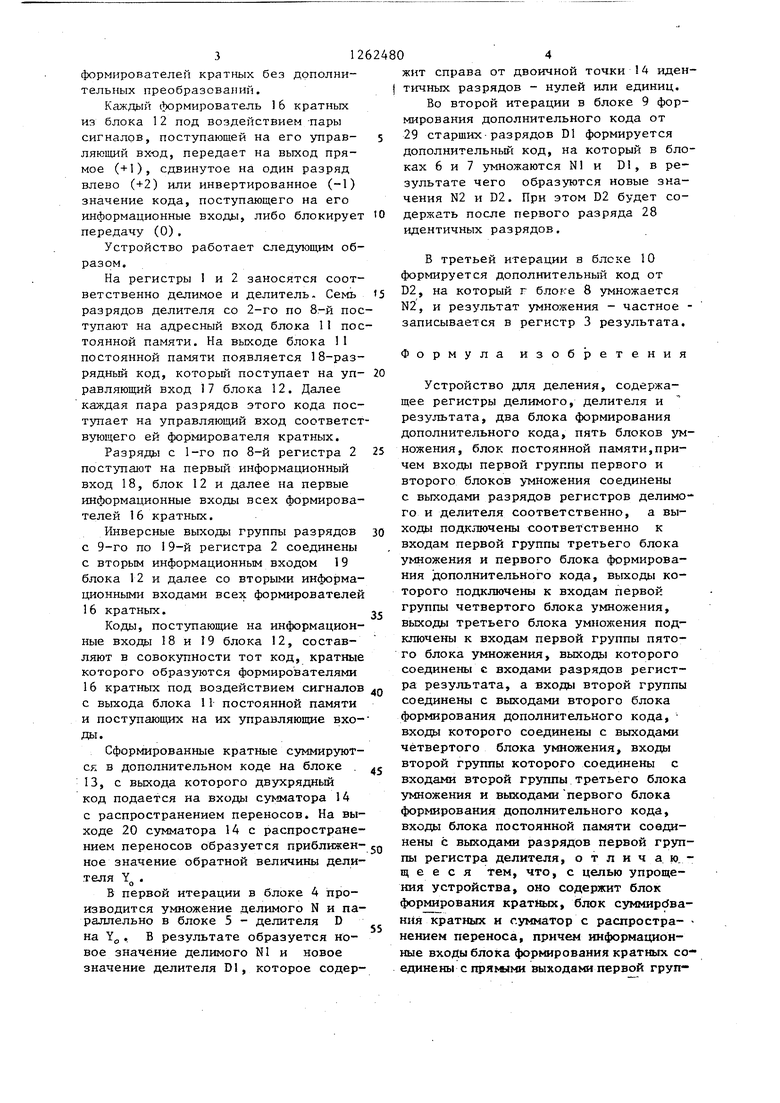

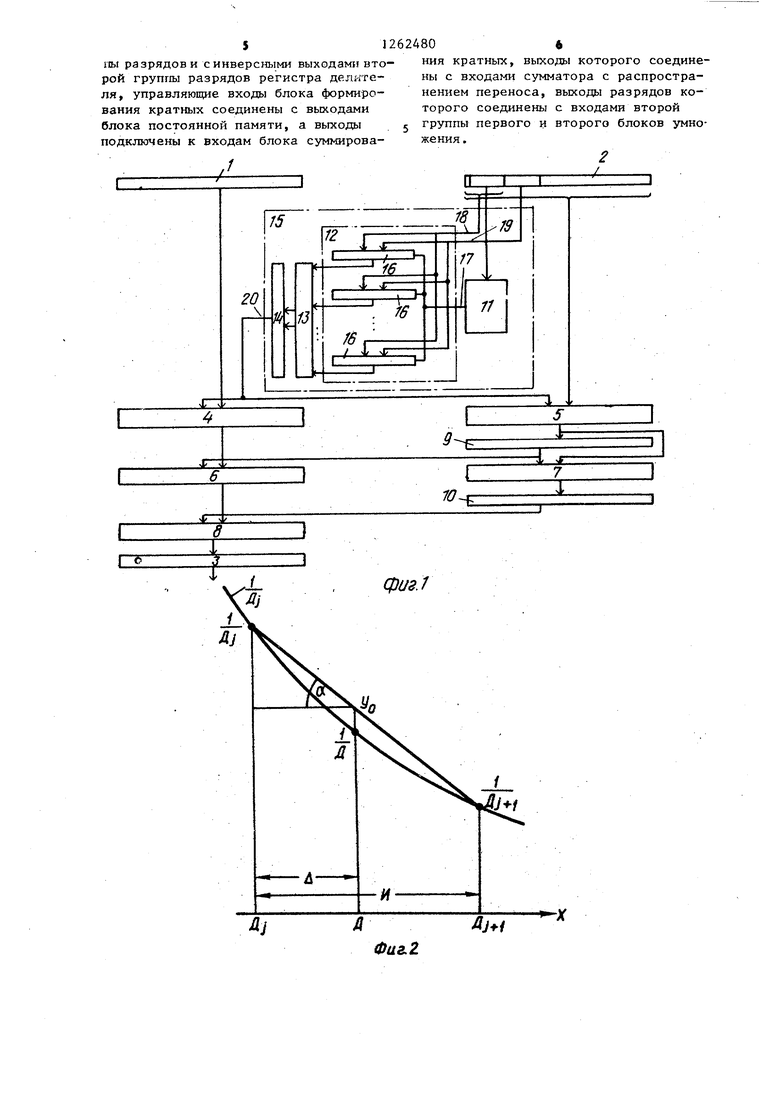

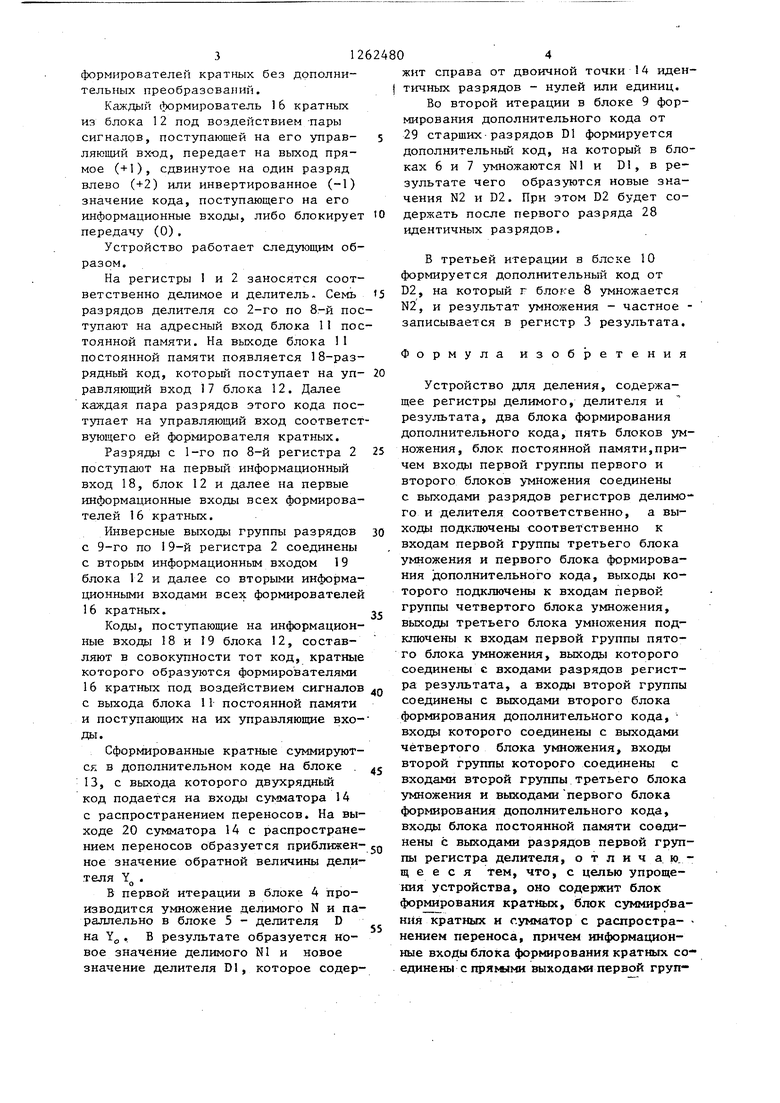

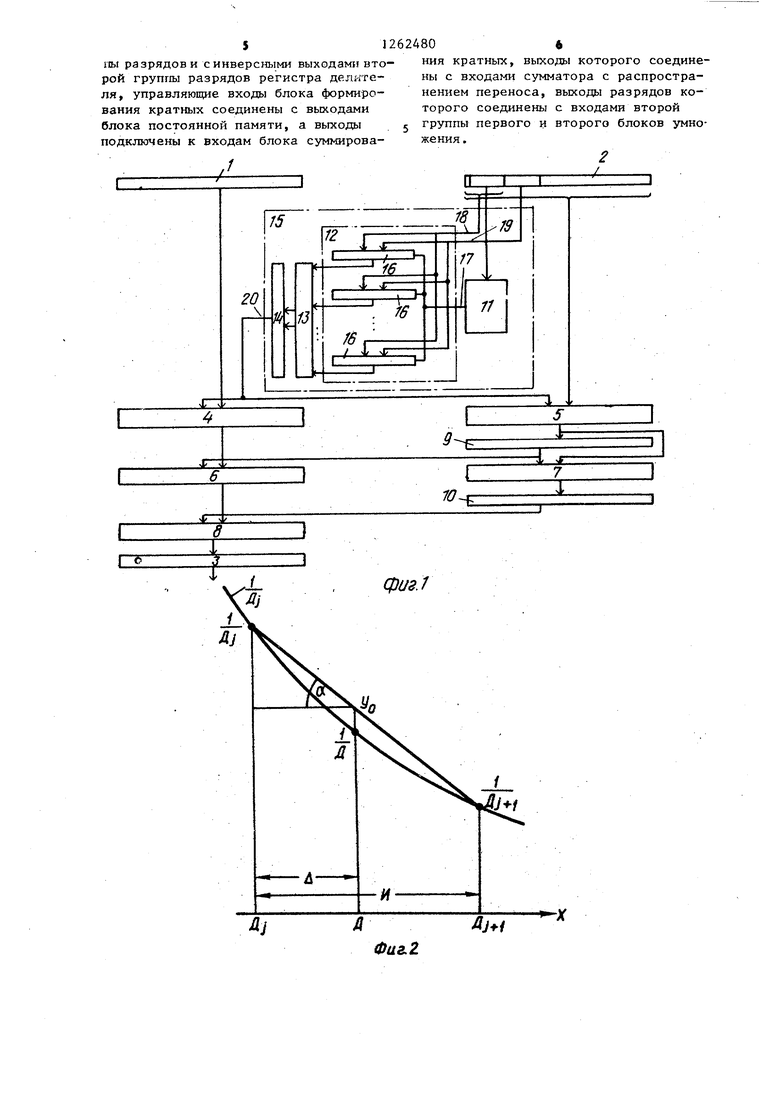

00 I1 Изобретение относится к вычислительной технике и предназначено для использования в цифровых арифмети 1ес ких устройствах. Целью изобретения является упроще ние устройства. На фиг.1 представлена функциональ ная схема устройства для деления; на фиг. 2 - j-й интервал разбиения диапазона представлений делителя; на фиг. 3 - структура регистра делителя Устройство содержит регистр 1 делимого, регистр 2 делителя, регистр 3 результата, блоки 4-8 умножения, блоки 9 и 10 фop rapoвaния дополнительного кода, блок 11 постоянной па мяти, блок 12 формирования кратных, блок 13 суммирования кратных и сумма тор 14 с распространением переноса. Блоки 11 - 13 и сумматор 14 образуют узел 15 генерации приближенного значения обратной величины делителя. Блок 12 содержит формирователи 16 кратных. В основу работы узла 15 генерации приближенного значения обратной вели чины делителя положен метод кусочнолинейной аппроксимации. Диапазон представлений п-разрядно го делителя разбивается на 2 рав ных интервалов, где i - число старших разрядов делителя, начиная ее 2-го по i-й, содержащих номер интервала, в который попадает данный дели тель. Сайый старший разряд делителя (первый) не рассматривается, так как его значение всегда 1. D и D , - значения делителя, J«1т ограничивающие j-и интервал, а i/Dj и 1/Dj, - соответствующие им значе ния функции Y 1/Х. Аппроксимиро ванное значение функции „, соответствующее некоторому значению делителя D, лежащему в данном интервале, определяется формулой Atgci, .-5U D - D; DJ- D,,1 Подставляя (2) в (1), получаем где & I - Л . Значения tgd. всех интервалов могут быть вычислены заранее и размещены в постоянной памяти. Величина D аппаратно представлена старшими разрядами регистра делителя. Величина Л может быть представлена дополнительным кодом разрядов делителя, начиная с (i+)-ro и кончая п-м, или приближенно обратным кодом этих разрядов. Число разрядов величин tg ot и & может быть уменьшено до некоторых значений, обеспечивающих такую точность вычисления Y , которая достаточна для его дальнейшего использования в устройстве деления. Поэтому в ячейки постоянной памяти помещаются усеченные значения tgo, аи заменяются величиной а , для представления которой используются инверсные выходы группы разрядов регистра делителя, а именно с (i+l)-ro по К-й. Тогда выражение (3) принимает вид .. 1 (D,, +Д ). Усеченные значения tgd., помещаемые в постоянную память, предварительно преобразуются таким образом, что каждой паре разрядов первоначального значения соответствует пара разрядов преобразованного значения.При этом возможные комбинации пары разрядов преобразованного значения соответствуют следуюшрнм значениям кратных величин (D : +&) О - , . 00-- О 01- (+1) 10- (+2) 11- (-1). Благодаря этому, сигналы,полуЧёнше на выходе постоянной памяти, могут быть поданы на управляющие входы

формирователей кратных без дополнительных преобразований.

Каждый (Ъормирователь 16 кратных из блока 12 под воздействием -пары сигналов, поступающей на его управляющий вх-од, передает на выход прямое (+1), сдвинутое на один разряд влево (+2) или инвертированное (-1) значение кода, поступающего на его информационные входы, либо блокирует передачу (0).

Устройство работает следующим образом.

На регистры 1 и 2 заносятся соответственно делимое и делитель. Семь разрядов делителя со 2-го по 8-й поступают на адресный вход блока 11 постоянной памяти. На выходе блока II постоянной памяти появляется 18-разрядный код, который поступает на управляющий вход 17 блока 12. Далее каждая пара разрядов этого кода поступает на управляющий вход соответствующего ей формирователя кратных.

Разряды с 1-го по 8-й регистра 2 поступают на первый информационный вход 18, блок 12 и далее на первые информационные входы всех формирователей 16 кратных.

Инверсные выходы группы разрядов с 9-го по 19-й регистра 2 соединены с вторым информационным входом 19 блока 12 и далее со вторыми информационными входами всех формирователей 16 кратных.

Коды, поступающие на информационные входы 18 и 19 блока 12, составляют в совокупности тот код, кратные которого образуются формирователями 16 кратных под воздействием сигналов с выхода блока 11 постоянной памяти и поступающих на их управляющие вхоДы.

Сформированные кратные суммируются в дополнительном коде на блоке . 13, с выхода которого двухрядный код подается на входы сумматора 14 с распространением переносов. На выходе 20 сумматора 14 с распространением переносов образуется приближенное значение обратной величины делителя Уд .

В первой итерации в блоке 4 производится умножение делимого N и параллельно в блоке 5 - делителя D

на YQ. В результате образуется новое значение делимого N1 и новое значение делителя D1, которое содержит справа от двоичной точки 14 идентичных разрядов - нулей или единиц.

Во второй итерации в блоке 9 формирования дополнительного кода от 29 старщих разрядов D1 формируется дополнительный код, на который в блоках 6 и 7 умножаются N1 и D1, в результате чего образуются новые значения N2 и D2. При этом D2 будет содержать после первого разряда 28 идентичных разрядов.

Б третьей итерации в блоке 10 формируется дополнительный код от D2, на который г блоке 8 умножается N2, и результат умножения - частное записывается в регистр 3 результата.

Формула изобретения

Устройство для деления, содержащее регистры делимого, делителя и результата, два блока формирования дополнительного кода, пять блоков умножения, блок постоянной памяти,причем входы первой группы первого и второго блоков умножения соединены с выходами разрядов регистров делимого и делителя соответственно, а выходы подключены соответственно к входам первой группы третьего блока умножения и первого блока формирования дополнительного кода, выходы которого подключены к входам первой группы четвертого блока умножения, выходы третьего блока умножения подключены к входам первой группы пятого блока умножения, выходы которого соединены с входами разрядов регистра результата, а входы второй группы соединены с выходами второго блока формирования дополнительного кода, входы которого соединены с выходами четвертого блока умножения, входы второй группы которого соединены с входами второй группы третьего блока умножения и выходамипервого блока формирования дополнительного кода, входы блока постоянной памяти соединены с выходами разрядов первой группы регистра делителя, отличаю.щ е е с я тем, что, с целью упрощения устройства, оно содержит блок формирования кратных, блок суммирбвания кратных и сумматор с распространением переноса, причш информационные входы блока формирования кратных соединены с прямыми выходами первой груп1 Ы разрядов И с инверсными выходами вто рой группы разрядов регистра делителя, управляющие входы блока формирования кратных соединены с выходами блока постоянной памяти, а выходы подключены к входам блока суммирова806ния кратных, выходы которого соединены с входами сумматора с распространением переноса, выходы разрядов которого соединены с входами второй второго блоков умногруппы первого и женил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1280613A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ | 1991 |

|

RU2018934C1 |

| Устройство для двоичного деления | 1986 |

|

SU1399727A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

Изобретение относится к вычислительной технике и предназначено для использования в цифровых арифметических устройствах. Целью изобретения является упрощение устройства. Устройство содеркит регистр делимого, регистр делителя, регистр результата, блоки формирования дoпoлнитeльнoio кода и узел генерации 11риближенного значения обратной величины делителя, содержащий блок постоянной памяти, блок формирования кратных, блок суммирования кратных и сумматор с распространением переноса. Результат вычислений формируете за три итерации. 3 ил.

Cf)U8t

-х

На пербые информационные бмды (pop ниробателей Кратных ц адресный бмд SflOKO памяти

На дторьге информационные 0X0ды формирсбателей кратных

Фиг.З

| Устройство для деления | 1975 |

|

SU602944A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Гаврилов Ю.В | |||

| и др | |||

| Арифметические устройства быстродействующих ЭЦВМ | |||

| - М.: Советское радио, 1970, с.221-224. | |||

Авторы

Даты

1986-10-07—Публикация

1985-01-02—Подача