1Э

ш

40

foun

fS

7

оо

N

ы

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1262480A1 |

| Устройство для деления двоичных чисел | 1981 |

|

SU1008733A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1280613A1 |

| Конвейерное устройство для деления итерационного типа | 1985 |

|

SU1262483A1 |

| Конвейерное устройство для деления интерационного типа | 1984 |

|

SU1179321A1 |

| Устройство для деления чисел с фиксированной запятой | 1986 |

|

SU1417009A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Делительное устройство | 1983 |

|

SU1176324A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

Изобретение относится к вычисли тельной технике и может быть использо вано в арифметических устройствах быстродействующих ЭВМ, Целью изобрете кия является повьшение быстродейст ВИЯ. Поставленная цель достигается тем, что устройство для двоичного деления, содержащее регистр 2 делителя, регистр 3 остатка, блок 4 коммутации кратных, сумматор 8 остатка, формирователь 9 усеченного остатка, блоки 10, 11 сравнения, дешифратор 12 выбора кратного, регистр 13 сиг налов выбора кратного, формирователь li частного и регистр 15 частного, содержит регистр 16 усеченного кратного, формирователь 17 усеченных KpHTiu-ix, формирователь 18 приближенного знака, блоки 19,20 суммирования пробных кратных и коммутатор 2 усе- кратных с соответствующими связями. 4 з.п. , 12 ил., 1 табл. О «

.1

ИзоРретеште отноа- тся к вычисли тельной техиике и предназначено для двоичного деления чисел без восстановления остатка.

10

25

Цель изобретолгля повышение быст родействия устройства ,

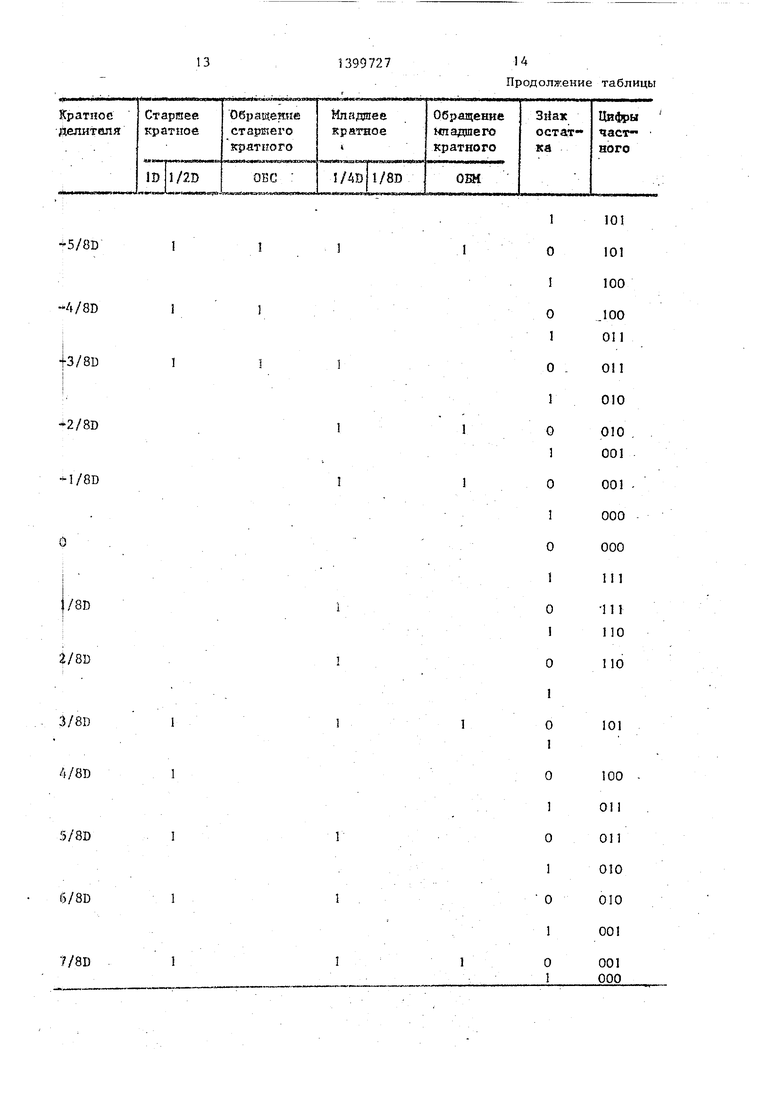

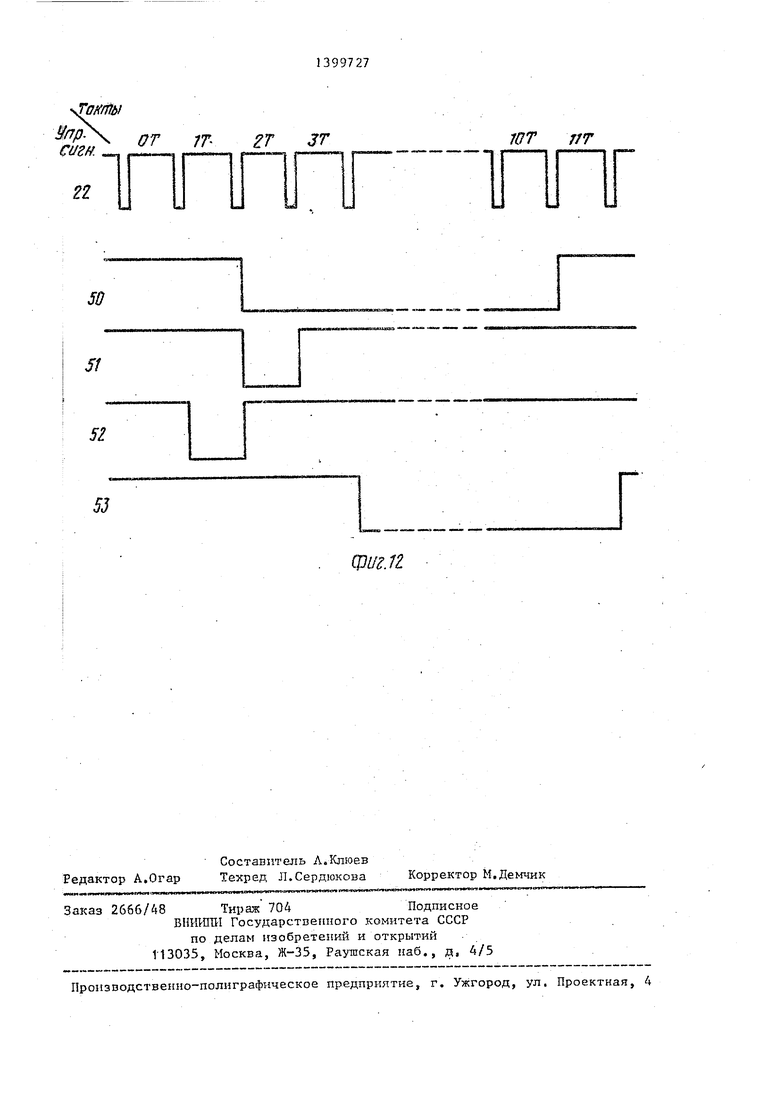

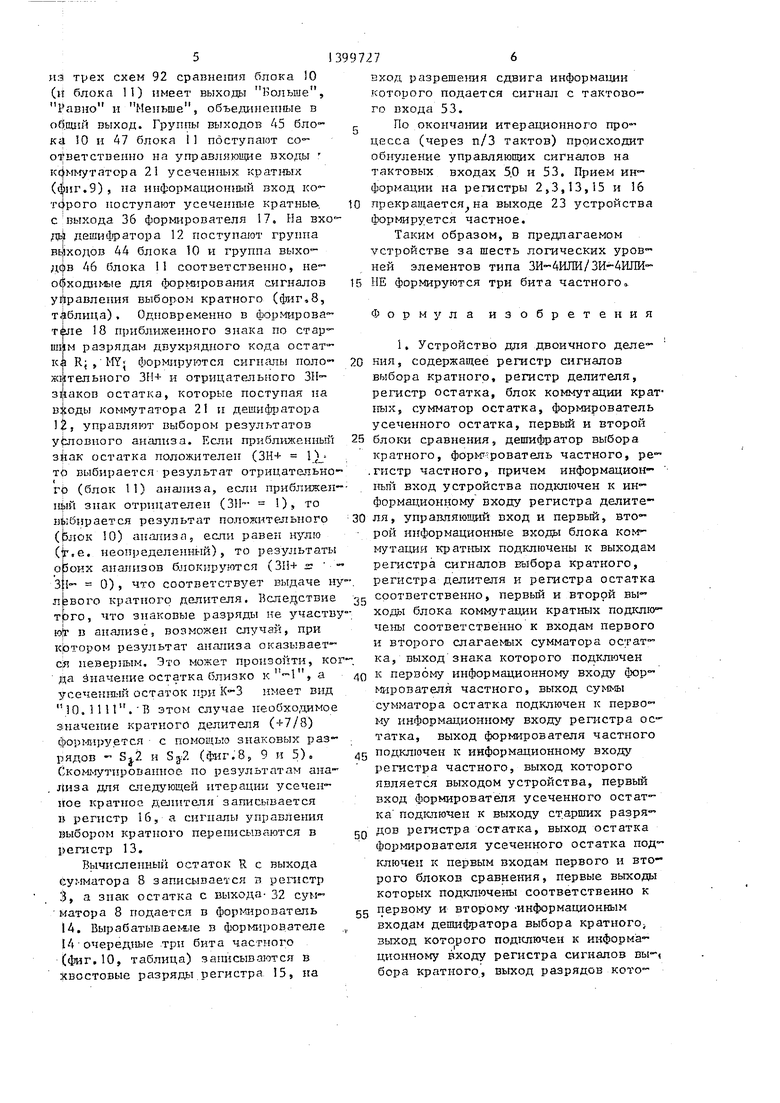

Па фиг,1 представлена схема уст ройстпа для двоичного деления; на фиг,2 схема формирователя усечен- ного остатка для случая К-3 (К - коичество формируемых разрядов частного) ; на (иг.З схемы нервого и второго блоков суммирования rrpo6iib x кратных дпя случая на с1л1Г.4 схема сумматора пробных кратных для случая К-З; на .З - схема формирователя приближенного знака для случая К-З; на 4iir.6 - схемы первого и вто-- 20 рого блоков сравнения для случал 1(3 па tiinr«7 схема сравнения для случая К-3; на фиг.8 - схема дешифратора аы бора кратного дпя случая на (}д1Г.9 - схема разряда коммутатора усеченных кратных дпя случая К-3; на фиг. 10 схема формирователя част ного длп случая на фиг.1 схема формирователя усеченных крат-- яых для случая К-З; на фиг 12 временные диаграммы тактовых входов дпя случй-я ,

Устройство дпя двоичного деления ((li«r,i) содержит информационный вход 1 устройства, регистр 2 делителя, регистр 3 остатка, блок /4 комму т а™ ни кратных, управляющей вход 5 6лО ка 4 комм /тадии кратных, нервьш информационный вход 6 блока А тадии кратных, .второй информациоп - ный вход 7 блока 4 комьтутации кратных, Сумматор 8 остатка, формирователь 9 усеченного остатка, первый 10 и рой 11 блоки сравнения, дешисЪ

10

30

3

ратор 12 выбора кратного, регистр 13 сигналов выбора кратного, ветель 14 частного, регистр 15 част ного, регистр 16 усеченного кратно го, формирователь 17 усеченных крат , формирователь 18 щэиближенного знака, первый 19 и второй 20 блоки суммироваш1Я пробных кратных, татор 21 усеченньге кратных, вход 22 синхронизации устройства, выход 23 устройства, выход 24 регистра 13 сигпапов выбора кратного, выход 25 разрядов регистра 13 сигналов выбора кратного, выход 26 регистра 2 де лител5, выходх 27 старших разрядов

регистра 2 делителя, выход 28 регистра 3 остатка, выход 29 старших разря - дов регистра 3 остатка, первый выход 30 блока 4 коммутации кратных, второй выход 31 блока 4 коммутации кратных, выход 32 знака сумматора 8 остатка, выход 33 суммы сумматора 8 остатка, выход 34 формирователя 14 частного, выход 35 регистра 16 усеченного крат ного, первый выход 36 формирователя усеченных кратршш, второй выход 37 формирователя 7 усеченных кратных, третий выход 38 форг«-1рователя 17 усеченных кратных, выход 39 форми

рователя 18 приближенного знака, вы

ход 40 блока 1Э суммирования пробных кратных, выход 41 блока 20 суммярова - ния пробных кратных, выход 42 остатка форг-шрователя 9 усеченного , выход 43 переноса формироват; ля 9 усеченного остатка, первый выход 44 блока 0 сравнения, второй выход 45 бло ка io сравнения, первый 46 и второй

47выходы блока П сравнения, выход

48коммутатор; . 21 усеченных кратных, выход 49 дешифратора12 выбора крат- ного, а также первый 50, второй 51, третий 52 и четвертьй 53 тактовые вко.дь: устройства.

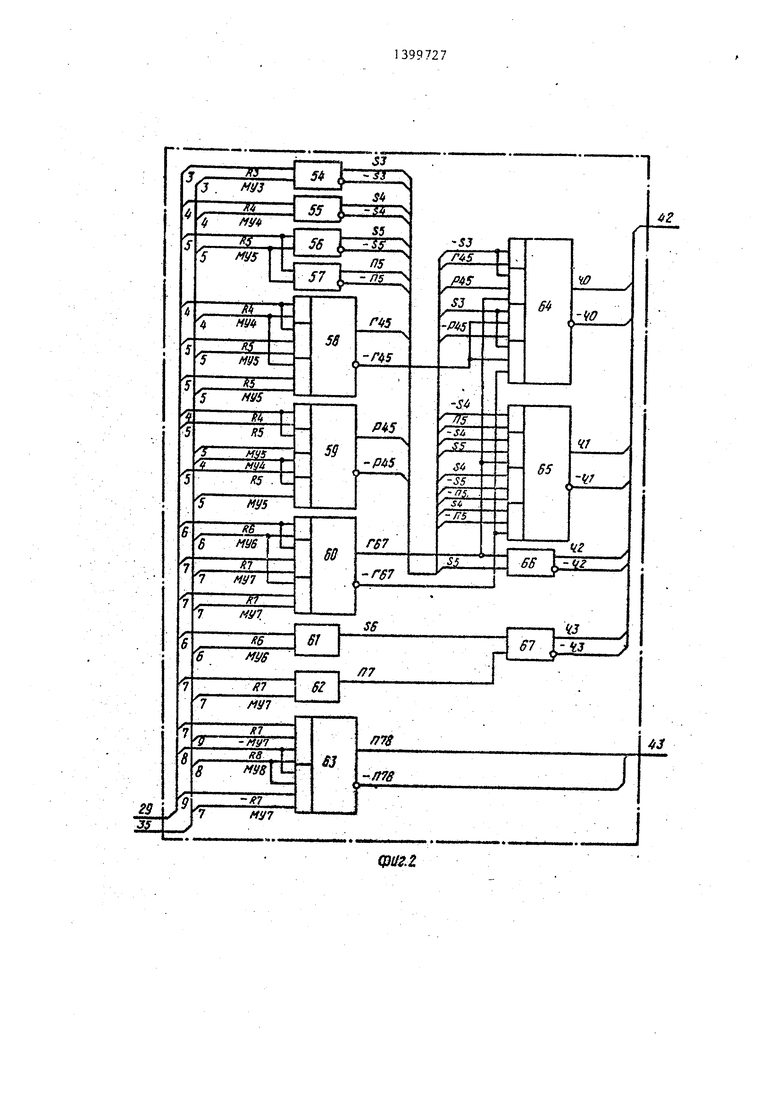

Формирователь 9 усеченного остатка (фиг,2) образуют элементы ИСКЛЮЧАЮЩЕЕ FJIli 54-56, элемент И 57, элементы ИЧ-ШИ 58-60, элемент ИСКЛЮЧАЮЩЕЕ ШШ 61, элемент И 62, элементы И- Ш1И 63-65 и элементы ИСКЛЮЧАЮЩЕЕ ИПИ 66 и 67.

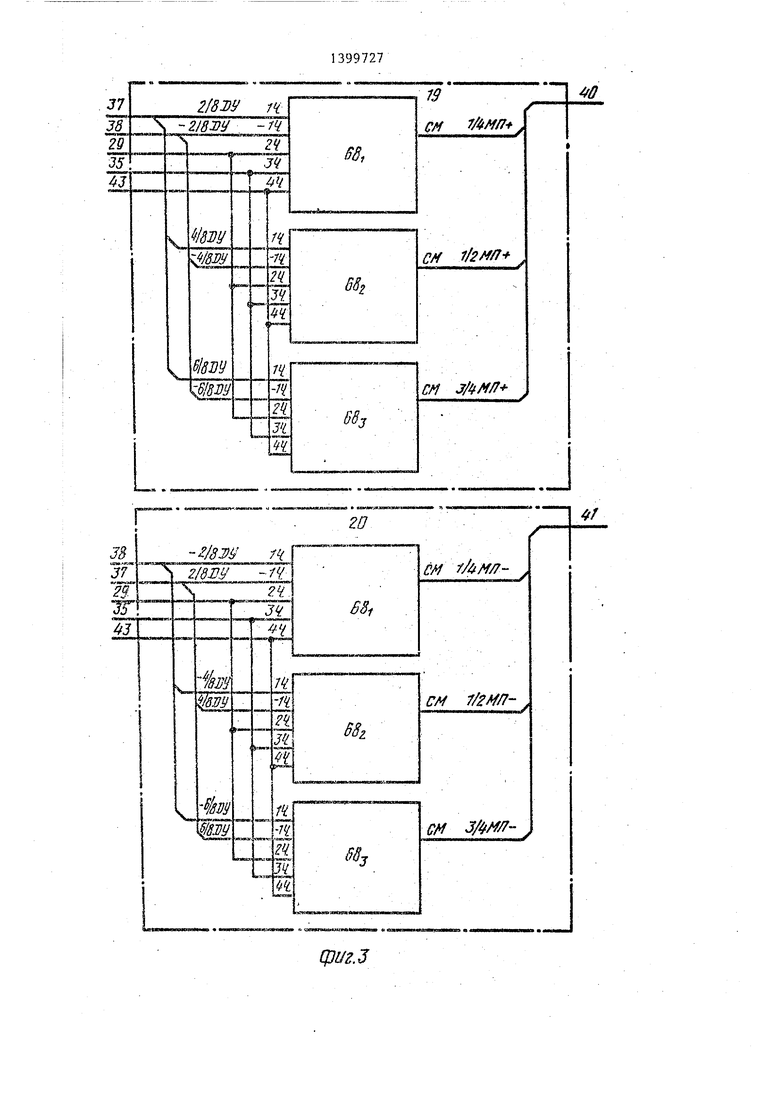

Блоки 19 и 20 суммирования пробных кратных,(фиг.3) состоят из груп- пь. сг мматоров пробных кратных

Сумматор 68 пробных кратных содержит элементы И-ИЛИ .

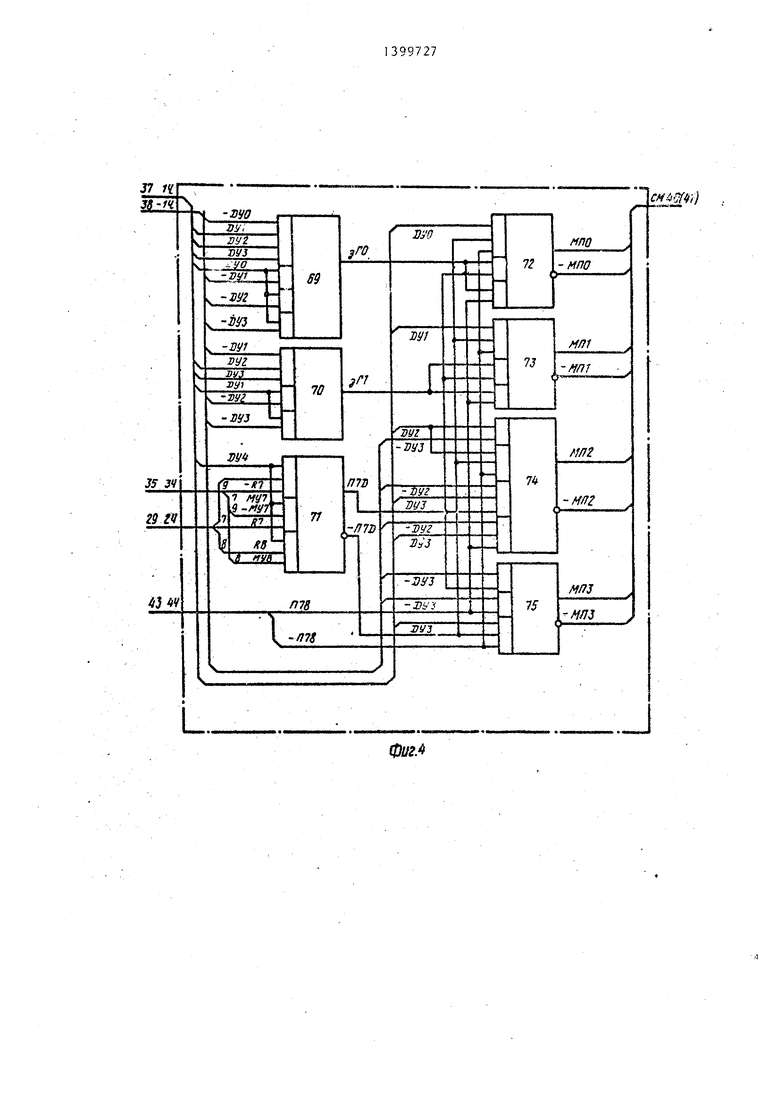

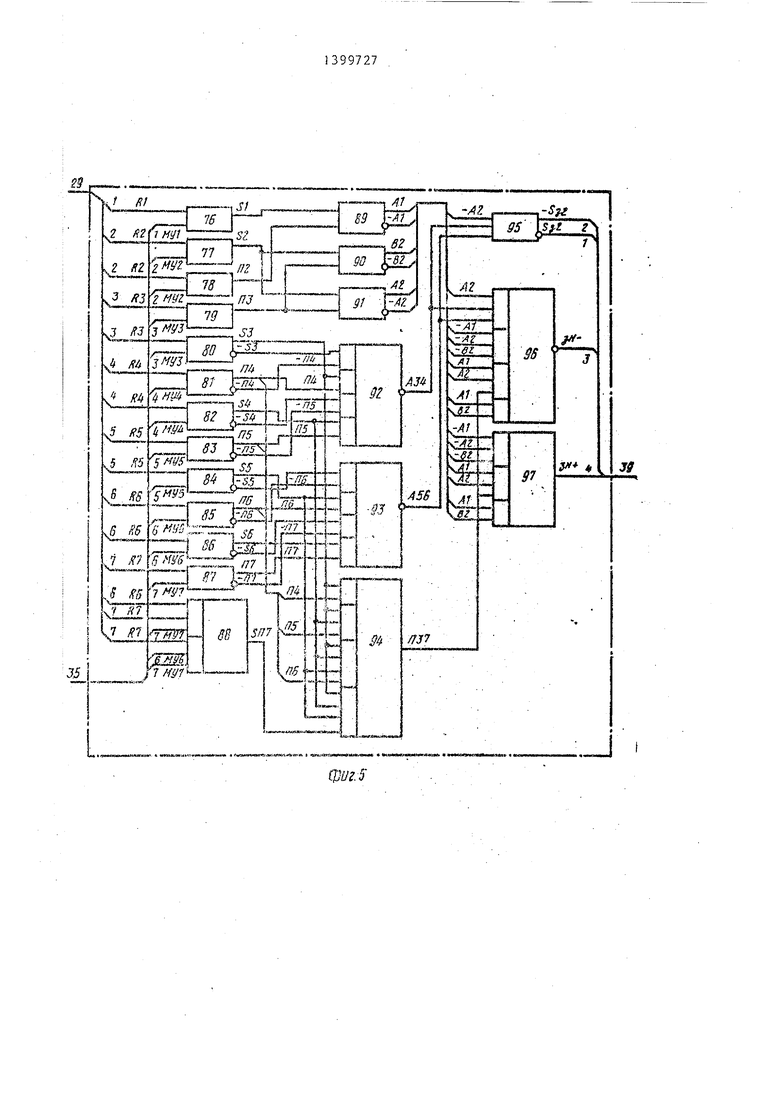

Формирователь 18 приближенного знака (фиг,5) вюпочает элементы

ИСКЛЮЧАЮШЕЕ ИЛИ 76 и 77, элементы И 78 и 79, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 80, элемент И 81 , элемент ИСКЛЮЧАК - ЩЕЕ ИЛИ 82, элемент И 83, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 84, элемент И 85,

элемент ИСКЛЮЧАКЩЕЕ ИЛИ 86, элемент И 87, элемент И-ИЛИ 88, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 89, элемент И. 90, элемент ИСЮПОЧАЮЩЕЕ IfflH 91, элементы И-ИЛИ 92-94, элемент И 95, элементы И-ИЛИ 96 и 97.

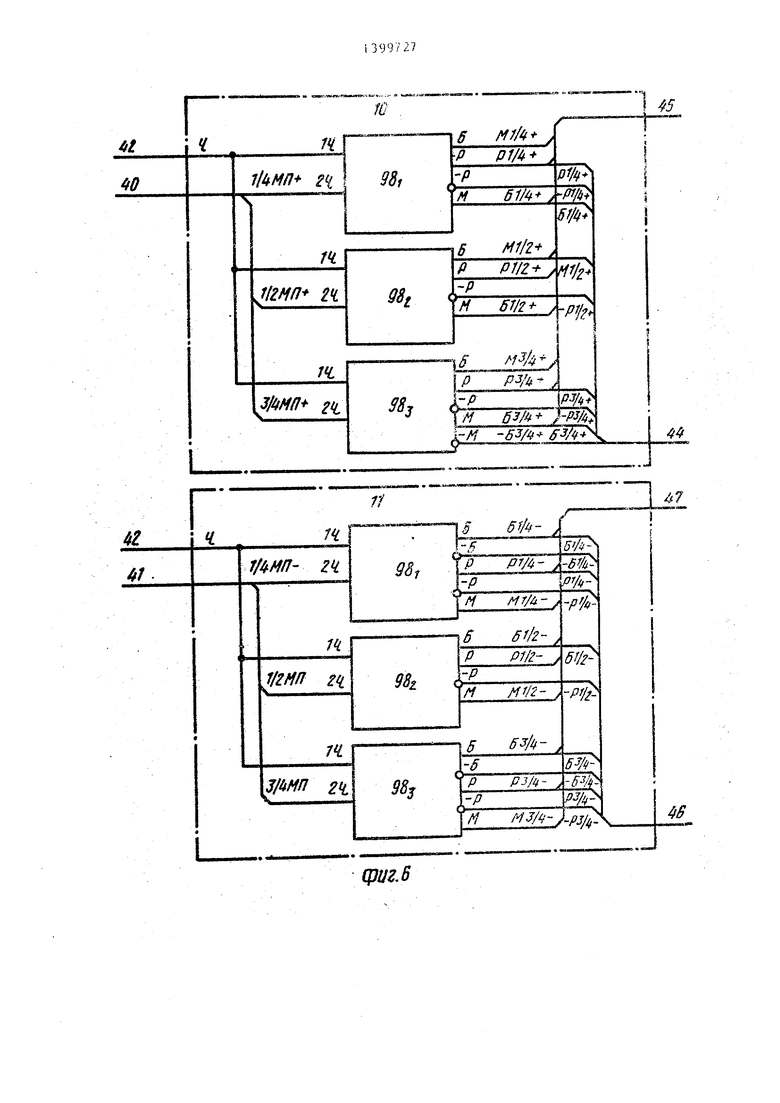

Блоки 10 и 1 1 сравнения (е1)иг.6) содержат труппь схем 98,-98з срав- нетшя,

3 39972

Схему 98 сравне1шя (фигч7) обраа--- - -н элементы И , элементы ИСЮ- - ЩЕЕ ИЛИ I02-104, элементы И 105anча ; ;а ус но ра ст го

108, элемент ИСКПЮЧ РЩЕ Шт 109, элеans-jMa инфорка1 ;;н регистра 3, переключая коммутатор регнстра на приег-i пор- ; ;а:1изованного делимоj o с входа 1 устройства (причем выходные разряд нормализатора подаются на зхсд регистра 3 со сдвигом на 3 разряда вправо в сторону младишх разрядов). С тактового входа 50 на входы разрешч-иит г;:и&ма

10 информахши регистров 16,3 и i : пс-дагт- ся сигнал длитепьностью п/3 (п -- разрядность входных операндов). На ре- гистр 3 при1шмается 1/8 нормалнзонан-- ного делимого (1/8 DE), в регистр 16 15 1/8 усеченного делителя (-1/8 DY), в регистр 13 записываются сигналы по выбору кратного -1/8 П, В спеду югцем такте в блок .- 4 производится выбор необхогхкмогс г/аткпго -1/8 DT (см, таблицу).. Таки-) обрая м, в первом ; ктарап,исчтном такте ( такт на вре™мент И 1 10, .элемент И-ЮТИ 1 1 , элемент И 112 и элемент И-ИЛИ МЗ,

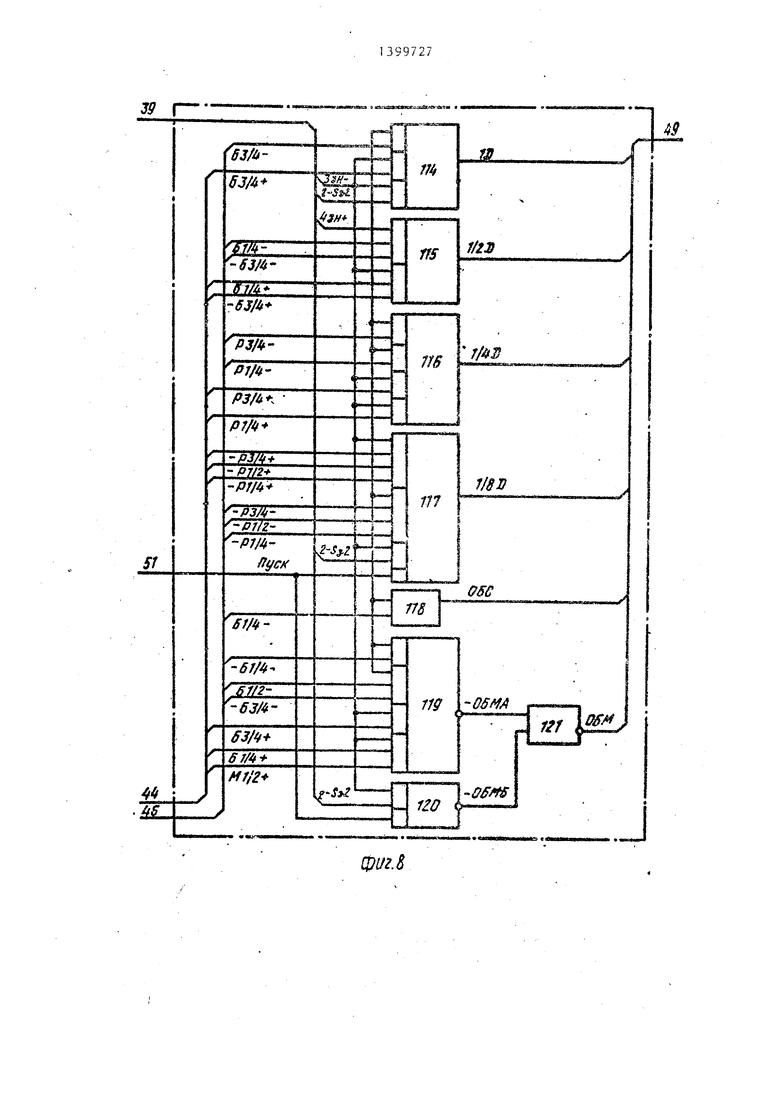

Дешифратор 12 выбора кратного (фиг. 8) содержит элементы И-.ШИ 1i 117, элемент И 118, элементе; И-ИЛИ 119 и 120 и элемент И-НЕ 21„

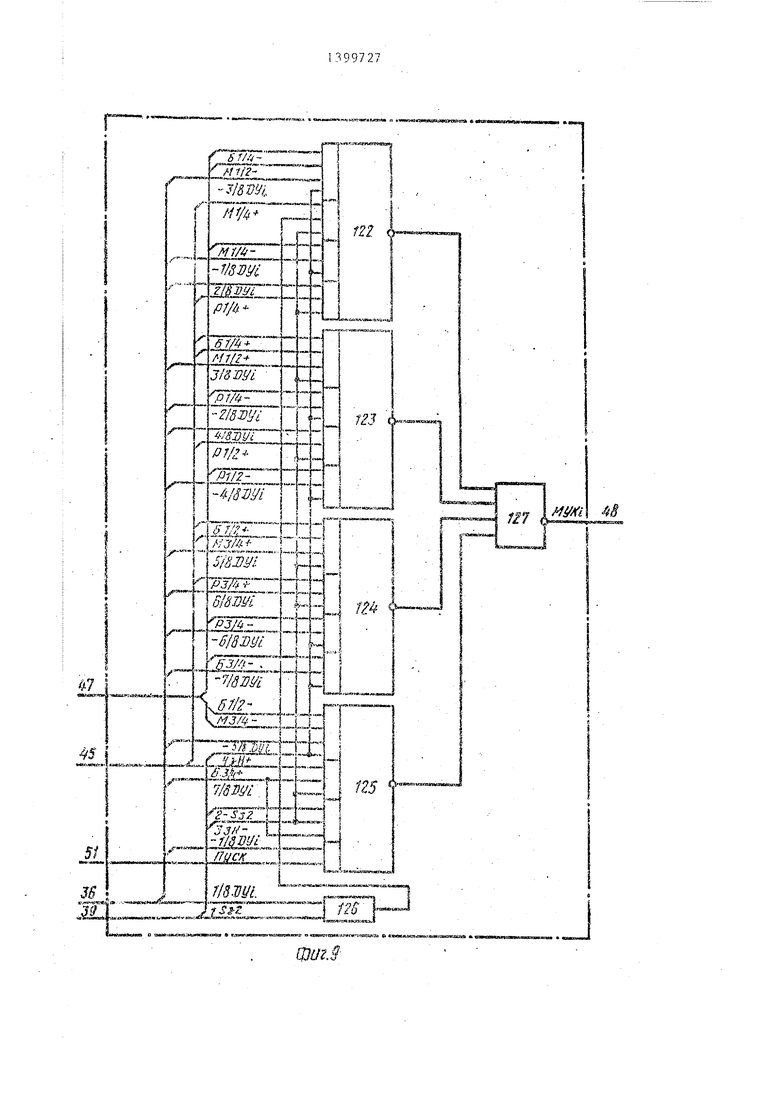

Разряд коммутатора 21 усеченных кратных (фиг,9) включает элементы И-ИЛИ 122-125, элемент И 126 и элемент И-ИЕ 127.

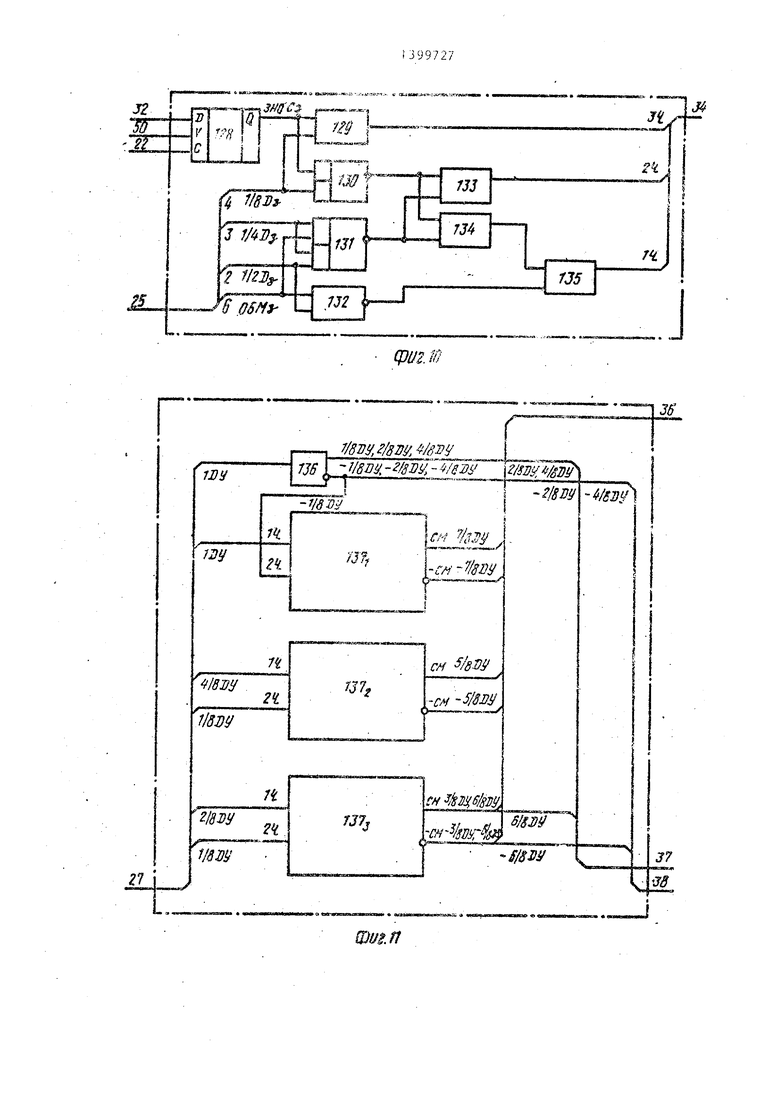

Формирователь 14 частного (фиг.10) содержит триггер. 128, элемент ИСКЛЮЧАЮЩЕЕ Rm-I 129, элементы 130 и 13 Ц элементы ИСКЛЮЧАИЦЕЕ ИЛИ 132 и 133, элемент И 1 ЗА и элемент ИСКЛЮ- 20 ИЛИ 135.

Формирователь 17 усеченных крат ных (фиг.11) образуют группа элементов И 136 и группа сумматоров 137, - 137.

Цифровые и буквенные выражения на фиг.2-12 представляют собой разряд-: ность операндов и мнемонические обозначения сигналов, используе -ые Б опк сании работы устройства.30 рядн1-;е, формгтрователь 1А - трехразряд

Блок коммутации кратных предстг.Б-г-шш,. регистр 13 и деши; т)сзтор 12. -:

ляет собой известное техническое реше- шестиразрядтгые, решстр 16, фоомиро- ние, реализован и функционирует ана- - логично известному.

Регистр 3 остатка выполнен на основе триггера- зап1елки с мультипле.ксо° ром на два входа - ИС100ТМ134.

Сумматор 8 остатка представляет собой быстродействуюпщй сверхпараллельный сумматор.

Сумматор 37, применяемый в фор- 1 мрователе- 7 усеченных кратн1-:х, выполнен в виде девятиразрядного cyiM- матора с приведением переносов. Рассмотрим работу устройства для двоичного деления для случая К-3

В первом такте работы устройства (фиг.12) однотактовый сигнал с тактового входа 52 подается на вход. раз

решеьшя приема инфо маи.ии регистра 2, 50 сдвищ тых кргти.--;:-. DY с двухрядным который .производит i рием нормализо-кодом 7-го и разрядов остаткаг

ванного делителя (DT) с входа I блоках 10 и 1 (Лиг.6) npoiicxoрсйства (фиго) , В следующем втором такте одкотакт1гый сигнал с тактового

входа 51 подается на вход коммутатора 55 ° остатка г, с выхода фop з poвaтeля 21, выбирая усеченное кратное9 с пoлoжитe,. пробными кратны-

DY на вход дешифратора 12, МП+ с выхода блока 19 и отрица шруя управляющие сигналы 1/8 ителькы ш МП- с вы-

ОБМ,-на вход задания направленияхода блока 20 соотБЗтственно. Каждая

менной диаграмме всегда ,ш- тсч действие R, /Ь DE - /8 DT, которым проверяется усповие . При 25 невыполнении .этого условия в Noiai jn i l разряд целой части частного заносится Г (Код ООГ ь регистр 15 частного)..

Регистры 2 и 3, блок 4, сумматор 8, регистр 5 - шестидесятичетырекраз-

ватель 7 и коммутатор 21 - дегшти- разрядные; фop aтpoвaтeль 9 и блоки 19 к 20 - четырехразряд тге.

Одновре - ень:о с вычислением остат- Т КЗ R на сумматоре 8 произ.водится ана ЛИЗ остатка с целью выработки частного и крать ого делителя для след -ющей итерации. В формирователе 9 произво- дится вычислег-л е од.норазряд гного

40

ченного остатка путем

ирования

усеченного предыдущего остатка R и усеченного кратного МУ. В блоках 19 45 и 20 происходит вычислеш е соотзетст венно положительнь х (Г/4 МП +, 1/2 MII+, 3/4 МП+) и отридатепььгых (1/4 Mil, 1/2 , 3/4 МП-) пробных крат ных путем суммирования усеченш к

дпт собственно анализ путем с авнё- кия в схемах 98 сравнения усеченно

-н

ans-jMa инфорка1 ;;н регистра 3, переключая коммутатор регнстра на приег-i пор- ; ;а:1изованного делимоj o с входа 1 устройства (причем выходные разряд нормализатора подаются на зхсд регистра 3 со сдвигом на 3 разряда вправо в сторону младишх разрядов). С тактового входа 50 на входы разрешч-иит г;:и&ма

0 информахши регистров 16,3 и i : пс-дагт- ся сигнал длитепьностью п/3 (п -- разрядность входных операндов). На ре- гистр 3 при1шмается 1/8 нормалнзонан-- ного делимого (1/8 DE), в регистр 16 5 1/8 усеченного делителя (-1/8 DY), в регистр 13 записываются сигналы по выбору кратного -1/8 П, В спеду югцем такте в блок .- 4 производится выбор необхогхкмогс г/аткпго -1/8 DT (см, таблицу).. Таки-) обрая м, в первом ; ктарап,исчтном такте ( такт на вре™

рядн1-;е, формгтрователь 1А - трехразряд

менной диаграмме всегда ,ш- тсч действие R, /Ь DE - /8 DT, которым проверяется усповие . При невыполнении .этого условия в Noiai jn i l разряд целой части частного заносится Г (Код ООГ ь регистр 15 частного)..

Регистры 2 и 3, блок 4, сумматор 8, регистр 5 - шестидесятичетырекраз-

шестиразрядтгые, решстр 16, фоомиро-

ватель 7 и коммутатор 21 - дегшти- разрядные; фop aтpoвaтeль 9 и блоки 19 к 20 - четырехразряд тге.

Одновре - ень:о с вычислением остат- Т КЗ R на сумматоре 8 произ.водится ана ЛИЗ остатка с целью выработки частного и крать ого делителя для след -ющей итерации. В формирователе 9 произво- дится вычислег-л е од.норазряд гного

ченного остатка путем

ирования

усеченного предыдущего остатка R и усеченного кратного МУ. В блоках 19 45 и 20 происходит вычислеш е соотзетст венно положительнь х (Г/4 МП +, 1/2 MII+, 3/4 МП+) и отридатепььгых (1/4 Mil, 1/2 , 3/4 МП-) пробных крат ных путем суммирования усеченш к

дпт собственно анализ путем с авнё- кия в схемах 98 сравнения усеченно

5

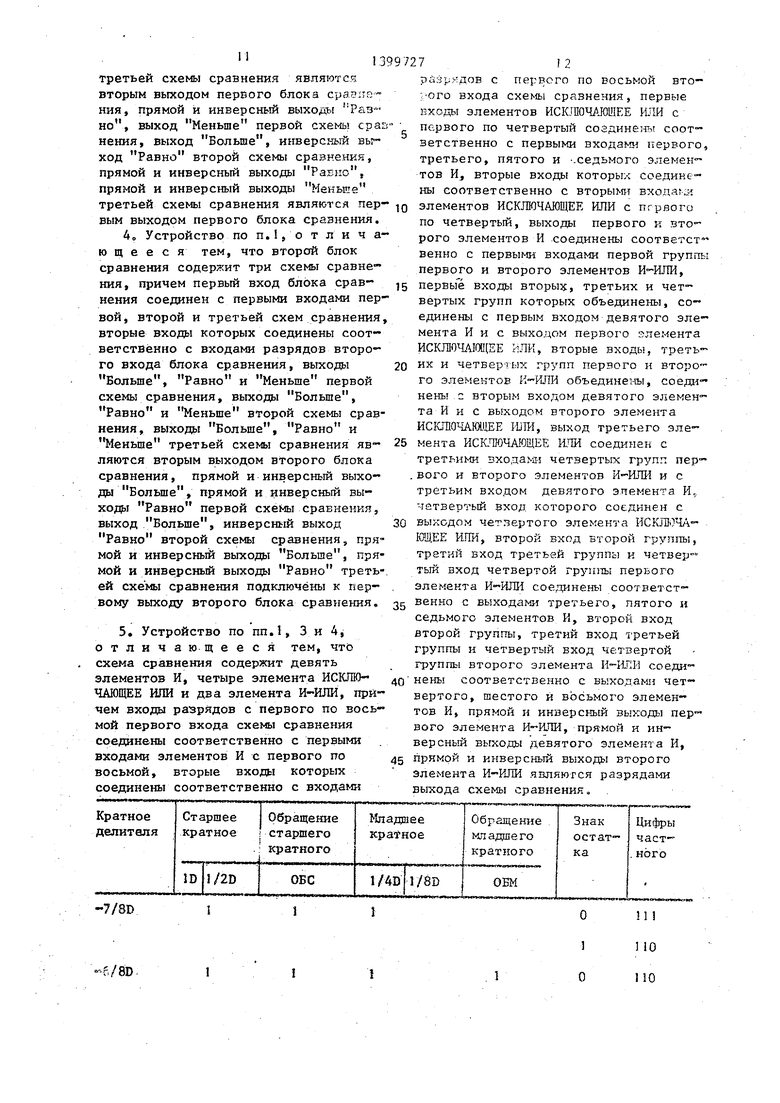

из трех схем 92 сравне1шя блока 10 (и блока 11) имеет выходы Больше, Равно и Меньше, объедапштые в общий выход. Группы вь кодов 45 блока Ш н 47 блока 1 поступают со- ответственно на управляющие входы - коммутатора 21 усечен1шх (ф1Г.9) S на информационный вход Tciporo поступают усеченнь е кратные с выхода 36 формирователя 17. На вх fi}4 де пи«1 ратора 12 поступают группа вь-|ходов 44 блока 10 и группа выхо дс|)В 46 блока 11 соответственно, не- офходимьш дпя формирования сигналов уфравлепия выбором кратного (фиг,8, таблица). Одновременно в формирова 18 приближенного знака по стар шин разрядам двухрядного кода остат ка R;, MY; формируются сигналы поло жительного ЗН+ и отрицательного ЗН 31,11аков остатка, которые поступая на коммутатора 2 и дешиф1)атора , управляют выбором результатов условного ангшиза. Если приблкженньг siiaK остатка положителен (ЗН+ 1 ) то выбирается результат отрицательн го (блок П) анализа, если приближе знак отрицателен (ЗИ- 1), то 1з 1б5фается результат положительного (Ьлок 10) апшшза, если равен нулю (т.е. неопределенный), то результат о|3оих анализов блокируются (ЗИ+ г 0), что соответствует выдаче

Ь

вого кратного делителя. TJoro, что знаковые разряды не участ ю|г в анализе, возможен случай, при котором результат анатп за оказывает ей неверным. Это может произойти, к да Значение остатка близко , а усечетшй остаток при имеет вид 10.1111. В этом случае необходамо значение кратного делителя (+7/8) формируется с помощью знаковых разрядов Sj.2 и Sg--2 (фнг.Вр 9 и 5). Скоммутированное по результатам ана Лиза дпя следующей итерации усечен- itoe кратное дшштеля записывается и регистр 16, а сигналы управления выбором кратного переписы.ваются в регистр 13.

Вычислепный остаток R с выхода Сумматора 8 записывается в регистр 3, а знак остатка с выхода- 32 сум матора 8 подается в формирователь 14. Вырабатывае1-«..1е в .ателе 14 очередные .три бита частного (фиг.10, таблица) записываются в хвостовые разряды .регистра. 15, на

вход разреше1шя сдвига информации которого подается сигнал с тактового входа 53.

По окончании итерационного прО цесса (через п/3 тактов) происходит обнуление управляющих сигналов на тактовых входах 5.0 и 53. Прием ин- формации на регистры 2,3,13,15 и 16 прекращается, на выходе 23 устройства формируется частное.

Таким образом, в предлагаемом устройстве за шесть логических уров ней элементов типа ЗИ 4ШШ/ЗИ 4ИЛИ - НЕ формируются три бита частного

Формула изобретения

кия, содержащее регистр сигналов выбора кратного, регистр делителя, регистр остатка, блок коммутации крат- шх, сумматор остатка, формирователь усеченного остатка, первый и второй

блоки сравнения, дешифратор выбора кратного, форм трователь частного, ре- гистр частного, причем информацион- Hbrti вход устройства подключен к ин формационному входу регистра делите

ля, управляющий вход и первьй, вто- рой информационные входы блока ком°- мутации кратных подключены к выходам регистра сигналов выбора кратного, регистра делителя и регистра остатка

соответственно, первый и второй вы ходы блока коммутации кратных подклю чены соответственно к входам первого и второго слагаемых сумматора остат ка, выход знака которого подключен к первому информационному входу фор №1рователя частного, выход сумматора остатка подключен к перво ну информационному входу регастра остатка, выход формирователя частного

подключен к информационному входу регистра частного, выход которого является выходом устройства, первый вход формирователя усеченного остат ка подхшючен к выходу ст.арших разря- дов регистра остатка, выход остатка формирователя усеченного остатка под- ключей к первым входам первого и второго блоков сравнения, первые выходы которых подключены соответственно к

первому и второму -информационным входам дешифратора выбора кратного выход которого подгслючен к информ а- ционному входу регистра сигналов вы- бора кратного, выход разрядов кото

рого подключен к второму информа- ционному входу формирователя частно го, вход синхронизации устройства подключен к входам синхронизации регистра делителя, регистра остаткаj регистра сигналов выбора кратного, регистра частного и формирователя частного, первый тактовый вход устройства соединен с входом разрешения приема регистра остатка и с входом разрешения приема формирователя частного, второй тактовый вход устройства соединен с входом задания направления приема регистра остатка третий тактовый вход устройства соединен с входом разрешения приема регистра делителя, четвертый тактовый вход устройства соединен с входом разрешения приема регистра частного, отлич-ающееся тем, что, с целью повьш1ения быстродействия, в него введены регистр усеченного кратного, формирователь усеченных кратных, формирователь приближенного знака, первый и вто- рой блоки суммирования пробных кратных . KOMhQ TaTop усеченных кратных, причем информационный вход устройства подключен к второму информационному входу регистра остатка, выход старших разрядов которого соединен с первым входом формирователя приближенного знака, второй вход которого соединен

с выходом регистра усеченных кратных, 35 приближенного знака соединены

выход старших разрядов регистра делителя подключен к входу формирователя усеченных кратных, первый выход которого подключен к информационному входу коммутатора усеченных кратных, второй и третий выходы формирователя усеченных кратных соединены соответственно с входами первых елагае№1Х первого и второго блоков суммирования

дробных кратных,входы вторых слагаемых 45 вход первой группы и

первый вход второй группы которого со .динены соответственно с первыми входа ми пятого и шестого злементов И,входЬ1 разрядов с первого по седьмой второго

которых объединены и соединены с выходом старших разрядов регистра остатка, выход регистра усеченного кратного соединен с входами третьих слагаемых первого и второго блоков суммирования пробных кратных, е вторым входом формирователя усеченно го остатка, выход переноса которого соединен с входами четвертых слагав- ьмх первого и второго блоков сумми ;- рования пробных кратш 1Х, входы пятых слагаемых которых соединены соответственно с третьим и вторым выходами формирователя усеченных кратных, выхо.цы первых и вт:орого блоков сунмнр6°- вання проб1о 1х кратных подключены соответственно к вторым входам первого и второго блоков сравнения, первый и второй управляющие входы комг-п та- тора усеченных кратных подключены к вторым выходам первого и второго блоков сравнения соответственно, ьы-

ход формирователя приближенного знака подключен к входу разрешения дешифратора выбора кратного и к третьему управляющему входу комментатора усеченных кратных, выход которого со

единен с информационным входом ре гистра усеченных кратного, вход разрешения приема которого соединен с входом разрешения приема регистра сигналов выбора кратного и с первым

тактовым входом устройства, второй тактовый вход которого соединен с четвертым управляющим входом коммутатора усеченных кратных и с входом установки дешифратора выбора кратного,

вход синхронизации устройства соединен с входом синхронизации регистра усеченного кратного,

приближенного знака содержит восемь элементов ИСКЛК ЧАЮ01ЕЕ ШШ, восемь злементов И и шесть злементов И-ИЛИ, причем входы разрядов с первого по седьмой первого входа фop шpoвa-

соответственно с первыми входами элементов ИСКЛЮЧ Юи1ЕЕ ИЛИ с первого по шестой и с первым входом первой группы первого элемента И-1ШИ, первые 4Q входы элементов И с первого по шестой соединены соответственно с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с второго по шестой и с первым входом первой группы первого элемента

первый вход второй группы которого сое- .динены соответственно с первыми входами пятого и шестого злементов И,входЬ1 разрядов с первого по седьмой второго

входа формирователя приблюкенного знака соединены соответственно с входами элементов ИСКЛЮЧАЮШЕЕ ИЛИ с первого по шестой и с третьим входом цервой Группы первого элемента И-ИЛИ, вторые входы злементов И с первого по шестой соединены соответственно с вторыми входами элементов ИСКЛЮЧАЩЕЕ ИЛИ с второго по шестой и с третьим входом первой группы первого элемента

, второй и третий входы второй 1труппы которого соединены соответ ctBeiiHO с вторыми входами пятого н шестого элементов И, пыходся первых Э1|1ементов ИСКЛЮЧАЮЩЕЕ РШИ и И сое- дШнепы соответственно с первым и иторым входами седьмого элемента ИСЮ) ШШ, выход второго элемента ,ЕЕ imii соединен с первым входами седьмого элемента И . и| восьмого элемента РЮКЛЮЧАЮЩЕЕ ИЛИ, в|горые входы которых объединены и с|эед 1не1Ш с выходом второго элемен- т И, первые входы первой, второй,. т|ретьей н четвертой групп второго элемента Н-ИПИ соединены соответст- ненно с инверсным и пряг-алм выходами тЬет.ьего элемеит.а ИСКЛЮМЛЩЕЕ ШШ,

ветственно с инверс1шми выхода1 1и седьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второго н третьего элементов И-ИЖ, g первые входы первой, второй, третьей и четвертой групп пятого элемента соединены соответственно с прямым выходом восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с инверсным н прямым вы- 10 ходамн седьмого элемента ИСКЛЮЧАЮЩЕЕ 1-ШИ, с прямым выходом седьмого эле мента ИСКЛЮЧАЮЩЕЕ ИЛИ, инверсные выхода второго и третьего элементов И- ИЛИ соединены соответственно с 15 вторым и третьим входами первой группы пятого элемента И-ИЛИ, второй и третий.входы второй группы, вторые входа третьей и четвертой групп которого соединены соответственно с

инверсным и прямым выходами четвер- 20 инверсными выходами восьмого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и седьмого элемента И, с пряьымн выходами восьмого элемента. ИСКгаоЧАЩЕЕ ИЛИ и седьмого элемента И, инверсные выходы седьмого 25 и ВОСЬМОГО элементов ИСКЛЮЧАЩЕЕ ИЛИ н седьмого элемента И соединены соответственно с входами первой группы жестого элемента И- ИЛИ, первые входы второй и третьей групп которого 30 объедлнеж jj соединены с прямым выходом седьмого элемента ИСКЛЮЧАЩЕЕ ШШ, пря№1е выходы восьмого элемента ИСЮ1ЮЧА1 ЩЕЕ 1Ш1 и седьмого элемента И соединены соответственно с вторы- ми входами второй и третьей групп шестого элемента , третий вход второй группы.которого объединен с третьим входом третьей группы пятого элемента и соединен с выходом 40 четвертого элемента , инверснь1Й и прямой выходы восьмого элемента И,ин-. версный выход пятого и выход шестого элементов И-ИЛИ являются соответственно первым, BTOpbSM, третьим и четвертым 45 раэрядами выхода формирователя приближенного знака.

второй группы, четвертые вход треть- вторые входы которых соединены соот- ей н четвертой групп которого соеди- ветственно с вxoдa й разрядов второго иены соответственно с пря№1Ми выхода- 55 Д блока сравнения, выходы Больше ми третьего, четвертого и пятого эле- Равно и Меньше первой схемы срав- меитов И и с выходом первого элеманта neimfi., выходы Больше, Равно и , первый} второй и третий входы Меньше .второй схемы сравнения, вы- восьмого э:$емента И соединены соот коды Больше, Равно и Меньше

ого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вто liae входа первой, второй, третьей 1 четвертой групп второго элемента Н -ТШИ соединены соответственно с ип- йерсным и прямым выходами третьего Элеме}1та И, с инверс5 ым п прямым выходами четвертого элемента И, первые ВХОД1Л первой,второй, третьей и чет йсртой групп третьего элеманта И ШШ соединены соответствепно с mi- iepciibiH и пря№1 5 ззыходами пятого флемепта.ИСЮПФШОЩЕЕ ИЛИ, с янверс- l&iM и выходам - шестого эле- .Цнта ИСКТПОМЛЮИЩЕ , вторые входы Первой,.., BTopoii, третьей и четвертой Гругш третьего элемента соедине- Ны соответственно с инверС ШМ п пря- t-ыы выходами пятого элемента Л, с JniBepcnaM я пря1-ым выходами шестого элемента И, прямой выход третьего элемента ИСКЛЮЧ МОПЩЕ ИЛИ соедкнеп с первыми входам первой, второй, трет ей и четвертой групп четвертого эле мента I МШИ 5 вторые входы второй, третьей и четвертой групп которого объединены и соеди епы с прямзлм вы- - ходом четвертого элемента ИСКГЮЧАЮ- Ш.ЕЕ ШШ, Щ1ЯМСЙ выход пятого элемен та ИСКЛЮЧАК01ЕЕ ИЛИ .соединен с треть

третьей схемы сравнения являются вторым выходом первого блока сраоик- ния, прямой и инверсный выходы Разно, выход Меньше первой схемы сраз нения, выход Больше, инверсный выход Равно второй схемы сравнения, прямой и инверсный выходы Равно, пряной и инверсный выходы Мекыке третьей схемы сравнения являются пер- вым выходом первого блока сравнения.

4„ Устройство по п.J о т л и ч а- ю щ е е с я тем, что второй блок сравнения содержит три схемы сравнения, причем первый вход блока сравнения соединен с первыми входами первой, второй и третьей схем сравнения, вторые входы которых соединены соответственно с входами разрядов второго входа блока сравнения, выходы Больше, Равно и Меньше первой схемы сравнения, выходы Больше, Равно и Меньше второй схемы сравнения, выходь Больше, Равно и Меньше третьей схемы сравнения яв- ляются вторым выходом второго блока сравнения, прямой и инверсный выходы Больше, прямой и инверсный выхода Равно первой схемы сравнения, выход Больше, инверсный выход Равно второй схемы сравнения, прямой и инверсный выходы Больше, прямой и инверсный выходы Равно третьей схе мы сравнения подключены к первому выходу второго блока сравнения,

5, Устройство по ПП.1, 3 и 4| отличающееся тем, что схема сравнения содержит девять элементов И, четыре элемента ИСКЛЮ- ЧАЮЩЕЕ ИЛИ и два элемента И-ИЛИ, при чем входы разрядов с первого по восьмой первого входа схемы сравнения со едннены соответственно с первыми входами элементов И с первого по восьмой, вторые входы которых соединены соответственно с входами

-7/8D

-6/8D

5

0

5 5

0 5

0

рййрядов с первого по восьмой вто- Г Ого входа схемы сравнения, первые кходы элементов ИСК.ШОЧАЮЩЕЕ Ш1И с первого по четвертый согдинены соответственно с первыми входами первого, третьего, пятого и -.седьмого элемен тов И, вторые входы которых соединены соответственно с вторымт входа ч элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с пгрвого по четвертый, выходы первого к второго элементов И -соединены соответственно с первыми входами первой группы первого и второго элементов , первы е входы вторых, третьих и четвертых групп которых объединены, соединены с первым входом девятого элемента И и с выходом первого Эo eмeнтa ИСКЛЮМ1Ш ЕЕ ИЛИ, вторые входы, треть-- их и четвертых групп первого н второ - го элементов И -ИЛИ объединв;, соеди нень, вторым входом девятого элемен- та И и с выходом второго элемента ИСКТПОЧАЮЩЕЕ ItlTH, выход третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с третьими зхода а- четвертых групп пер- .вого и второго элементов И-ИШ1 и с третьим входом девятого элемента И., четвертый 5ход которого соединен с выходом четвертого элемента ИСКЛЮЧА- ЮШ.ЕЕ ИЛИ, второй вход второй групгш, третий вход третьей группы и четвер- тый вход четвертой грушты первого элемента И-ИЛИ соединены соответственно с выходами третьего, пятого и седьмого элементов И, второй вход второй группы, третий вход третьей группы и четвертый вход четвертой группы второго элемента И-ИПИ соединены соответственно с выходами четвертого, шестого и восьмого элементов И, прямой и инверсный выходы первого элемента И-ШШ, прямой и инверсный выходы девятого элемента И, прямой и инверсный выходы второго элемента И-ИЛИ являются разрядами выхода схемы сравнения.

П1

1 10 ПО

5/8D -A/8D

I

|3/8D

2/8D i/8D

0

J/8D 2/8D

3/8D 4/8D

5/8D $/8D

4Й

(plJZJ

)

(pt/2,S

фи.7

39

I л M JbJCjacJtriiaia&t af fl Hi )

Дл

J

ф//г

фи

J2

3HffC

Щ

W г

iMCCTtS

3i

J4

q:)U2.ifi

фиш

fr зт

ют 7fT

.п

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3504167, кд | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Процессор центральный, ч | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Пюпитр для работы на пишущих машинах | 1922 |

|

SU86A1 |

Авторы

Даты

1988-05-30—Публикация

1986-12-31—Подача