IN:)

О5

ю

4

;о

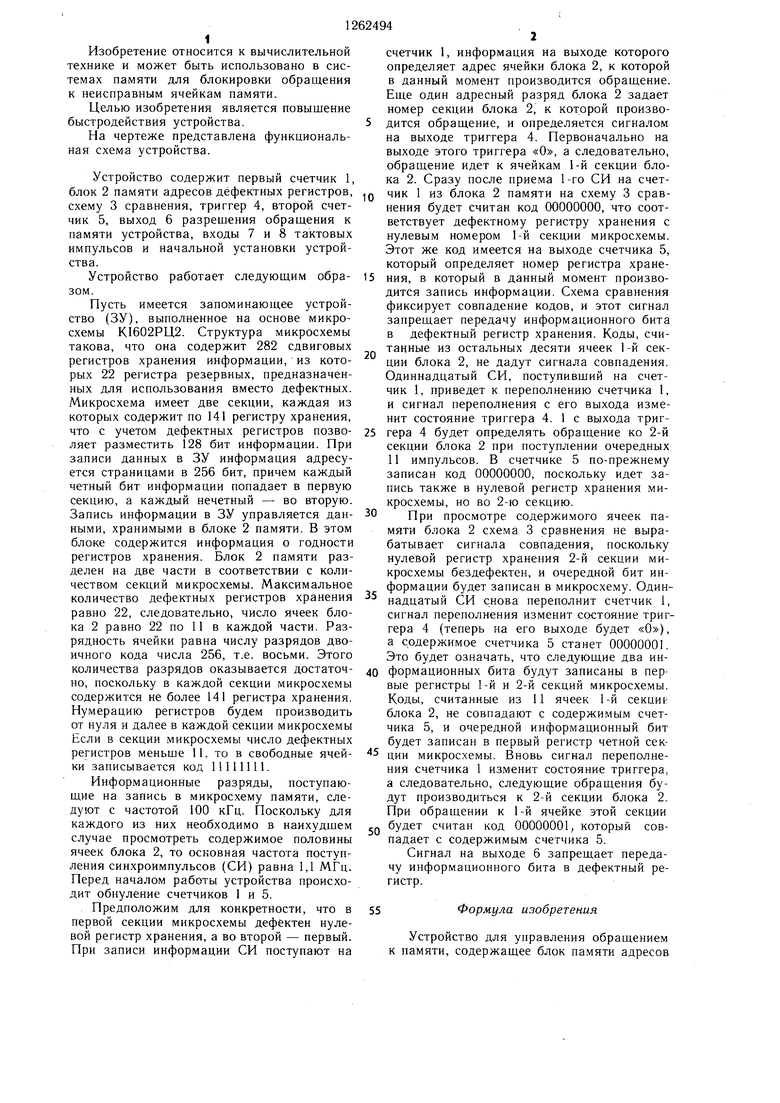

4 Изобретение относится к вычислительной технике и может быть использовано в системах памяти для блокировки обращения к неисправным ячейкам памяти. Целью изобретения является повышение быстродействия устройства. На чертеже представлена функциональная схема устройства. Устройство содержит первый счетчик 1, блок 2 памяти адресов дефектных регистров, схему 3 сравнения, триггер 4, второй счетчик 5, выход 6 разрешения обращения к памяти устройства, входы 7 и 8 тактовых импульсов и начальной установки устройства. Устройство работает следующим обраПусть имеется запоминающее устройство (ЗУ), выполненное на основе микросхемы К1602РЦ2. Структура микросхемы такова, что она содержит 282 сдвиговых регистров хранения информации, из которых 22 регистра резервных, предназначенных для использования вместо дефектных. Микросхема имеет две секции, каждая из которых содержит по 141 регистру хранения. что с учетом дефектных регистров позволяет разместить 128 бит информации. При записи данных в ЗУ информация адресуется страницами в 256 бит, причем каждый четный бит информации попадает в первую секцию, а каждый нечетный - во вторую. Запись информации в ЗУ управляется данными, хранимыми в блоке 2 памяти. В этом блоке содержится информация о годности регистров хранения. Блок 2 памяти разделен на две части в соответствии с количеством секций микросхемы. Максимальное количество дефектных регистров хранения равно 22, следовательно, число ячеек блока 2 равно 22 по 11 в каждой части. Разрядность ячейки равна числу разрядов двоичного кода числа 256, т.е. восьми. Этого количества разрядов оказывается достаточно, поскольку в каждой секции микросхемы содержится не более 141 регистра хранения. Нумерацию регистров будем производить от нуля и далее в каждой секции микросхемы Если в секции микросхемы число дефектных регистров меньше 11, то в свободные ячейки записывается код 11111111. Информационные разряды, поступающие на запись в микросхему памяти, следуют с частотой 100 кГц. Поскольку для каждого из них необходимо в наихудшем случае просмотреть содержимое половины ячеек блока 2, то основная частота поступления синхроимпульсов (СИ) равна 1,1 МГц. Перед началом работы устройства происходит обнуление счетчиков 1 и 5. Предположим для конкретности, что в первой секции микросхемы дефектен нулевой регистр хранения, а во второй - первый. При записи информации СИ поступают на счетчик 1, информация на выходе которого определяет адрес ячейки блока 2, к которой в данный момент производится обращение. Еще один адресный разряд блока 2 задает номер секции блока 2, к которой производится обращение, и определяется сигналом на выходе триггера 4. Первоначально на выходе этого триггера «О, а следовательно, обращение идет к ячейкам 1-й секции блока 2. Сразу после приема 1-го СИ на счетчик 1 из блока 2 памяти на схему 3 сравнения будет считан код 00000000, что соответствует дефектному регистру хранения с нулевым номером 1-й секции микросхемы. Этот же код имеется на выходе счетчика 5, который определяет номер регистра хранения, в который в данный момент производится запись информации. Схема сравнения фиксирует совпадение кодов, и этот сигнал запрещает передачу информационного бита в дефектный регистр хранения. Коды, считанные из остальных десяти ячеек 1 -и секции блока 2, не дадут сигнала совпадения. Одиннадцатый СИ, поступивший на счетчик 1, приведет к переполнению счетчика 1, и сигнал переполнения с его выхода изменит состояние триггера 4. 1 с выхода триггера 4 будет определять обращение ко 2-й секции блока 2 при поступлении очередных В счетчике 5 по-прежнему 11 импульсов записан код 00000000, поскольку идет запись также в нулевой регистр хранения микросхемы, но во 2-ю секцию. При просмотре содержимого ячеек памяти блока 2 схема 3 сравнения не вырабатывает сигнала совпадения, поскольку нулевой регистр хранения 2-й секции микросхемы бездефектен, и очередной бит информации будет записан в микросхему. Одиннадцатый СИ снова переполнит счетчик 1, сигнал переполнения изменит состояние триггера 4 (теперь на его выходе будет «О), а содержимое счетчика 5 станет 00000001. Это будет означать, что следующие два информационных бита будут записаны в первые регистры 1-й и 2-й секций микросхемы. Коды, считанные из 11 ячеек 1-й секци блока 2, не совпадают с содержимым счетчика 5, и очередной информационный бит будет записан в первый регистр четной секц„„ микросхемы. Вновь сигнал переполнения счетчика 1 изменит состояние триггера, а следовательно, следующие обращения будут производиться к 2-й секции блока 2. При обращении к 1-й ячейке этой секции будет считан код 00000001, который совпадает с содержимым счетчика 5. Сигнал на выходе 6 запрещает передачу информационного бита в дефектный регистр. Формула изобретения Устройство для управления обращением к памяти, содержащее блок памяти адресов

дефектных регистров и первый счетчик, причем выход первого счетчика подключен к входу младших разрядов адреса блока памяти адресов дефектных регистров, вход установки в «О первого счетчика подключен к входу начальной установки устройства, отличающееся тем, что с целью повышения быстродействия устройства, в него введены второй счетчик, триггер и схема сравнения, причем выход триггера подключен к счетному входу второго счетчика и к входу старших разрядов адреса блока памяти адресов

дефектных регистров, выход которого подключен к первому входу схемы сравнения, выход и второй вход которой подключены соответственно к выходу разрешения обращения к памяти устройства и к выходу второго счетчика, вход начальной установки устройства подключен к входам установки «О триггера и второго счетчика, синхровход и выход переполнения первого счетчика подключены соответственно к входу тактовых импульсов устройства и к счетному входу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Устройство для программного управления | 1987 |

|

SU1439533A2 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Ассоциативное запоминающее устройство | 1984 |

|

SU1234880A1 |

| Устройство для моделирования сетевого графика | 1977 |

|

SU686033A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Параллельный сигнатурный анализатор | 1984 |

|

SU1182523A1 |

Изобретение относится к области вычислительной техники и может быть использовано в системах памяти для блокировки обращения к неисправным ячейкам. Целью изобретения является повышение быстродействия. Устройство содержит два счетчика, триггер, схему сравнения и блок памяти адресов дефектных регистров. Поставленная цель достигается за счет увеличения количества управляемых объектов при фиксированном объеме блока памяти адресов дефектных регистров. 1 ил.

| Устройство для управления записьюи СчиТыВАНиЕМ иНфОРМАции | 1979 |

|

SU809181A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| /V aйopoв С | |||

| А., Новиков Г | |||

| И | |||

| Принципы организации цифровых машин | |||

| Л.: Машиностроение,1974, с | |||

| Уровень с пузырьком | 1922 |

|

SU388A1 |

Авторы

Даты

1986-10-07—Публикация

1985-02-28—Подача