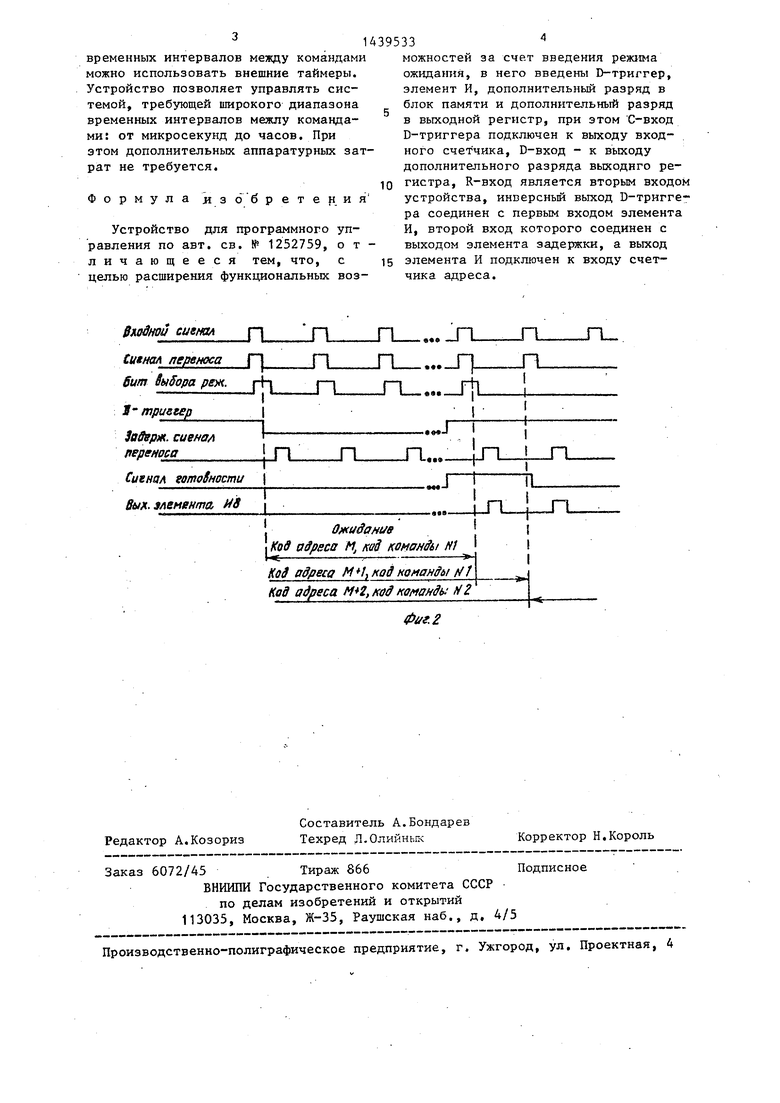

Изобретение относится к автомати-. ке и вычислительной технике и может :найти применение в качестве устройст- ;ва у: 1равления системами в реальном масштабе времени. I Цель изобретения - расширение функциональных возможностб й за счет рведения релсима ожидания. На фиг.1 приведена структурная хема устройства; на фиг.2 - времеи- ая диаграмма его работы.

Устройство содержит входной счетчик 1, дешифратор 2, выходной регистр

3, блок 4 памяти, элемент. 5 задержки, счетчик б адрегра, В триггер 7, элемент И 8,.Каждая ячейка блока 4 памяти содерлшт код операции, код временного интервала и бит выбора режима. Начальная запись в блок 4 Памяти может быть осутдествлена раз- (пичкыми способами (цепи начал:ьной |заик;си блока памяти, начальной ус- |таыовки входного счетчика 1 и счет- чикг. б адреса на схеме не показаны), сд ройство работает следугои и - об- азом.

Ео кома нде, в которой установлен .|бит выбора режима (логическая 1 в ;| дополнительном разряде блока 4 памяTH)S устройство переходит в режим ождания, т,е, следующая команда выполнется после прихода на второй вход устройства сигнала х отовности от управляемой систег-ЕЫ. : в исходном состоянии ВО все раз- ;ряды входного счетчика 1 записаны :единиды, D- триггер 7 и счетчик б ад ipeca обкулеШ, что соответствует ад- ресу первой ячейки блока 4 памяти. Сигнал входной частоты, поступив™ тш на. первьй вход устройства, выз зшает появление сигнгша переполнения входного счетчика 1, которьш, поступив на управляющий вход (считывания) блока 4 памяти, производит считываний содерждаюго первой ячейки в выходной регистр 3. Код операции со старших разрядов выходного . регистра 3 поступает на вход дешифратора 2, и на выходе устройства появляются сигналы управления. С выхода младших разрядов регистра 3 код временного интервала, через который необходимо выполнить следующую ко

мандУр записывается во входной счетчик 1. С выхода бита выбора режима регистра 3 сигнал поступает на D-вход триггера 7, которьй по сшзду сигнала

0

5

0

5

0

5 0 5

0

5

переполнения счетчика 1 устанавливается в состояние (нулевое или единичное), определяемое сигналом на его D-входе. Если бит выбора режима не установлен, то D-триггер 7 устанавливается в нулевое состояние и разрешает прохождение через элемент И 8 задержанного элементом 5 задержки сигнала переполнения счетчика 1. Этот сигнал увеличивет содержимое счетчика 6 адреса на единицу.

Сигналами входной частоты отсчитывается заданный временной интервал мелоду командами. Сигнал переполнения счетчика 1 вызывает считывание содержимого второй ячейки блока 4 памяти и т.д. до тех пор, пока в очередной команде не будет установлен бит выбора режима. В этом случае D-триггер 7 устанавливается в единичное состояние и запрещает прохождение сигнала переполнения через элемент И 8, поэтому в счетчике б адреса код адреса не меняется. Устройство переходит в режим ожидания. Сигналы переполнения в блоке 4 памяти производят считывание содержимого одной и той же ячейки памяти,адрес которой хранится в счетчике б адреса. В команде, по которой происходит переход устрой- - ства в режим ожидания, целесообразно установить код временного интервала такой величины, во все разряды входного счетчика 1 записывались единицы, тогда сигнал переполнения будет возникать по первому импульсу сигнала входной частоты, уменьшая тем самым мертвое время устройства. По сигналу готовности от управляемого устройства, поступающему на R-вход D-триггера 7, последний переключится в нулевое состояние и разрешит прохождение через элемент И 8 сигнала переполнения. Содержимое счетчика б адреса увеличивается на единицу. Приход следующего сигнала переполнения вызовет считьшание содержимого ячейки памяти и т.д. В дальнейшем работа устройства повторится. В качестве элементной базы устройства могут быть выбраны микросхемы с ерии К155.

В устройстве за счет введения режима ожидания становится возможным организовать обратные связи; от управляемой системы - сигнал готовности, цри этом связь проста, и не требует введения холостых команд. Кроме .того, для формирования длительных

временных интервалов между командами можно использовать внешние таймеры. Устройство позволяет управлять системой, требующей широкого диапазона временных интервалов межлу командами: от микросекунд до часов. При этом дополнительных аппаратурных затрат не требуется.

Формула изобретения

Устройство для программного управления по авт. св. № 1252759, отличающееся тем, что, с целью расширения функциональных возА39533

можностей за счет введения реж11ма ожидания, в него введены D-триггер, элемент И, дополнительный разряд в блок памяти и дополнительный разряд в выходной регистр, при зтом С-вход D-триггера подключен к выходу входного счетчика, D-вход - к выходу дополнительного разряда выходнго регистра, R-вход является вторым входом устройства, инверсньй выход D-триггера соединен с первым входом элемента И, второй вход которого соединен с выходом элемента задержки, а выход

элемента И подключен к входу счетчика адреса.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1990 |

|

SU1784939A1 |

| Ассоциативное оперативное запоминающее устройство | 1989 |

|

SU1714682A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

| Цифровая электронная вычислительная машина последовательного действия | 1975 |

|

SU532295A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ЖИДКОСТИ | 1991 |

|

RU2012848C1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для программного управления | 1988 |

|

SU1569804A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

Изобретение относится к автоматике и вычислительной технике и может найти применение в качестве устройства управления системами в реальном масштабе времени. Цель изобретения - расширение функциональных возможностей за счет введения режима ожидания. Устройство содержит входной счетчик 1, дешифратор 2, выходной регистр 3, блок 4 памяти, элемент 5 задержки, счетчик 6 адреса, D-триггер 7 и элемент И 8. Каждая ячейка блока 4 памяти содержит код операции, код временного интервала и бит выбора режима. В устройстве за счет введения.режима ожидания становится возможным организовать обратные связи: от управляемой системы - сигнал готовности. Устройство позволяет управлять системой, требующей широкого диапазона временных интервалов между командами: от микросекунд до часов. При этом дополнительных аппаратурных затрат не требуется. 2 ил. | се сд &0 Од К)

Вмднои сиеюсл pl

П

ПП

| Устройство для программного управления | 1985 |

|

SU1252759A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-11-23—Публикация

1987-03-13—Подача