1чЭ

О) N3 4 СО СП

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействуюпяих ЦВМ.

Целью изобретения является повышение быстродействия.

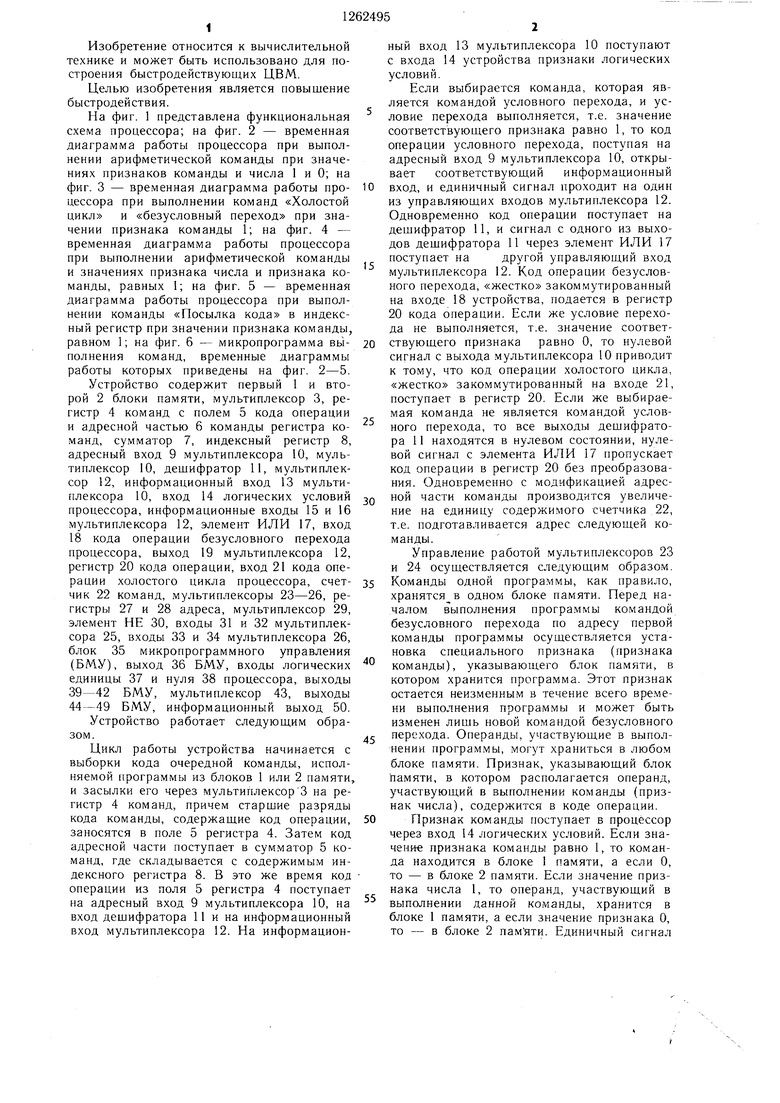

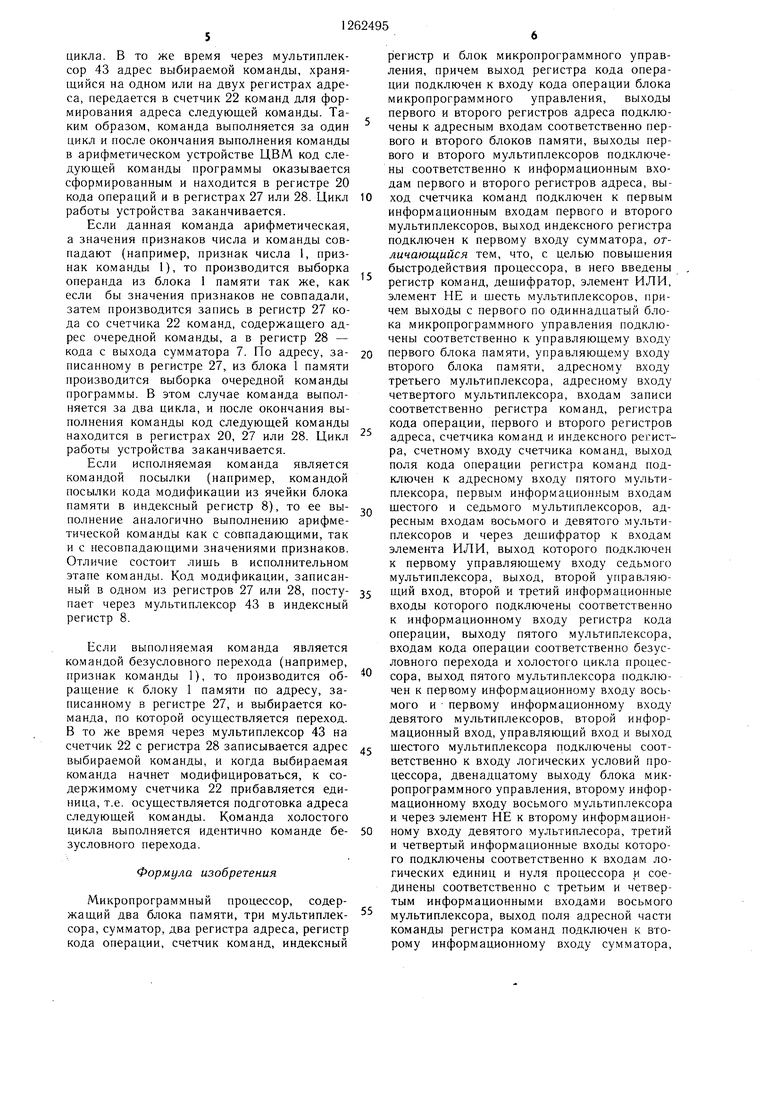

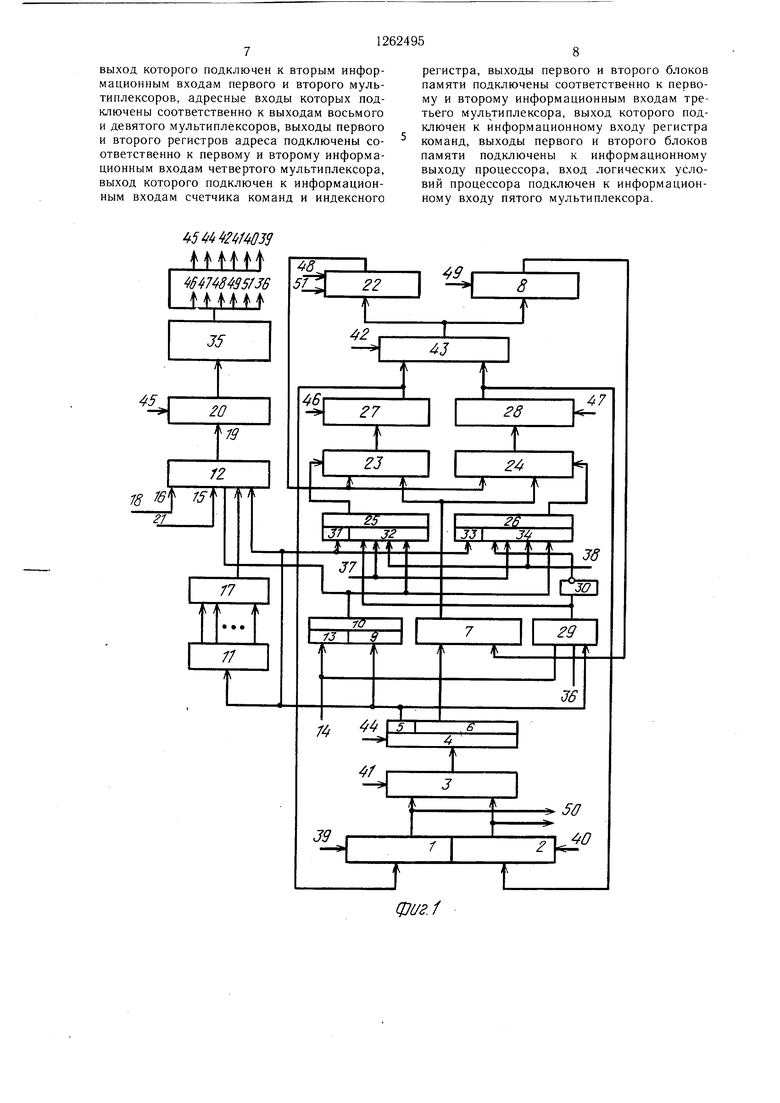

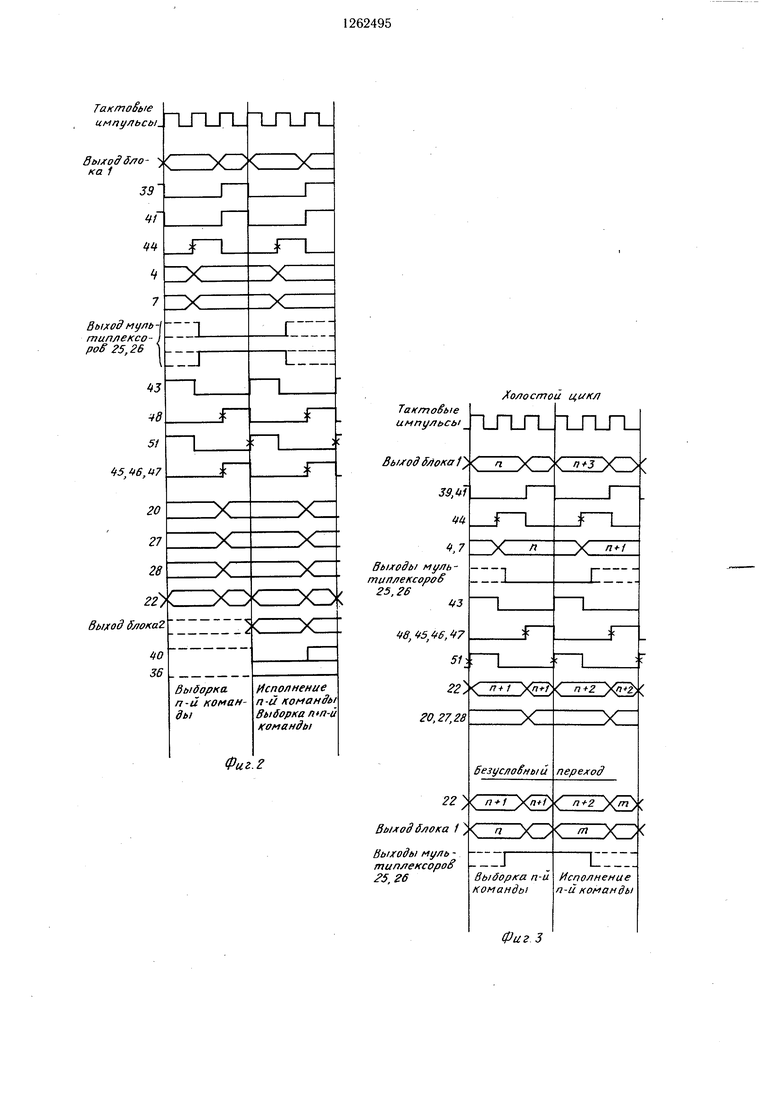

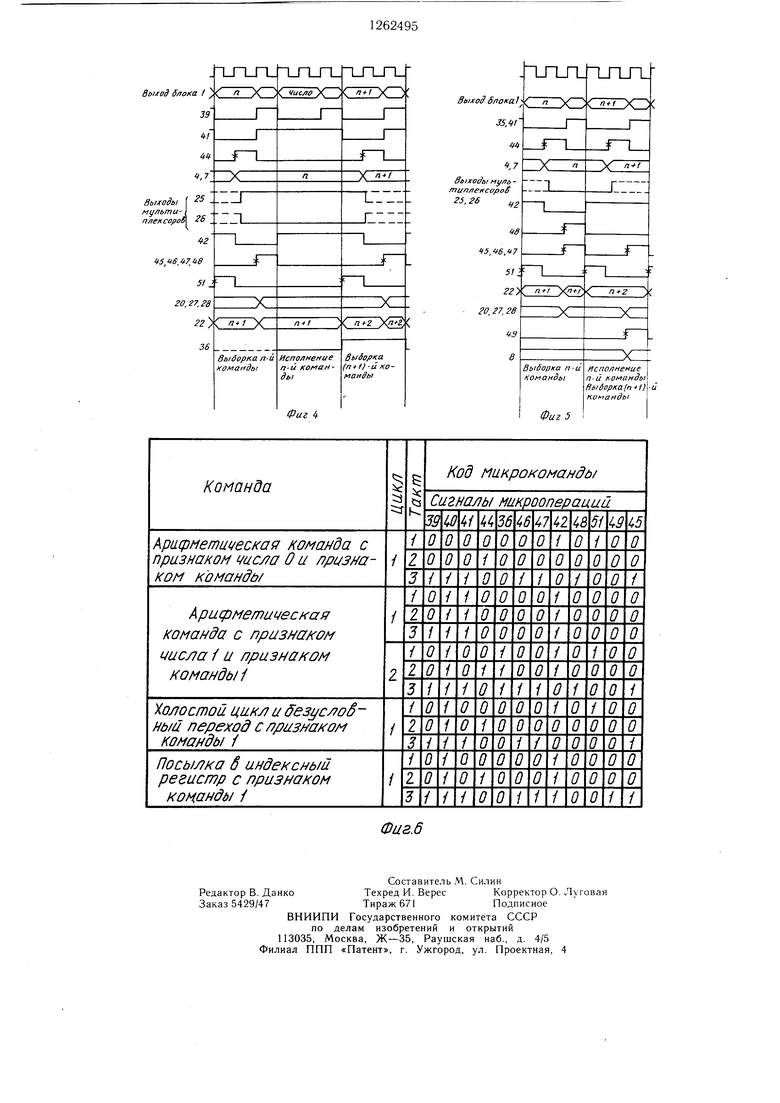

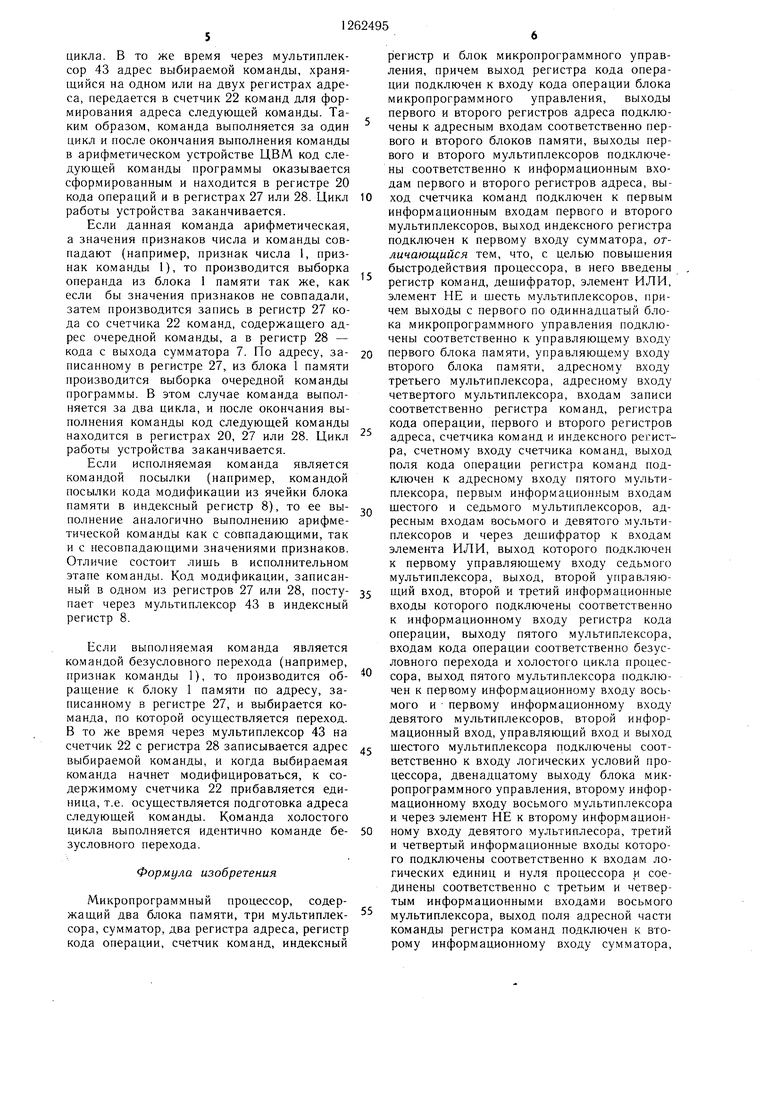

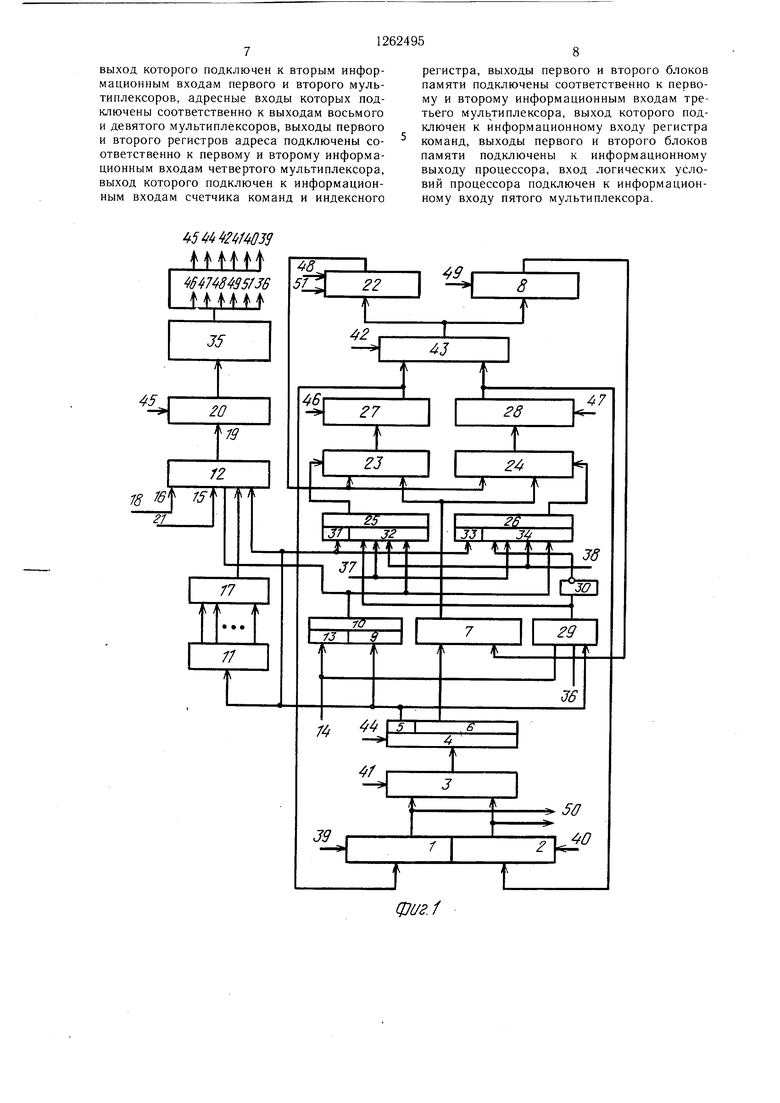

На фиг. 1 представлена функциональная схема процессора; на фиг. 2 - временная диаграмма работы процессора при выполнении арифметической команды при значениях признаков команды и числа 1 и 0; на фиг. 3 - временная диаграмма работы процессора при выполнении команд «Холостой цикл и «безусловный переход при значении признака команды 1; на фиг. 4 - временная диаграмма работы процессора при выполнении арифметической команды и значениях признака числа и признака команды, равных 1; на фиг. 5 - временная диаграмма работы процессора при выполнении команды «Посылка кода в индексный регистр при значении признака команды, равном 1; на фиг. 6 - микропрограмма вь1полнения команд, временные диаграммы работы которых приведены на фиг. 2-5.

Устройство содержит первый 1 и второй 2 блоки памяти, мультиплексор 3, регистр 4 команд с полем 5 кода операции и адресной частью 6 команды регистра команд, сумматор 7, индексный регистр 8, адресный вход 9 мультиплексора 10, мультиплексор 10, дешифратор 11, мультиплексор 12, информационный вход 13 мультиплексора 10, вход 14 логических условий процессора, информационные входы 15 и 16 мультиплексора 12, элемент ИЛИ 17, вход 18 кода операции безусловного перехода процессора, выход 19 мультиплексора 12, регистр 20 кода операции, вход 21 кода операции холостого цикла процессора, счетчик 22 команд, мультиплексоры 23-26, регистры 27 и 28 адреса, мультиплексор 29, элемент НЕ 30, входы 31 и 32 мультиплексора 25, входы 33 и 34 мультиплексора 26, блок 35 микропрограммного управления (БМУ), выход 36 БМУ, входы логических единицы 37 и нуля 38 процессора, выходы 39-42 БМУ, мультиплексор 43, выходы 44-49 БМУ, информационный выход 50.

Устройство работает следуюшим образом.

Цикл работы устройства начинается с выборки кода очередной команды, исполняемой программы из блоков 1 или 2 памяти, и засылки его через мультиплексор3 на регистр 4 команд, причем старшие разряды кода команды, содержашие код операции, заносятся в поле 5 регистра 4. Затем код адресной части поступает в сумматор 5 команд, где складывается с содержимым индексного регистра 8. В это же время код операции из поля 5 регистра 4 поступает на адресный вход 9 мультиплексора 10, на вход дешифратора 11 и на информационный вход мультиплексора 12. На информационный вход 13 мультиплексора 10 поступают с входа 14 устройства признаки логических условий.

Если выбирается команда, которая является командой условного перехода, и условие перехода выполняется, т.е. значение соответствующего признака равно 1, то код операции условного перехода, поступая на адресный вход 9 мультиплексора 10, открывает соответствующий информационный вход, и единичный сигнал проходит на один из управляющих входов мультип.тексора 12. Одновременно код операции поступает на дешифратор 11, и сигнал с одного из выходов дешифратора 11 через элемент ИЛИ 17 поступает на другой управляющий вход мультиплексора 12. Код операции безусловного перехода, «жестко закоммутированный на входе 18 устройства, подается в регистр 20 кода операции. Если же условие перехода не выполняется, т.е. значение соответствующего признака равно О, то нулевой сигнал с выхода .мультиплексора 10 привод,ит к тому, что код операции холостого цикла, «жестко закоммутированный на входе 21, поступает в регистр 20. Если же выбираемая команда не является командой условного перехода, то все выходы дешифратора 11 находятся в нулевом состоянии, нулевой сигнал с элемента ИЛИ 17 пропускает код операции в регистр 20 без преобразования. Одновременно с модификацией адресной части команды производится увеличение на единицу содержимого счетчика 22, т.е. подготавливается адрес следующей команды.

Управление работой мультиплексоров 23 и 24 осуществляется следующим образом. Команды одной программы, как правило, хранятся в одном блоке памяти. Перед началом выполнения програ.ммы командой безусловного перехода по адресу первой команды программы осуществляется установка специального признака (признака команды), указывающего блок памяти, в котором хранится программа. Этот признак остается неизменным в течение всего времени выполнения программы и может быть изменен лишь новой командой безусловного перехода. Операнды, участвующие в выполнении программы, могут храниться в любом блоке памяти. Признак, указывающий блок памяти, в котором располагается операнд, участвующий в выполнении команды (признак числа), содержится в коде операции.

Признак команды поступает в процессор через вход 14 логических условий. Если значение признака команды равно 1, то команда находится в блоке 1 памяти, а если О, то - в блоке 2 памяти. Если значение признака числа 1, то операнд, участвующий в выполнении данной команды, хранится в блоке 1 памяти, а если значение признака О, то - в блоке 2 памяти. Единичный сигнал С выходом мультиплексоров 25 и 26 открывает второй выход соответствующего мультиплексора 23 или 24, и информация с сумматора 7 проходит иа регистры 27 или 28 адреса. Нулевой сигнал с выходов мультиплексоров 25 или 26 открывает первый вход соответствующего мультиплексора 23 или 24, и информация со счетчика 22 команд проходит на регистры 27 или 28. Если выбирается команда арифметическая или команда посылки и значения признаков числа и команды не совпадают (например, признак команды 1, а признак числа 0), то через мультиплексор 29 нулевое значение признака числа подается на первый информационный вход мультиплексора 25, а инверсное значение признака числа с выхода элемента НЕ 30 подается на первый из информационных входов 34 мультиплексора 26. Код арифметической операции, поступая на адресные входы 32 и 33 мультиплексоров 25 и 26, открывает первые из информационных входов 31 и 34, и с выхода мультиплексора 25 поступает нулевой сигнал, а с выхода мультиплексора 26 - единичный сигнал. Открывается первый вход мультиплексора 23 и на регистр 27 принимается код со счетчика 22 команд, содержащий адрес следующей команды программы. Одновременно открывается второй вход мультиплексора 24 и на регистр 28 принимается модифицированный адрес операнда с сумматора 7. Если значение признаков числа и команды совпадает (например, признак числа О, а признак команды тоже 0), то команда выполняется за два цикла, так как необходимо обратиться за операндом и за командой к одному и тому же блоку памяти. В первом цикле производится выборка операнда, во втором - выборка следующей команды. В этом случае блок 35 микропрограммного управления выдает единичный сигнал на управляющий вход 36 мультиплексора 29, указывающий на то, что выполнение команды продолжается во втором цикле, при этом мультиплексор 29 пропускает инверсное значение признака команды на первые информационные входы мультиплексоров 25 и 26. Поскольку на адресные входы этих мультиплексоров подается код операции той же арифметической команды, то единичный сигнал проходит на выход мультиплексора 25, а нулевой - на выход мультиплексора 26 и затем на управляющие входы мультиплексоров 23 и 24, открывая соответственно второй вход мультиплексора 24 и первый вход мультиплексора 25. На вход регистра 28 проходит содержимое счетчика 22, а на вход регистра 27 - содержимое сумматора 7. Если выбираемая команда является командой безусловного перехода, то после поступления кода операции команды на адресные входы мультиплексоров 25 и 26 открываются вторые информационные входы мультиплексоров 25 и 26, и «жестко закоммутированные единичные сигналы с входа 37 проходят на выходы мультиплексоров 25 и 26, открывая вторые входы мультиплексоров 23 и 24. На регистры 27 и 28 поступает модифицированный адрес перехода с сумматора 7. Если выбираемая команда является командой холостого цикла, то с входа 38 «жестко закоммутированные нулевые сигналы поступают через третьи из информационных входов 32 и 34 мультиплексоров 25 и 26 и открывают первые входы мультиплексоров 23 и 24. Информация со счетчика 22, содержащего адрес следующей команды, подается на регистры 27 и 28. ЕС.ПИ выбираемая команда является командой условного перехода и условие перехода выполняется, то единичный сигнал с выхода мультиплексора 10 поступает на четвертые из информационных входов 32 и 34 мультиплексоров 25 и 26, а через них на выходы мультиплексоров 25 и 26, и далее процессор работает так же, как и для команды безусловного перехода. Если условие не выполняется, то на четвертые из информационных входов 32 и 34 поступают нулевые сигналы с выхода мультиплексора 10 и процессор далее работает так же, как и для команды холостого цикла. После окончания модификации в регистр 20 кода операции принимается кОлТ, операции с выхода элемента ИЛИ 17, а в регистры 27 и 28 адреса - коды с выходов мультиплексоров 23 и 24. Заканчивается цикл выборки команды и начинается цикл выполнения. Код операции с регистра 20 поступает в блок 35 микропрограммного управления, где начинает выполняться микропрограмма данной команды. Блок 35 выдает следующие сигналы микроопераций, управляющие выполнением команды в процессоре: сигналы 39 и 40 чтения соответственно блоков 1 и 2 памяти, сигналы 41 и 42 управления соответственно мультиплексорами 3 и 43, сигналы 44-49 записи информации соответтвенно в регистры команд 4, кода операции 20, адреса 27 и 28, счетчик 22 команд, инденсный регистр 8, сигнал 51 увеличения содержимого счетчика 22 команд на единицу. Если данная команда арифметическая и значения признаков числа и команды не совпадают (например, признак числа О, а признак команды 1), то по адресу, записанному в регистре 28 адреса, из блока 2 памяти, выбирается операнд и через выход 50 процессора подается в арифметическое устройство ЦВМ, а по адресу, записанному в регистре 27, из блока 1 памяти выбирается очередная команда программы и подается через мультиплексор 3 в регистр 4, т.е. фактически выполняется команда холостого цикла. В то же время через мультиплексор 43 адрес выбираемой команды, хранящийся на одном или на двух регистрах адреса, передается в счетчик 22 команд для формирования адреса следующей команды. Таким образом, команда выполняется за один цикл и после окончания выполнения команды в арифметическом устройстве ЦВМ код следующей команды программы оказывается сформированным и находится в регистре 20 кода операций и в регистрах 27 или 28. Цикл работы устройства заканчивается. Если данная команда арифметическая, а значения признаков числа и команды совпадают (например, признак числа 1, признак команды 1), то производится выборка операнда из блока 1 памяти так же, как если бы значения признаков не совпадали, затем производится запись в регистр 27 кода со счетчика 22 команд, содержащего адрес очередной команды, а в регистр 28 - кода с выхода сумматора 7. По адресу, записанному в регистре 27, из блока 1 памяти производится выборка очередной команды программы. В этом случае команда выполняется за два цикла, и носле окончания выполнения команды код следующей команды ,-,, , находится в регистрах 20, 27 или 28. Цикл работы устройства заканчивается. Если исполняемая команда является командой посылки (например, командой посылки кода модификации из ячейки блока памяти в индексный регистр 8), то ее выполнение аналогично выполнению арифметической команды как с совпадающими, так и с несовпадающими значениями признаков. Отличие состоит лищь в исполнительном этане команды. Код модификации, записанный в одном из регистров 27 или 28, поступает через мультиплексор 43 в индексный регистр 8. Если выполняемая команда является командой безусловного перехода (например, признак команды 1), то производится обращение к блоку 1 памяти но адресу, записанному в регистре 27, и выбирается команда, по которой осуществляется переход. В то же время через мультиплексор 43 на счетчик 22 с регистра 28 записывается адрес выбираемой команды, и когда выбираемая команда начнет модифицироваться, к содержимому счетчика 22 прибавляется единица, т.е. осуществляется подготовка адреса следующей команды. Команда холостого цикла выполняется идентично команде безусловного перехода. Формула изобретения Микропрограммный процессор, содержащий два блока памяти, три мультинлексора, сумматор, два регистра адреса, регистр кода операции, счетчик команд, индексный регистр и блок микропрограммного управления, причем выход регистра кода операции подключен к входу кода операции блока микропрограммного управления, выходы первого и второго регистров адреса подключены к адресным входам соответственно первого и второго блоков памяти, выходы первого и второго мультиплексоров подключены соответственно к информационным входам первого и второго регистров адреса, выход счетчика команд подключен к первым информационным входам первого и второго мультиплексоров, выход индексного регистра подключен к первому входу сумматора, отличающийся тем, что, с целью повышения быстродействия процессора, в него введены регистр команд, дешифратор, элемент ИЛИ, элемент НЕ и шесть мультиплексоров, причем выходы с первого по одиннадцатый блока микропрограммного управления подключены соответственно к управляющему входу первого блока памяти, управляющему входу второго блока памяти, адресному входу третьего мультиплексора, адресному входу четвертого мультиплексора, входам записи соответственно регистра команд, регистра кода операции, первого и второго регистров .,- , ц, -ггг адреса, счетчика команд и индексного регистра, счетному входу счетчика команд, выход поля кода операции регистра команд подключен к адресному входу пятого мультиплексора, первым информационным входам щестого и седьмого мультиплексоров, адресным входам восьмого и девятого мультиплексоров и через дешифратор к входам элемента ИЛИ, выход которого подключен к первому управляющему входу седь.мого мультиплексора, выход, второй управляющий вход, второй и третий информационные входы которого подключены соответственно к информационному входу регистра кода операции, выходу пятого .мультиплексора, входам кода операции соответственно безусловного перехода и холостого цикла процессора, выход пятого мультиплексора подключен к первому информационному входу восьмого и первому информационному входу девятого мультиплексоров, второй информационный вход, управляющий вход и выход шестого мультиплексора подключены соответственно к входу логических условий процессора, двенадцатому выходу блока микропрограммного управления, второ.му информационному входу восьмого мультиплексора и через элемент НЕ к второму информационному входу девятого мультиплесора, третий и четвертый информационные входы которого подключены соответственно к входам логических единиц и нуля процессора и соединены соответственно с третьим и четвертым информационными входами восьмого мультиплексора, выход поля адресной части команды регистра команд подключен к второму информационному входу сумматора.

выход которого подключен к вторым информационным входам первого и второго мультиплексоров, адресные входы которых подключены соответственно к выходам восьмого и девятого мультиплексоров, выходы первого и второго регистров адреса подключены соответственно к первому и второму информационным входам четвертого мультиплексора, выход которого подключен к информационным входам счетчика команд и индексного

регистра, выходы первого и второго блоков памяти подключены соответственно к первому и второму информационным входам третьего мультиплексора, выход которого подключен к информационному входу регистра команд, выходы первого и второго блоков памяти подключены к информационному выходу процессора, вход логических условий процессора подключен к информационному входу пятого мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР | 1990 |

|

SU1826787A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для формирования адресов процессора быстрого преобразования Фурье | 1989 |

|

SU1691853A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих цифровых вычислительных машин. Целью изобретения является повышение быстродействия процессора. Процессор содержит два блока памяти, девять мультиплексоров, сумматор, два регистра адреса, регистр кода операции, счетчик команд, индексный регистр, блок микропрограммного управления, регистр команд, дешифратор, элемент ИЛИ и элемент НЕ. Поставленная цель достигается за счет совмешения операций модификации адресной части команды и анализа кода операции. 6 ил.

фиг.1

1J

T

t5,tt6,

20 27 28

22У

Выход блока2

to

36

(Исполнение п-й конанвы Выборка ntfj-u команды

/о/тоетой цикл

ВыкоЗ блока. SS.ifl

BbtXOl bl Му/Jfr гпиллексороё2S.26

| Микропрограммное устройство управления | 1981 |

|

SU1003084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Майоров С | |||

| А., Новиков Г | |||

| И | |||

| Структура цифровых вычислительных машин | |||

| Кинематографический аппарат | 1923 |

|

SU1970A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1984-10-09—Подача