Изобретение относится к вычислительной технике и может быть использовано в устройствах управле.ния вычислительных машин..,

Известно микропрограммное устройство управления, содержащее блоки памяти, регистры адреса, коммутатор, триггеры, .. элементы И, элементы ИЛИ. tl.

Однако это устройство обладает избытком оборудования.

Известно микропрограммное устройство управления, содержащее блоки памяти, регистр адреса, элемент ИЛИ 2.

Недостаток известного устройства- низкая надежность работы.

Цель изобретения - повышение надежности работы устройства.

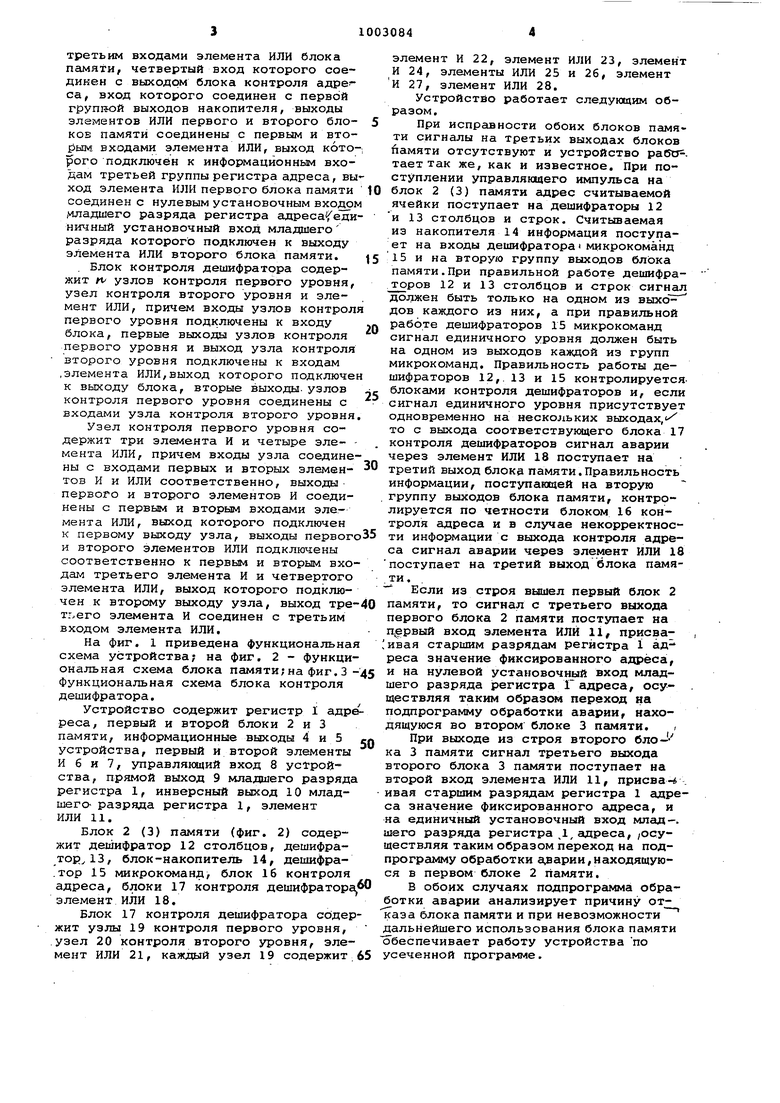

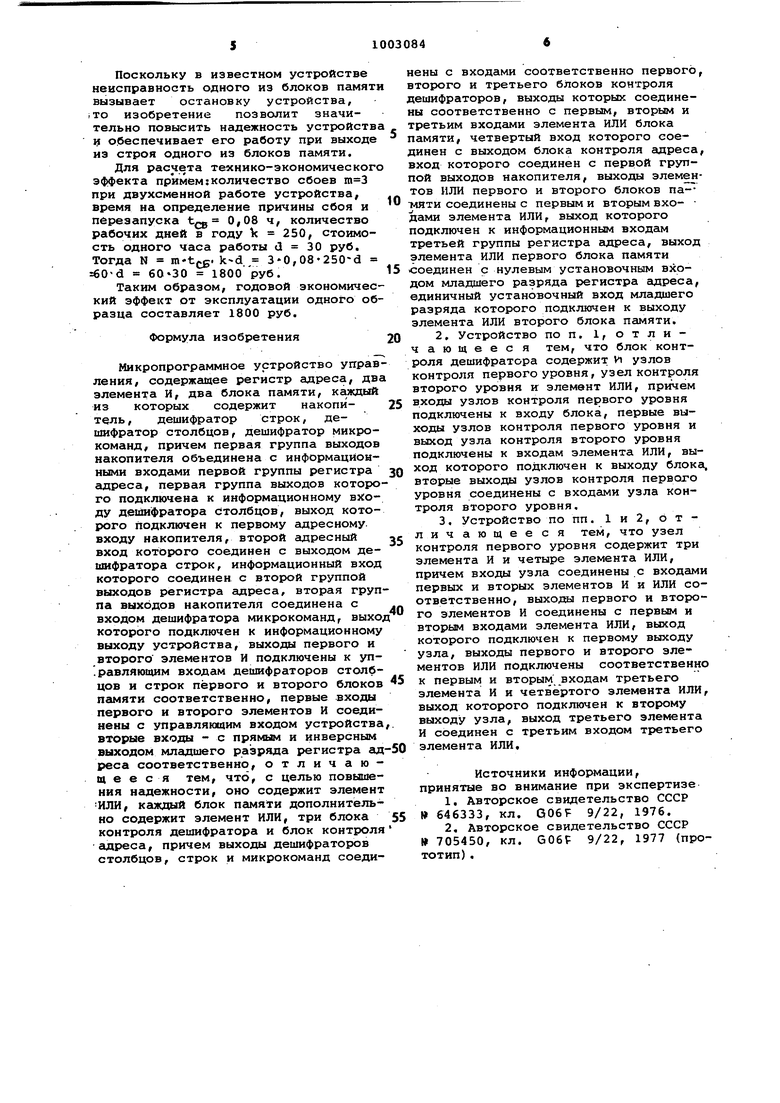

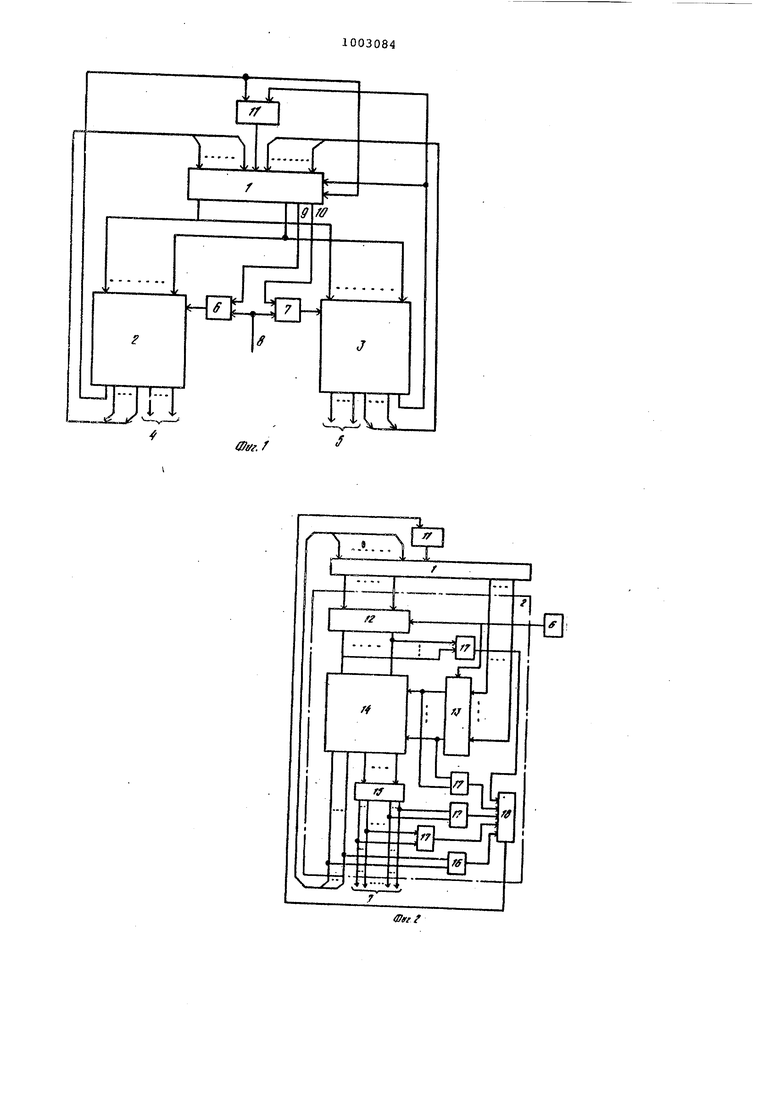

Поставленная цель достигается тем, что микропрограммное устройство управления, содержащее регистр адреса, два элемента И, два блока.памяти, каждый иэ которых содержит накопитель, деши фратор строк, дешифратор, столбцов, дешифратор микрокоманд, причем первая группа выходов накопителя соединена с информационными входами первой группы регистра адреса, первая группа выходов которого подключена к информационному входу дешифратора столбцов, выход которого подключен к первому адресному входу накопителя, второй адресный вход которого соединен с выходом дешифратора строк, информационный вход которого соединен с второй группой выходов регистра адреса, вторая группа выходов накопителя соединена с входом дешифратора микрокоманд, выход которого подключен к информационному выходу устройства, выходы первого и второго элементов И подключены к управлянвдим входам дешифраторов столбцов и строк первого и второго блоков памяти соответйтвенно, первые входал первого и второго элементов И соединены с управляющим входом устройства, вторые входы - с прямым и инверсным выходом младшего разряда регистра адреса соответственно, дополнительно содержит элемент ИЛИ, каждый блок памяти дополнительно содержит -элемент ИЛИ, три блока контроля дешифратора и блок контроля адреса, причем выходы дешифраторов столбцов, строк и микрокоманд соединены с входс1ми соответственно первого второго и третьего блоков контроля дешифраторов, выходы которых соединены соответственно с первытл, вторым и третьим входами элемента ИЛИ блока памяти, четвертый вход которого соединен с выходом блока контроля , вход которого соединен с первой групн-ой выходов накопителя, выходы элементов ИЛИ первого и второго блоКОЕ памяти соединены с первым и вторым входами элемента ИЛИ, выход которого подключен к информационным входам третьей группы регистра адреса, вы ход элемента ИЛИ первого блока памяти соединен с нулевым установочным входом / 1ладшего разряда регистра адреса;еди ничный установочный вход младшего разряда которого подключен к выходу элемента ИЛИ второго блока памяти. Блок контроля дешифратора содержит /f узлов контроля первого уровня, узел контроля второго уровня и элемент ИЛИ, причем входы узлов контрол первого уровня подключены к входу блока, первые выходы узлов контроля первого уровня и выход узла контроля второго уровня подключены к входам .элемента ИЛИ,выход которого подключе к выходу блока, вторые выходы, узлов контроля первого уровня соединены с входами узла контроля второго уровня Узел контроля первого уровня содержит три элемента И и четыре элемента ИЛИ, причем входы узла соедине ны с входами первых и вторых элементов И и ИЛИ соответственно, выходы первого и второго элементов И соединены с первым и вторым входами элемента ИЛИ, выход которого подключен к первому выходу узла, выходы первог и второго элементов ИЛИ подключены соответственно к первым и вторым вхо дам третьего элемента И и четвертого элемента ИЛИ, выход которого подключен к второму выходу узла, выход тре т-.его элемента И соединен с третьим входом элемента ИЛИ, На фиг, 1 приведена функциональна схема устройства; на фиг, 2 - функци ональная схема блока памяти;на фиг. 3 функциональная схема блока контроля дешифратора. Устройство содержит регистр I адр реса, первый и второй блоки 2 и 3 памяти, информационные выходы 4 и 5 устройства, первый и второй элементы И 6 и 7, управляквдий вход 8 устрой ства, прямой выход 9 младшего разряда регистра 1, инверсный выход 10 младшего- разряда регистра 1, элемент ИЛИ 11, Блок 2 (3) памяти (фиг, 2) содержит дешифратор 12 столбцов, дешифратор 13, блок-накопитель 14, дешифра.тор 15 микроксжанд, блок 16 контроля адреса, блоки 17 контроля дешифратора элемент ИЛИ 18, Блок 17 контроля дешифратора са1дер жит уэлы 19 контроля первого уровня, узел 20 контроля второго уровня, элемент ИЛИ 21, каждый узел 19 содержит элемент И 22, элемент ИЛИ 23, элемент И 24, элементы ИЛИ 25 и 26, элемент и 27, элемент ИЛИ 28, Устройство работает следующим образом. При исправности обоих блоков памяти сигналы на третьих выходах блоков Аамяти отсутствуют и устройство раба. тает так же, как и известное. При поступлении управляющего импульса на блок 2 (3) памяти адрес считываемой ячейки поступает на дешифраторы 12 и 13 столбцов и строк. Считываемая из накопителя 14 информация поступает на входы дешифратора микрокоманд 15 и на вторую группу выходов блока памяти.При правильной работе дешифра трров 12 и 13 столбцов и строк сигнал должен быть только на одном из выхо дов каждого из них, а при правильной работе дешифраторов 15 микрокоманд сигнал единичного уровня должен быть на одном из выходов каждой из групп микрокоманд. Правильность работы дешифраторов 12,. 13 и 15 контролируетсяблоками контроля дешифраторов и, если сигнал единичного уровня присутствует одновременно на нескольких выходах,/ то с выхода соответствующего блока 17 контроля дешифраторов сигнал аварии через элемент ИЛИ 18 поступает на третий выход блока памяти.Правильность информации, поступающей на вторую группу выходов блока памяти, контролируется по четности блоком 16 контроля адреса и в случае некорректности информации с выхода контроля адреса сигнал аварии через элемент ИЛИ 18 поступает на третий выход блока памяти, . Если из строя вышел первый блок 2 памяти, то сигнал с третьего выхода первого блока 2 памяти поступает на п,ервый вход элемента ИЛИ 11, присваивая старшим разрядам регистра 1 адреса значение фиксированного адреса, и на нулевой установочный вход младшего разряда регистра Г адреса, осуществляя таким образом переход на подпрограмму обработки аварии, находящуюся во втором блоке 3 памяти, / При выходе из строя второго бло-ка 3 памяти сигнал третьего выхода второго блока 3 памяти поступает на второй вход элемента ИЛИ 11, присва- ивая старшим разрядам регистра 1 адреса значение фиксированного адреса, и на единичный установочный вход млад-, шего разряда регистра ,1,адреса, /осуществляя таким образом переход на подпрограмму обработки аварии,находящуюся в первом блоке 2 памяти, В обоих случаях подпрограмма обработки аварии анализирует причину откаэа блока памяти и при невозможности дальнейшего использования блока памяти обеспечивает работу устройства по усеченной программе. Поскольку в известном устройстве неисправность одного из блоков памят вызывает остановку устройства, iTO изобретение позволит значительно повысить надежность устройств и обеспечивает его работу при выходе из строя одного из блоков памяти. Для расчета технико-экономического эффекта примем количество сбоев при двухсменной работе устройства, время на определение причины сбоя и Перезапуска t 0,08 ч, количество рабочих дней в году Vc 250, стоимость одного часа работы 3 30 руб. Тогда N m-t. k-d 3-0,08250-d бОЗО 1800 руб. Таким образом, годовой экономичес кий эффект от эксплуатации одного образца составляет 1800 руб. Формула изобретения Микропрограммное устройство управ ления, содержащее регистр адреса, дв элемента И, два блока памяти, кгикдый из которых содержит накопитель, дешифратор строк, дешифратор столбцов, дешифратор микрокоманд, причем первая группа выходов накопителя объединена с информационными входами первой группы регистра адреса, первая группа выходов которо го подключена к информационному входу дешифратора столбцов, выход которого подключен к первому адресному входу накопителя, второй адресный вход которого соединен с выходом дешифратора строк, информационный вход которого соединен с вторюй группой выходов регистра адреса, вторая груп па выходов накопителя соединена с входом дешифратора микрокоманд, выхо которого подключен к информационному выходу устройства, выходы первого и второго элементов И подключены к уп равляющим входам дешифраторов столбцов и строк первого и второго блоков памяти соответственно, первые входы первого и второго элементов И соединены с управляющим входом устройства вторые входы - с прямым и инверсным выходом младшего разряда регистра ёщ реса соответственно, отличаюц е е с я тем, что, с целью повышения надежности, оно содержит элемент ИЛИ, каждый блок дополнительно содержит элемент ИЛИ, три блока контроля дешифратора и блок контроля адреса, причем выходы дешифраторов столбцов, строк и микрокоманд соединены с входами соответственно первого, второго и третьего блоков контроля дешифраторов, выходы которых соединены соответственно с первым, вторым и третьим входами элемента ИЛИ блока памяти, четвертый вход которого соединен с выходом блока контроля адреса, вход которого соединен с первой группой выходов накопителя, выходы элементов ИЛИ первого и второго блоков па- -увпк соединены с первым и вторым вхо- дами элемента ИЛИ, выход которого подключен к информационным входам третьей группы регистра адреса, выход элемента ИЛИ первого блока памяти -соединен с нулевым установочным входом младшего разряда регистра адреса, единичный установочный вход младшего разряда которого подключен к выходу элемента ИЛИ второго блока памяти. 2.Устройство по п. 1, отличающееся тем, что блок контроля дешифратора содержит И узлов контроля первого уровня, узел контроля второго уровня и элемент ИЛИ, причем входы узлов контроля первого уровня подключены к входу блока, первые выходы узлов контроля первого уровня и выход узла контроля второго уровня подключены к входам элемента ИЛИ, выход которого подключен к выходу блоке1, вторые выходы узлов контроля первого уровня соединены с входами узла контроля второго уровня, 3.Устройство по пп. 1 и 2, о т личающееся тем, что узел контроля первого уровня содержит три элемента И и четыре элемента ИЛИ, причем входы узла соединены с входами первых и вторых элементов И и ИЛИ соответственно, выходы первого и второго элементов И соединены с первым и вторым входами элемента ИЛИ, выход которого подключен к первому выходу узла, выходы первого и второго элементов ИЛИ подключены соответственно к первым и вторым входам третьего элемента И и четвертого элемента ИЛИ, выход которого подключен к второму выходу узла, выход третьего элемента И соединен с третьим входом третьего элемента ИЛИ, Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 646333, кл. G06f 9/22, 1976. 2.Авторское свидетельство СССР № 705450, кл. G06F 9/22, 1977 (прототип) ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Устройство для медианной фильтрации двумерных массивов | 1987 |

|

SU1524067A1 |

| Имитатор канала | 1987 |

|

SU1425675A2 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

J

rilT

Ty

...(f -V

(ffwJ

Авторы

Даты

1983-03-07—Публикация

1981-04-08—Подача