|С

05 1C

ел

Изобретение относится к вычислительной технике и, в частности, к устройствам автоматического синтеза тестов для контроля работоспособности и диагностики неисправностей сложных цифровых объектов, построенных на основе микропроцессоров.

Целью изобретения является повышение бь стродействия устройства.

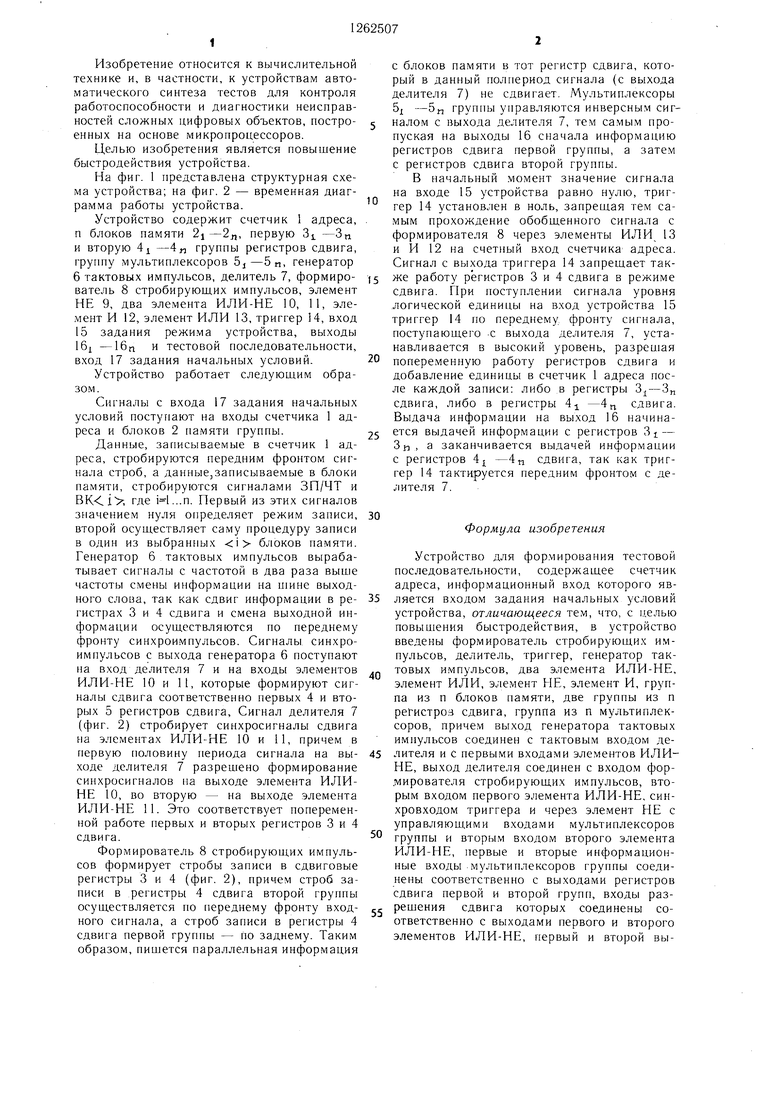

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временная диаграмма работы устройства.

Устройство содержит счетчик 1 адреса, п блоков памяти ,, первую Sj. -3ц и вторую 4i -4л группы регистров сдвига, группу мультиплексоров 5j-5п, генератор б тактовых импульсов, делитель 7, формирователь 8 стробирующих импульсов, элемент НЕ 9, два элемента ИЛИ-НЕ 10, 11, элемент И 12, элемент ИЛИ 13, триггер 14, вход 15 задания режима устройства, выходы 16| -IGri и тестовой последовательности, вход 17 задания начальных условий.

Устройство работает следуюпдим обра30.М.

Сигналы с входа 17 задания начальных условий поступают на входы счетчика 1 адреса и блоков 2 памяти группы.

Данные, записываемые в счетчик 1 адреса, стробируются передним фронтом сигнала строб, а данные,записываемые в блоки памяти, стробируются сигналами ЗП/ЧТ и , где ...n. Нервый из этих сигналов значением нуля определяет режим записи, второй осуш,ествляет саму процедуру записи в один из выбранных i блоков памяти. Генератор 6 тактовых импульсов вырабатывает сигналы с частотой в два раза выше частоты смены информации на шине выходного слова, так как сдвиг информации в регистрах 3 и 4 сдвига и смена выходной информации осуществляются по переднему фронту синхрои.мпульсов. Сигналы синхроимпульсов с выхода генератора 6 поступают на вход делителя 7 и на входы элементов ИЛИ-НЕ 10 и 11, которые формируют сигналь сдвига соответственно первых 4 и вторых 5 регистров сдвига. Сигнал делителя 7 (фиг. 2) стробирует синхросигналы сдвига на элементах ИЛИ-НЕ 10 и 11, причем в первую половину периода сигнала на выходе делителя 7 разрешено формирование синхросигналов па выходе элемента ИЛИНЕ 10, во вторую - на выходе элемента ИЛИ-НЕ 11. Это соответствует попеременной работе первых и вторых регистров 3 и 4 сдвига.

Формирователь 8 стробируюп 1,их импульсов формирует стробы записи в сдвиговые регистры 3 и 4 (фиг. 2), причем строб записи в регистры 4 сдвига второй группы осуществляется по сюреднему фронту входного сигнала, а строб записи в регистры 4 сдвига первой группы - по заднему. Таким образом, пишется параллельная информация

с блоков памяти в тот регистр сдвига, который в данный полпериод сигнала (с выхода делителя 7) не сдвигает. Мультиплексоры 5j( -5п группы управляются инверсным сигнало.м с выхода делителя 7, тем самы.м пропуская на выходы 16 сначала информацию регистров сдвига первой группы, а затем с регистров сдвига второй группы.

В начальный момент значение сигнала на входе 15 устройства равно нулю, триггер 14 установлен в ноль, запрещая тем самым прохождение обобщенного сигнала с формирователя 8 через элементы ИЛИ 13 и И 12 на счетный вход счетчика адреса. Сигнал с выхода триггера 14 запрещает также работу регистров 3 и 4 сдвига в режиме сдвига. При поступлении сигнала уровня .логической единицы на вход устройства 15 триггер 14 по переднему фронту сигнала, поступающего -с выхода делителя 7, устанавливается в высокий уровень, разрешая

попеременную работу регистров сдвига и добавление единицы в счетчик 1 адреса после каждой записи: либо в регистры 3j-3„ сдвига, либо в регистры 4 -4п сдвига. Выдача информации на выход 16 начинается выдачей информации с регистров 3 - Зн, а заканчивается выдачей информации с регистров 4j: -4 сдвига, так как триггер 14 тактируется передним фронтом с делителя 7.

Формула изобретения

Устройство для формирования тестовой последовательности, содержащее счетчик адреса, информационный вход которого является входом задания начальных условий устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены формирователь стробирующих импульсов, делитель, триггер, генератор так.. товых импульсов, два элемента ИЛИ-НЕ, элемент ИЛИ, элемент НЕ, элемент И, группа из п блоков памяти, две группы из п регистро.в сдвига, группа из п мультиплексоров, причем выход генератора тактовых импульсов соединен с тактовым входом де5 лителя и с первыми входами элементов ИЛИНЕ, выход делителя соединен с входом фор.мирователя стробирующих импульсов, вторым входом первого элемента ИЛИ-НЕ, синхровходом триггера и через элемент НЕ с управляющ,ими входами мультиплексоров

группы и вторым входом второго элемента

ИЛИ-НЕ, первые и вторые информационные входы мультиплексоров группы соединены соответственно с выходами регистров сдвига первой и второй групп, входы разJ решения сдвига которых соединены соответственно с выходами первого и второго элементов ИЛИ-НЕ, первый и второй выходы формирователя стробирующих импульсов соединены соответственно с входами разрешения записи регистров сдвига первой и второй групп и первым и вторым входами элемента ИЛИ, выход которого подключен к первому входу элемента И, второй вход которого объединен с входами запрета записи регистров сдвига первой и второй групп и подключен к прямому выходу триггера, информационный вход которого соединен с входом задания режима устройства.

информационные входы блоков памяти группы соединены с входом задания начальных условий устройства, выходы блоков памяти группы подключены к информационным входам регистров сдвига первой и второй групп, счетный вход счетчика адреса соединен с выходом элемента И, выход счетчика адреса соединен с адресными входами блоков памяти группы, выходы мультиплексоров группы являются выходами тестовой последовательности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНОЕ УСТРОЙСТВО КОДИРОВАНИЯ СИГНАЛОВ | 1993 |

|

RU2037270C1 |

| Многоканальный логический анализатор | 1984 |

|

SU1359779A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

| Устройство для функционального контроля интегральных схем | 1988 |

|

SU1737465A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство асинхронного сопряжения дискретного сигнала с синхронным цифровым трактом | 1987 |

|

SU1610600A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для формирования и передачи сообщения | 1990 |

|

SU1778767A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Изобретение относится к вычислительной технике, в частности к устройствам автоматического синтеза тестов для контроля работоспособности и диагностики неисправностей цифровых объектов, построенных на основе микропроцессоров. Целью изобретения является повышение быстродействия устройства. Цель достигается введением в устройство генератора импульсов, делителя, триггера, элемента И, формирователя стробирующих импульсов, элемента ИЛИ-НЕ, элемента ИЛИ, элемента НЕ, п блоков памяти, двух групп из п регистров сдвига, группы из п мультиплексоров. Выдача информации на выходную шину начинается с регистров первой группы, а заканчивается выдачей информации с регистров второй группы. 2 ил.

/7 С 5л 6 С5л.7 с 5л.Югигшлггитгиш lJlllЛJlJlJглJlЛJггLГLЛJlЛJlJlJ Jl гпJlJlJlJlJlJirLTLTLrLЛЛЛР п п п п п п -ПЛГ

| Электронная промышленность | |||

| М.: Мир, 1977 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-04—Подача