pa частоты является группой информационных входов блока временного контроля.

2. AnaJSHsaTop по п.1, о т л и - чающимися тем, что блак запуска содержит каналы управления началом записи и концом записи и триггер разрешения записи, каждый из каналов управления содержит регистр маски, группой выходов соединенньй с первой группой входов первого узла элементов И-НЕ, группа выходов которого подключена к первой группе входов узла сравнения, вторая группа входов которого соединена с группой выходов регистра начала записи и регистра конца записи соответственно, группа выходов узла сравнения подключена к группе входов второго узла элементов И-НЕ, группа выходов которого соединена с группой входов элементов Ш1И-НЕ, вторая группа информационных входов блока запуска соединена с группами входов регистров начала записи и конца записи и регистров маски начала записи и конца записи каналов управления началом и концом записи соответственно, первая группа информационных входов блока запуска соединена с второй группой входов первого узла элементов И-НЕ каждого из каналов, выходы элементов ИЛИ-НЕ являются соответствующими входами триггера.

3. Анализатор по п.1, отличающийся тем, что блок управления содержит узел захвата сигналов, узел выбора вида работ, узел управления началом и концом записи, узел переполнения памяти, узел выбор режима записи, первый вход которого . является синхровходом блока управления, а второй вход - входом раз зеше- ния блока управления и соединен с вторым входом узла захвата сигналов, первый вход которого соединен с вторым выходом узла выбора режима записи и четвертым входом узла выбора вида работ, первая группа выходов кото рого соединена с первыми группами выходов узла выбора режима записи, узла управления Началом и концом записи, узла переполнения памяти и является группой разрешающих выходов блока управления, второй выход узла выбора вида работ является выходом

выбора режима блока управления, четвертая группа входов узла выбора режима записи соединена с вторыми группами входов узла выбора вида работ, узла управления началом и концом записи, узла переполнения памяти, третьим входом узла захвата сигналов и является группой входов задания режима блока управления, третий вход узла управления началом и концом записи соединен с четвертым выходом узла выбора вида работ, первый вход которого соединен с вторым выходом узла переполнения памяти, а третий вход узла выбора режима записи связан с вторым выходом узлл управления началом и концом записи, третий выход которого соединен с третьим входом узла выбора вида работ, четвертый вход узла захвата сигналов соединен с .третьим выходом узла выбора режима записи, четвертый выход которого является вьпсодом управления режимом записи блока управления, первый вход узла управления началом и концом записи является стробирующим входом блока управления, а третий вьтод узла выбора вида работ соединен с выходом узла захвата сигналов и является выходом управления блоком памяти блока управления, первый вход узла переполнения памяти является входом выбора режима блока управления, узел выбора режима записи содержит три триггера и три элемента И, причем информационные и синхровходы первого и второго триггеров образуют четвертый вход узла, единичный и нулевой выходы пер- вого триггера образуют четвертый выход узла, единичный выход третьего триггера соединен с первыми входами первого и второго элементов И и явля- ется первым выходом узла, единичный выход второго триггера соединен с вторым входом первого элемента И и является третьим выходом блока, третий вход первого элемента И является вторым входом блока, нулевой выход второго триггера соединен с вторым входом второго элемента И, третий вход которого является первым входом узла, выходы первого и второго элементов И соединены с первым и вторым входами третьего элемента И, выход которого является вторым выхо;: ом блока.

Изобретение относится к вычислительной технике, а именно к устройствам контроля и диагностики ЭВМ.

Целью изобретения является расширение функциональных возможностей анализатора за счет обеспечения режима быстрого асинхронного .анализа.

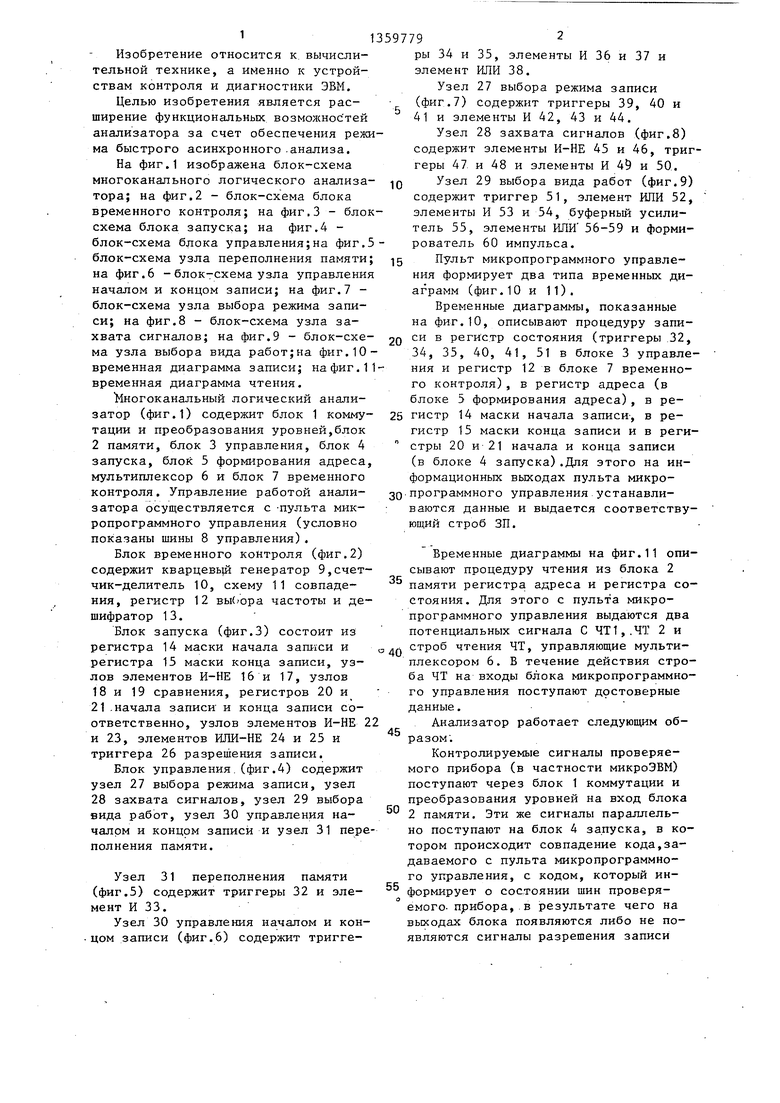

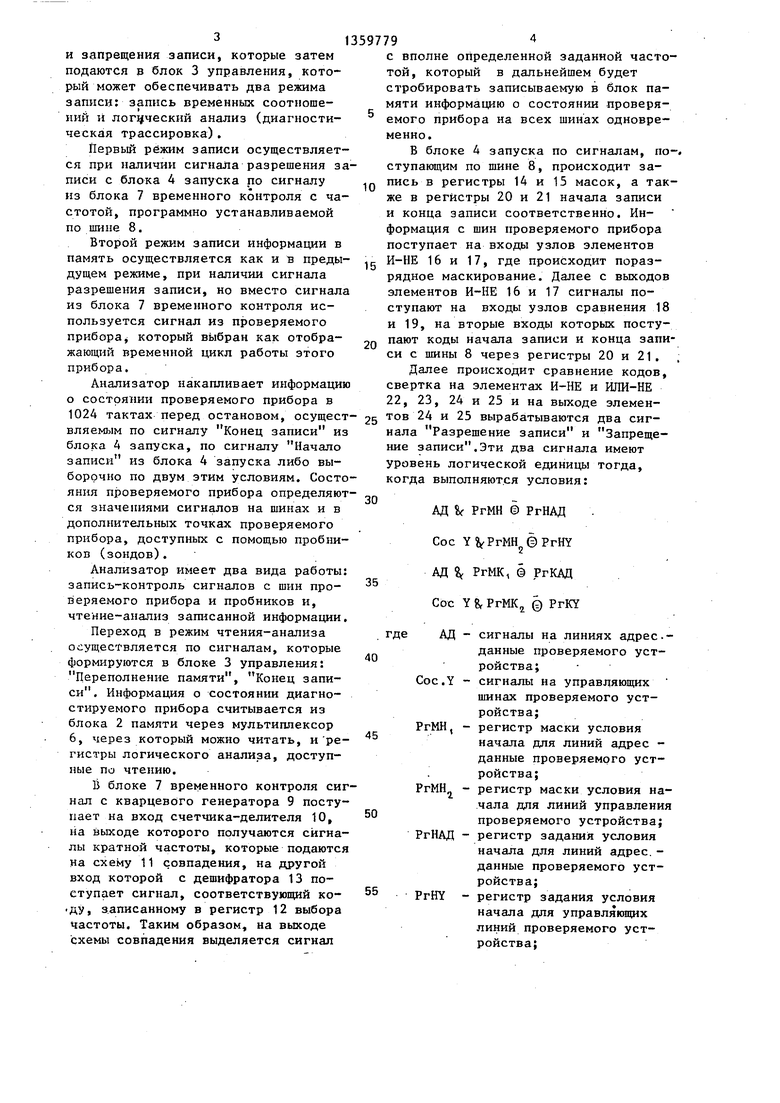

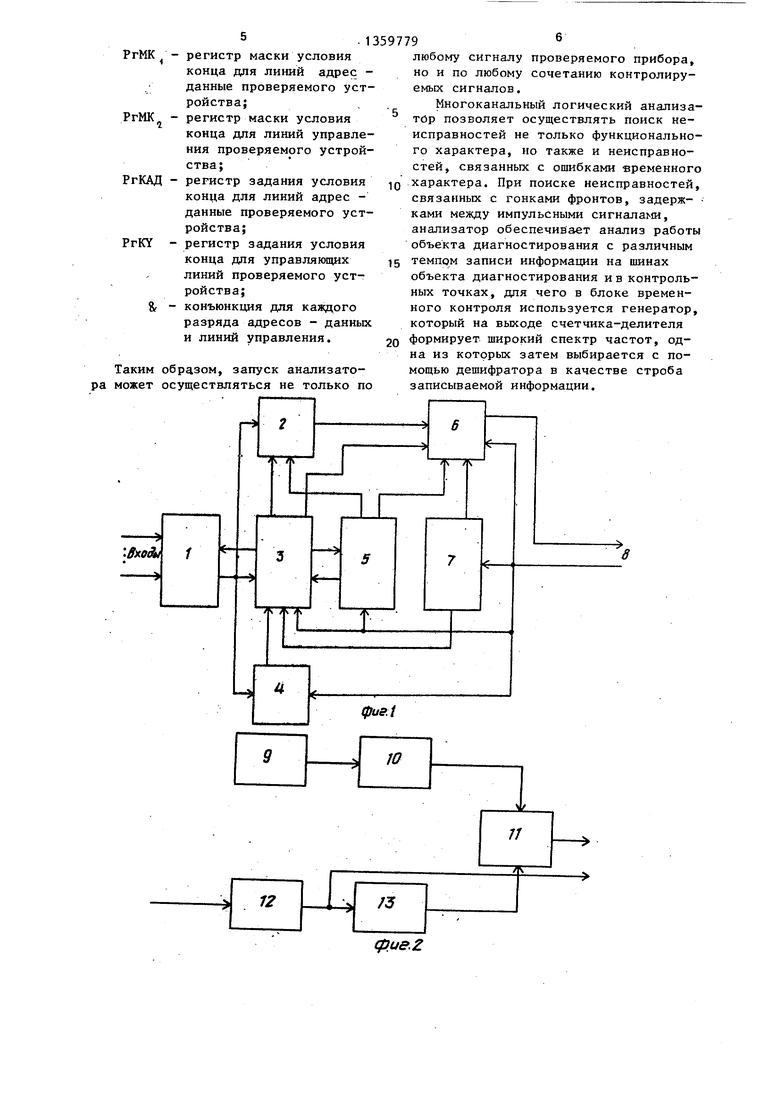

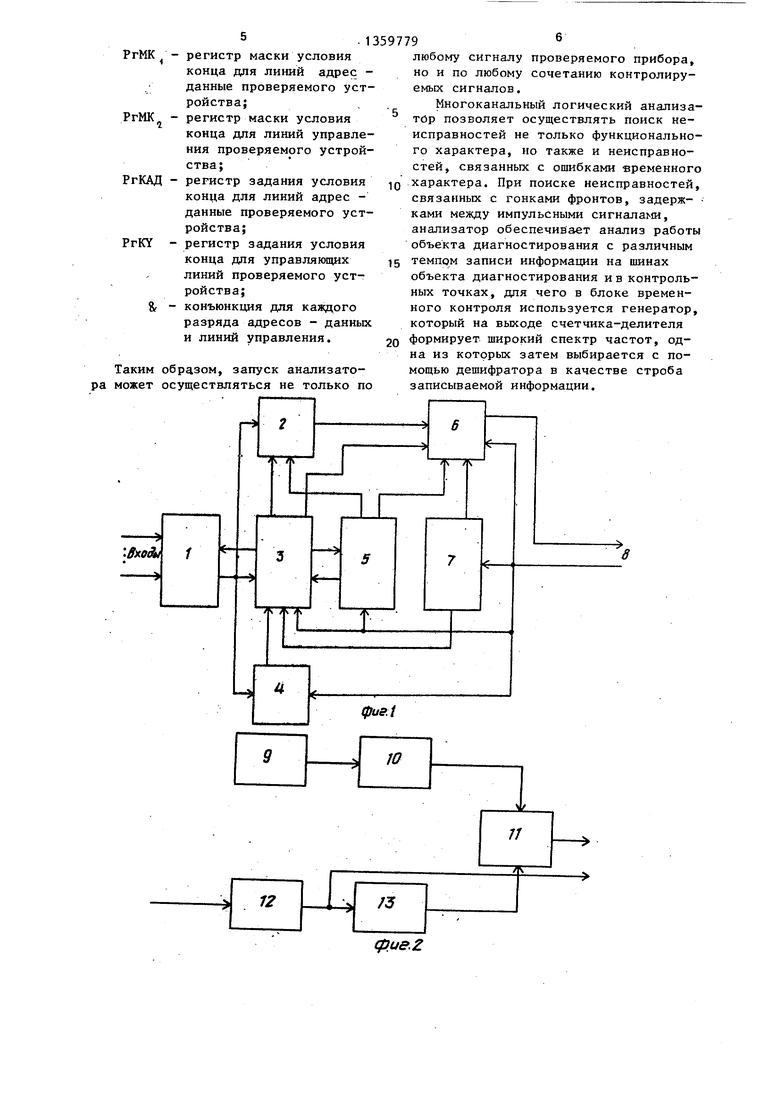

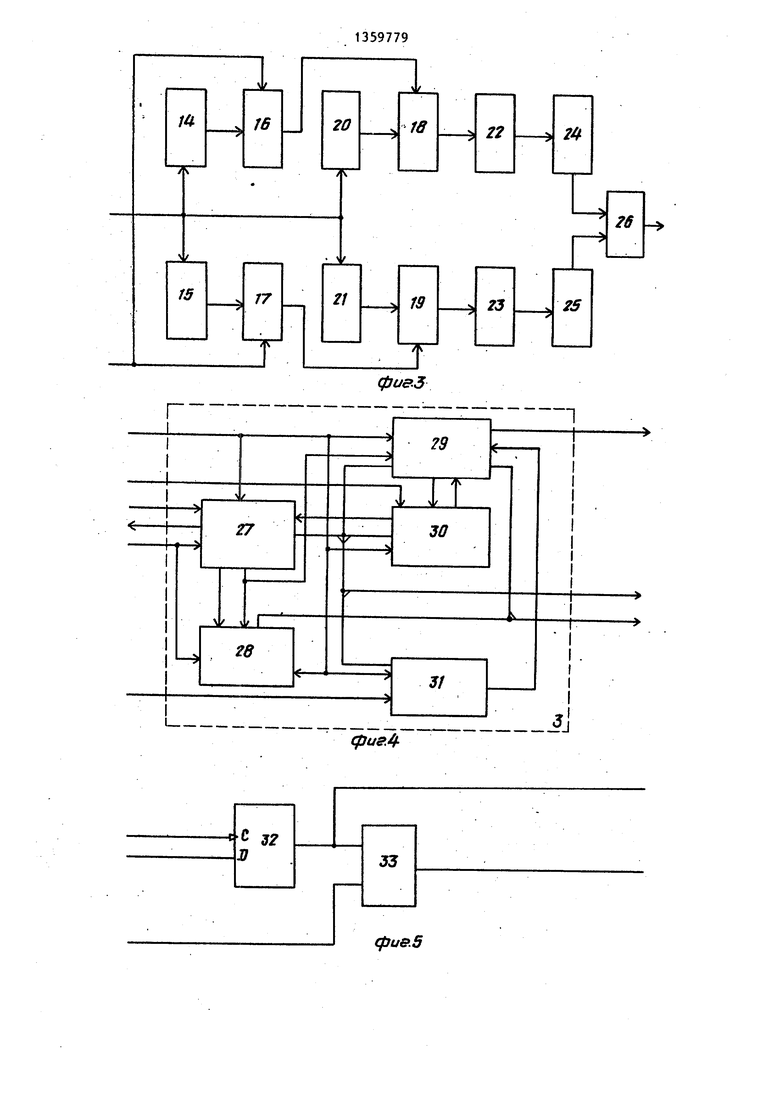

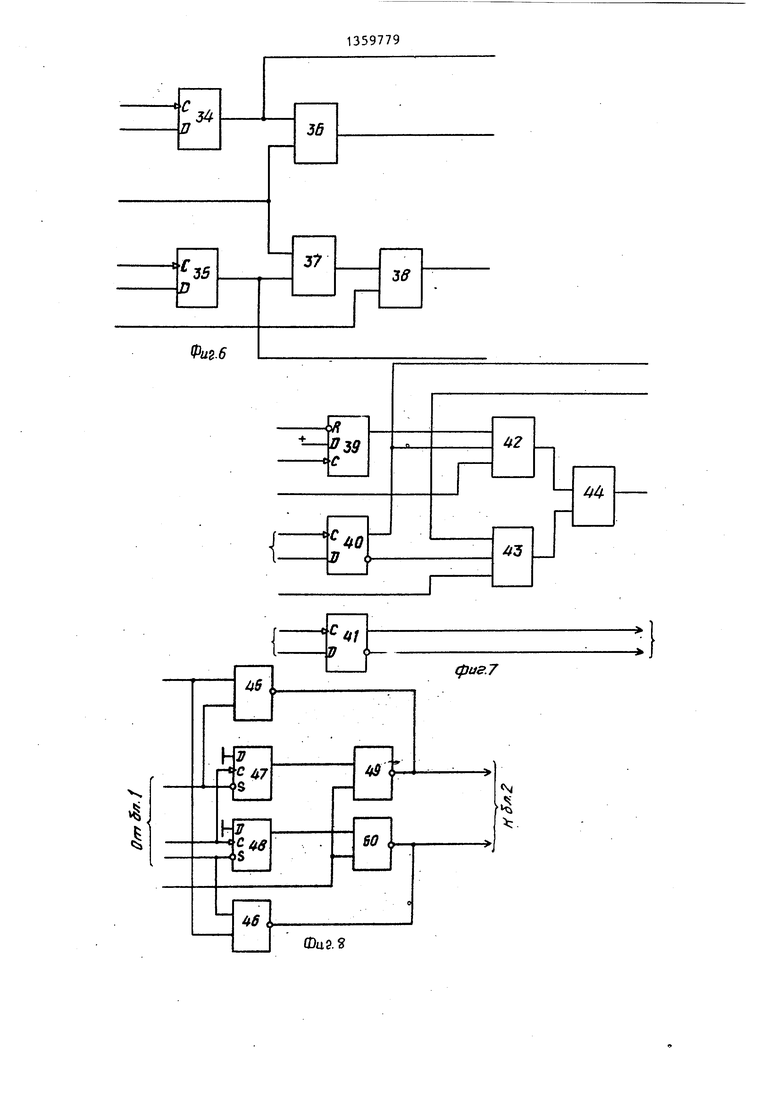

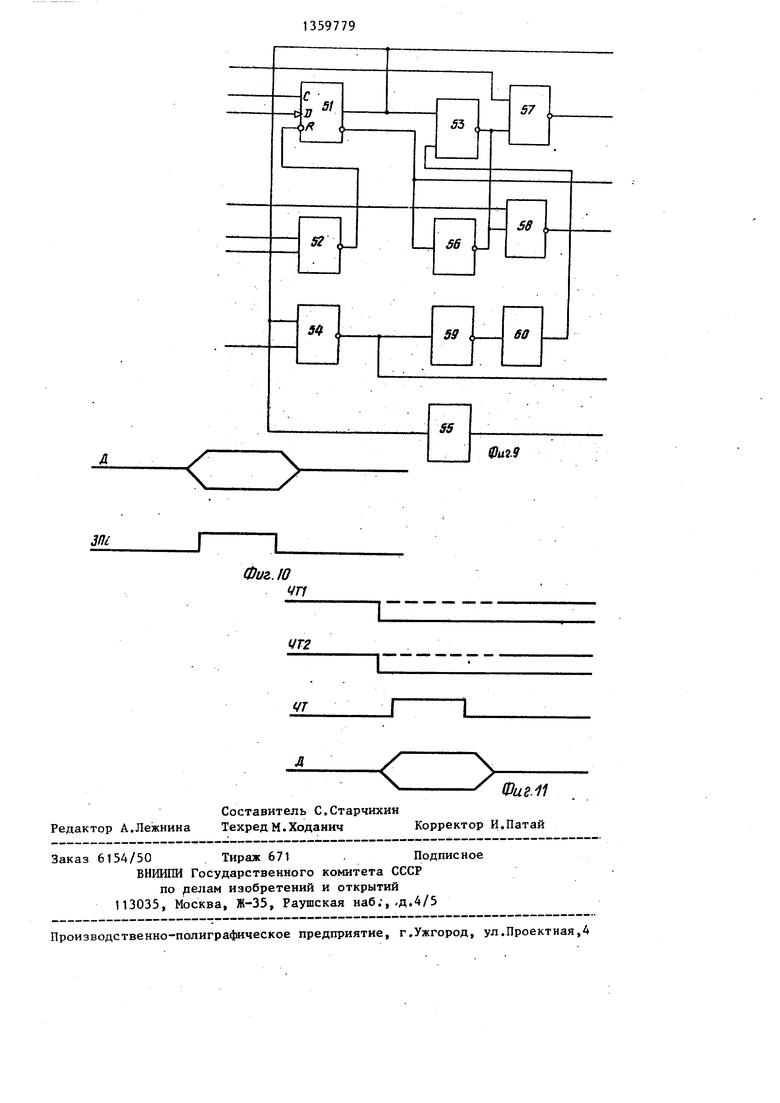

На фиг.1 изображена блок-схема многоканального логического анализатора; на фиг.2 - блок-схема блока временного контроля; на фиг.З - блок- схема блока запуска; на фиг.4 - блок-схема блока управления;на фиг.5- блок-схема узла переполнения памяти; на фиг.6 - блок-схема узла управления началом и концом записи; на фиг.7 - блок-схема узла выбора режима записи; на фиг.8 - блок-схема узла захвата сигналов; на фиг.9 - блок-схема узла выбора вида работ;на фиг. 10- временная диаграмма записи; на фиг.11- временная диаграмма чтения.

Многоканальный логический анализатор (фиг.1) содержит блок 1 коммутации и преобразования уровней,блок 2 памяти, блок 3 управления, блок 4 запуска, блок 5 формирования адреса, мультиплексор 6 и блок 7 временного контроля. Управление работой анализатора осуществляется с -пульта мик- ; ропрограммного управления (условно показаны шины 8 управления).

Блок временного контроля (фиг.2) содержит кварцевь)й генератор 9,счетчик-делитель 10, схему 11 совпадения, регистр 12 выС Ора частоты и дешифратор 13.

Блок запуска (фиг.З) состоит из регистра 14 маски начала записи и ,- регистра 15 маски конца записи, узов элементов И-НЕ 16 и 17, узлов 18 и 19 сравнения, регистров 20 и 21 .начала записи и конца записи соответственно, узлов элементов И-НЕ 22 и 23, элементов ИЛИ-НЕ 24 и 25 и триггера 26 разрешения записи.

Блок управления.(фиг.4) содержит узел 27 выбора режима записи, узел 28 захвата сигналов, узел 29 выбора вида работ, узел 30 управления началом и концом записи и узел 31 переполнения памяти.

Узел 31 переполнения памяти (фиг.5) содержит триггеры 32 и элемент И 33.

Узел 30 управления началом и кон- цом записи (фиг.6) содержит триггеры 34 и 35, элементы И 36 и 37 и элемент ИЛИ 38.

Узел 27 выбора режима записи

(фиг.7) содержит триггеры 39, 40 и 41 и элементы И 42, 43 и 44.

Узел 28 захвата сигналов (фиг.8) содержит элементы И-НЕ 45 и 46, триггеры 47 и 48 и элементы И 45 и 50.

Узел 29 выбора вида работ (фиг.9) содержит триггер 51, элемент ИЛИ 52, элементы И 53 и 54, буферный усилитель 55, элементы ИЛИ 56-59 и формирователь 60 импульса.

Пульт микропрограммного управления формирует два типа временных диаграмм (фиг.10 и 11).

Временные диаграммы, показанные на фиг.10, описывают процедуру записи в регистр состояния (триггеры 32, 34, 35, 40, 41, 51 в блоке 3 управления и регистр 12 в блоке 7 временного контроля), в регистр адреса (в блоке 5 формирования адреса), в регистр 14 маски начала записи-, в регистр 15 маски конца записи и в реги- стры 20 и 21 начала и конца записи (в блоке 4 запуска).Для этого на информационных выходах пульта микропрограммного управления устанавливаются данные и выдается соответствующий строб ЗП.

5

0

5

0

5

Временные диаграммы на фиг.11 описывают процедуру чтения из блока 2 памяти регистра адреса и регистра состояния. Для этого с пульта микропрограммного управления выдаются два потенциальных сигнала С ЧТ1,.ЧТ 2 и строб чтения ЧТ, управляющие мультиплексором 6. В течение действия строба ЧТ на входы блока микропрограммного управления поступают дрстоверные данные.

Анализатор работает следующим образом;

Контролируемые сигналы проверяемого прибора (в частности микроЭВМ) поступают через блок 1 коммутации и преобразования уровней на вход блока 2 памяти. Эти же сигналы параллельно поступают на блок 4 запуска, в котором происходит совпадение кода,задаваемого с пульта микропрограммного управления, с кодом, который информирует о состоянии шин проверяемого- прибора, в результате чего на выходах блока появляются либо не появляются сигналы разрешения записи

и запрещения записи, которые затем подаются э блок 3 управления, который может обеспечивать два режима записи: запись временных соотношений и лог1#ческий анализ (диагностическая трассировка).

Первый режим записи осуществляется при наличии сигнала разрешения записи с блока 4 запуска по сигналу из блока 7 временного контроля с частотой, программно устанавливаемой по шине 8.

Второй режим записи информации в память осуществляется как и в предыдущем режиме, при наличии сигнала разрешения записи, но вместо сигнала из блока 7 временного контроля используется сигнал из проверяемого прибора, который выбран как отображающий временной цикл работы этого прибора.

Анализатор накапливает информацию о состоянии проверяемого прибора в

10

1359779

с вполне определенной заданной частотой, который в дальнейшем будет стробировать записываемую в блок памяти информацию о состоянии проверя- емого прибора на всех шинах одновременно.

В блоке А запуска по сигналам, по-, ступающим по шине 8, происходит запись в регистры 14 и 15 масок, а также в регистры 20 и 21 начала записи и конца записи соответственно. Информация с шин проверяемого прибора поступает на входы узлов элементов И-НЕ 16 и 17, где происходит поразрядное маскирование. Далее с выходов элементов И-НЕ 16 и 17 сигналы поступают на входы узлов сравнения 18 и 19, на вторые входы которых поступают коды начала записи и конца записи с шины 8 через регистры 20 и 21,

Далее происходит сравнение кодов, свертка на элементах И-НЕ и ИЛИ-НЕ 22, 23, 24 и 25 и на выходе элемен15

20

1024 тактах перед остановом, осущест- 25 тов 24 и 25 вырабатываются два сиг- вляемым по сигналу Конец записи из нала Разрешение записи и Запрещение

блока 4 запуска, по сигналу Начало записи из блока 4 запуска либо выборочно по двум этим условиям. Состояния проверяемого прибора определяются значениями сигналов на шинах и в дополнительных точках проверяемого прибора, доступных с помощью пробников (зондов).

Анализатор имеет два вида работы: запись-контроль сигналов с шин проверяемого прибора и пробников и, чтение-анализ записанной информации.

Переход в режим чтения-анализа осуществляется по сигналам, которые формируются в блоке 3 управления: Переполнение памяти, Конец записи. Информация о состоянии диагностируемого прибора считывается из блока 2 памяти через мультиплексор 6, через который можно читать, и регистры логического анализа, доступные по чтению.

В блоке 7 временного контроля сигнал с кварцевого генератора 9 поступает на вход счетчика-делителя 10, на выходе которого получаются сигналы кратной частоты, которые подаются на схему 11 совпадения, на другой вход которой с дешифратора 13 поступает сигнал, соответствующий ко- ду, з.аписанному в регистр 12 выбора частоты. Таким образом, на выходе схемы совпадения выделяется сигнал

30

записи .Эти два сигнала имеют уровень логической единицы тогда, когда выполняются условия:

АД Чх РгМН © РгНАД

Сое YVPrMH ©PrHY

35

АД РгМК, © РгКАД Сое Y 8, РгМК 0 PrKY

где

АД 40

45

50

55

сигналы на линиях адрес-- данные проверяемого устройства;

COC.Y - сигналы на управляющих шинах проверяемого устройства;

РгМН, - регистр маски условия

начала для линий адрес - данные проверяемого устройства;

PrMH,j| - регистр маски условия начала для линий управления проверяемого устройства;

РгНАД - регистр задания условия начала для линий адрес. - данные проверяемого устройства;

РгНУ - регистр задания условия начала для управляющих линий проверяемого устройства;

25 тов 24 и 25 вырабатываются два сиг нала Разрешение записи и Запрещ ние

30

записи .Эти два сигнала имеют уровень логической единицы тогда, когда выполняются условия:

АД Чх РгМН © РгНАД

Сое YVPrMH ©PrHY

35

АД РгМК, © РгКАД Сое Y 8, РгМК 0 PrKY

где

АД 0

5

0

5

сигналы на линиях адрес-- данные проверяемого устройства;

COC.Y - сигналы на управляющих шинах проверяемого устройства;

РгМН, - регистр маски условия

начала для линий адрес - данные проверяемого устройства;

PrMH,j| - регистр маски условия начала для линий управления проверяемого устройства;

РгНАД - регистр задания условия начала для линий адрес. - данные проверяемого устройства;

РгНУ - регистр задания условия начала для управляющих линий проверяемого устройства;

РгМК - регистр маски условия

конца для линий адрес - данные проверяемого устройства;

РгМК - регистр маски условия

конца для линий управления проверяемого устройства;

РгКАД - регистр задания условия конца для линий адрес - данные проверяемого устройства;

PrKY - регистр задания условия конца дпя управляющих линий проверяемого устройства;

8 - конъюнкция для каждого разряда адресов - данных и линий управления.

Таким образом, запуск анализатоа может осуществляться не только по

779®

любому сигналу проверяемого прибора, но и по любому сочетанию контролируемых сигналов.

Многоканальный логический анализатор позволяет осуществлять поиск неисправностей не только функционально

го характера, но также и неисправностей, связанных с ошибками временного характера. При поиске неисправностей, связанных с гонками фронтов, задерж- ками между импульсными сигналами, анализатор обеспечивает анализ ра;боты объекта диагностирования с различным темпом записи информации на шинах объекта диагностирования и в контрольных точках, дпя чего в блоке временного контроля используется генератор, который на выходе счетчика-делителя формирует широкий спектр частот, одна из которых затем выбирается с помощью дешифратора в качестве строба записываемой информации.

cpue.Z

фие.З

фиеЛ

(ри&.5

39 с

{

40

U2

43

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство для контроля и регистрации асинхронных сигналов интерфейса | 1982 |

|

SU1084803A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для реализации подстановок | 1990 |

|

SU1805478A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Многоканальное устройство для сопряжения источников информации с вычислительной машиной | 1987 |

|

SU1437870A2 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

ftl

4/5

:|

фиа.7

У

С47

S

v§ I

У

-{с,.

f

Шцг.

J/7/

Фиг.. Ю

л

X /

Редактор А.Лежнина

(Dus.11

Составитель С.Старчихия

Техред М.ХоданичКорректор И.Патай

Заказ 6154/50Тираж 671Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб;,-д.4/5

Пройзводств1н;;о-п йгр1ф;1ч1ское предприятие, г.Ужгород, ул.Проектная.А

X /

| Устройство для многоканального контроля | 1976 |

|

SU608126A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Патент США № 4040025,кл.364-900, опублик | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1987-12-15—Публикация

1984-05-30—Подача