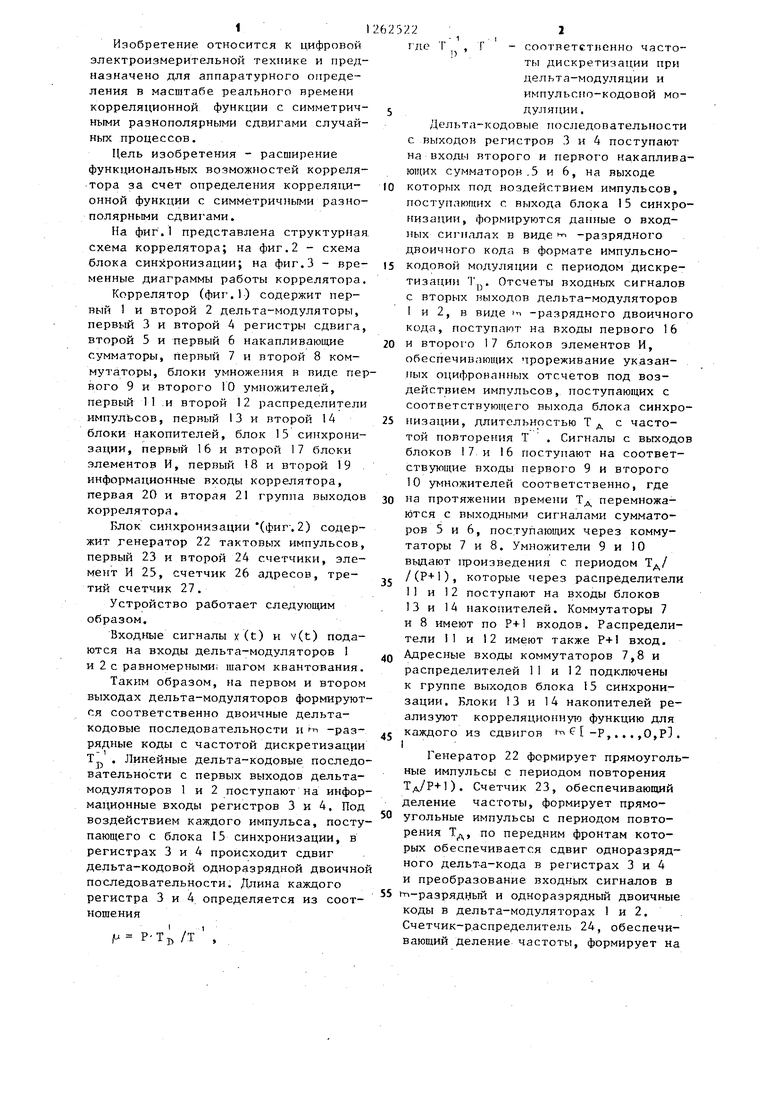

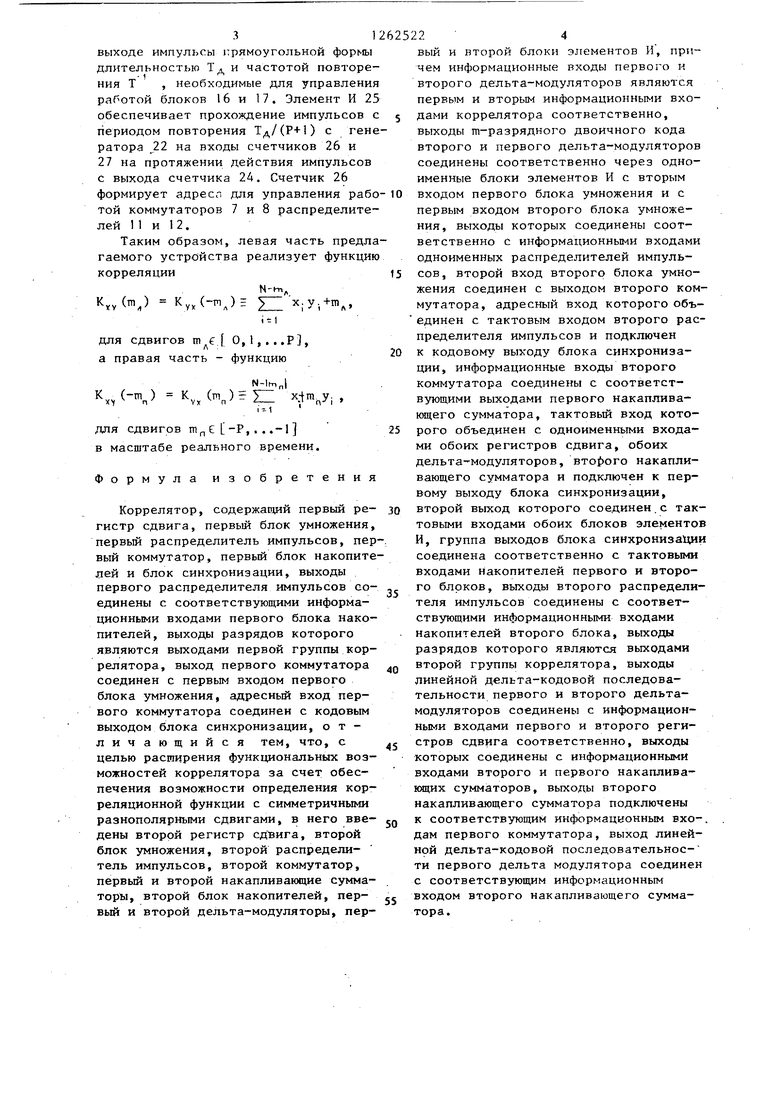

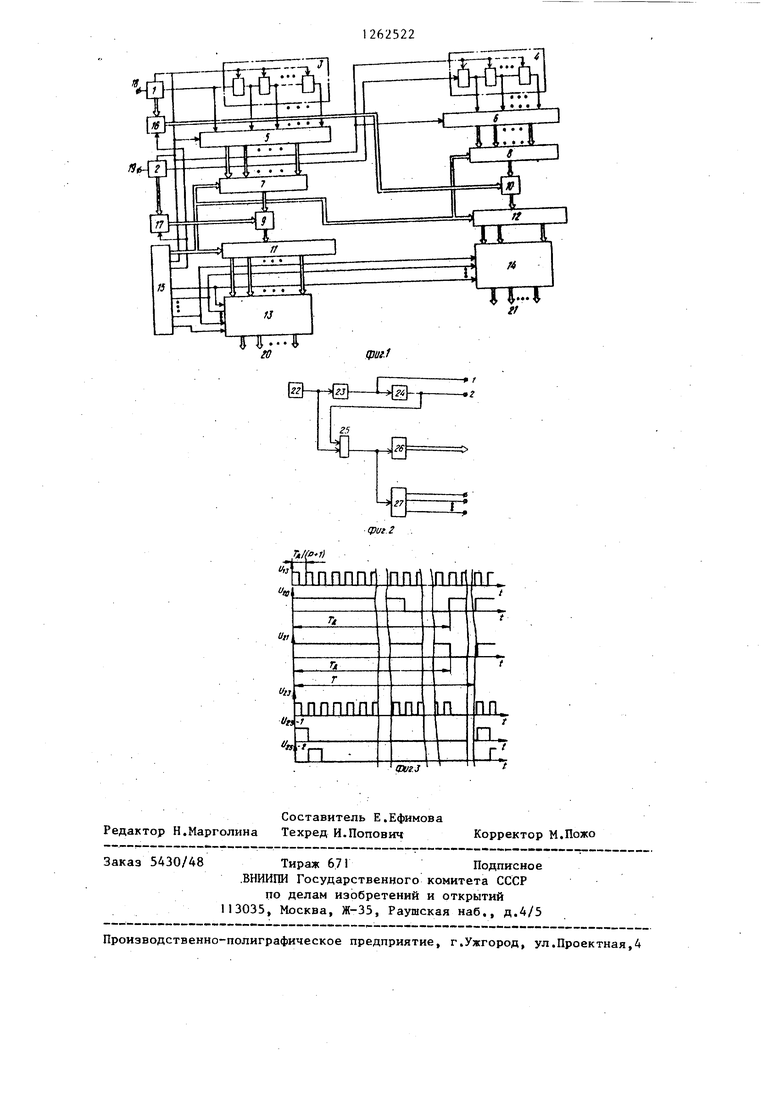

Изобретение относится к цифровой электроизмерительной технике и нреднаэначено для аппаратурного определения в масштабе реального времени корреляционной функции с симметричными разнополярными сдвигами случайных процессов. Цель изобретения - расширение функциональных возможностей коррелятора за счет определения корреляционной функции с симметричными разнополярными сдвигами. На фиг.1 представлена структурная схема коррелятора; на фиг.2 - схема блока синхронизации; на фиг.З - временные диаграммы работы коррелятора. Коррелятор (фиг.1) содержит первый 1 и второй 2 дельта-модуляторы, первый 3 и второй А регистры сдвига, второй 5 и первый 6 накапливающие сумматоры, первый 7 и второй 8 коммутаторы, блоки умножения в виде пер вого 9 и второго 10 умножителей, первый 11 .и второй 12 распределители импульсов, первый 13 и второй 14 блоки накопителей, блок 15 синхронизации, первый 16 и второй 17 блоки элементов И, первый 18 и второй 19 информационные входы коррелятора, первая 20 и вторая 21 группа выходов коррелятора. Блок синхронизации (Фнг. 2) содержит генератор 22 тактовых импульсов, первый 23 и второй 24 счетчики, элемент И 25, счетчик 26 адресов, третий счетчик 27. Устройство работает следующим образом. Входные сигналы х(t) и v(t) подаются на входы дельта-модуляторов I и 2 с равномерными; шагом квантования. Таким образом, на первом и втором выходах дельта-модуляторов формируют ся соответственно двоичные дельтакодовые последовательности и -разрядные коды с частотой дискретизации Т . Линейные дельта-кодовые последо вательности с первых выходов дельтамодуляторов 1 и 2 поступают на инфор мационные входы регистров 3 и 4, Под воздействием каждого импульса, посту пающего с блока 15 синхронизации, в регистрах 3 и 4 происходит сдвиг дельта-кодовой одноразрядной двоично последовательности. Длина каждого регистра 3 и 4 определяется из соотношенияf Р-т1 /Т , 2 где , I - соответственно частоты дискретизации при дельта-модуляции и импульсно-кодовой модуляции. Дельта-кодовые последовательности с выходов регистров 3 и 4 поступают на входы второго и первого накапливающих сумматоров .5 и 6, на выходе которых под воздействием импульсов, поступающих с выхода блока 15 синхронизации, формируются данные о входных сигналах в виде -разрядного двоичного кода в формате импульснокодовой модуляции с периодом дискреОтсчеты входных сигналов тизации с вторых выходов дельта-модуляторов Iи 2, в виде ч -разрядного двоичного кода, поступают на входы первого 16 и второго 17 блоков элементов И, обеспечив.чющих прореживание указанных оцифрованных отсчетов под воздействием импульсов, поступающих с соответствующего выхода блока синхронизации, длительностью Т д с частотой повторения Т . Сигналы с выходов блоков 17 и 16 поступают на соответствующие входы первого 9 и второго 10 умножителей соответственно, где на протяжении времени Тд перемножаются с выходными сигналами сумматоров 5 и 6, поступающих через коммутаторы 7 и 8. Умножители 9 и 10 выдают произведения с периодом Тд/ /(Р+1), которые через распределители IIи 12 поступают на входы блоков 13 и 14 накопителей. Коммутаторы 7 и 8 имеют по Р+1 входов. Распределители II и 12 имеют также Р+1 вход. Адресные входы коммутаторов 7,8 и распределителей 11 и 12 подключены к группе выходов блока 15 синхронизации. Блоки 13 и 14 накопителей реализуют корреляционную функцию для каждого из сдвигов i -Р,...,0,р. Генератор 22 формирует прямоугольные импульсы с периодом повторения Тд/Р+1). Счетчик 23, обеспечивающий деление частоты, формирует прямоугольные импульсы с периодом повторения Тд, по передним фронтам которых обеспечивается сдвиг одноразрядного дельта-кода в регистрах 3 и 4 и преобразование входных сигналов в 1-п-разрядный и одноразрядный двоичные коды в дельта-модуляторах 1 и 2. Счетчик-распределитель 24, обеспечивающий деление частоты, формирует на 3 выходе импульсы прямоугольной формы длительностью Тд и частотой повторе ния Т , необходимые для управлени раГОтой блоков 16 и 17. Элемент И 2 обеспечивает прохождение импульсов периодом повторения Тд/(Р+1) с ген ратора „22 на входы счетчиков 26 и 27 на протяжении действия импульсов с выхода счетчика 24. Счетчик 26 формирует адресп для управления раб той коммутаторов 7 и 8 распределите лей П и I 2. Таким образом, левая часть предл гаемого устройства реализует функци корреляции Ми,, К,, (т) Ky,(-Fi)s х.у,+т, i-1 для сдвигов m рf О,1,...РЗ, а правая часть - функцию ) хЮ. ДЛЯ сдвигов mг, е -Р, .. .-1 в масштабе реального времени. Формула изобретения Коррелятор, содержащий первый регистр сдвига, первый блок умножения, первый распределитель импульсов, пер вый коммутатор, первый блок накопите лей и блок синхронизации, выходы первого распределителя импульсов соединены с соответствующими информационными входами первого блока накопителей, выходы разрядов которого являются выходами первой группы коррелятора, выход первого коммутатора соединен с первым входом первого блока умножения, адресный вход первого коммутатора соединен с кодовым выходом блока синхронизации, отличающийся тем, что, с целью расширения функциональных возможностей коррелятора за счет обеспечения возможности определения корреляционной функции с симметричными разнополярными сдвигами, в него вне- дены второй регистр сдвига, второй блок умножения, второй распределитель импульсов, второй коммутатор, первый и второй накапливающие сумматоры, второй блок накопителей, первый и второй дельта-модуляторы, пер22вый и второй блоки элементов И, причем информационные входы первого и второго дельта-модуляторов являются первым и вторым информационными входами коррелятора соответственно, выходы т-разрядного двоичного кода второго и первого дельта-модуляторов соединены соответственно через одноименные блоки элементов И с вторым входом первого блока умножения и с первым входом второго блока умножения, выходы которых соединены соответственно с информационными входами одноименных распределителей импульсов, второй вход второго блока умножения соединен с выходом второго коммутатора, адресный вход которого объединен с тактовым входом второго распределителя импульсов и подключен к кодовому выходу блока синхронизации, информационные входы второго коммутатора соединены с соответствующими выходами первого накапливакяцего сумматора, тактовый вход которого объединен с одноименными входами обоих регистров сдвига, обоих дельта-модуляторов, второго накапливающего сумматора и подключен к первому выходу блока синхронизации, второй выход которого соединен.с тактовыми входами обоих блоков элементов И, группа выходов блока синхронизации соединена соответственно с тактовыми входами накопителей первого и второго блоков, выходы второго распределителя импульсов соединены с соответствующими информационными входами накопителей второго блока, выходы разрядов которого являются выходами второй группы коррелятора, выходы линейной дельта-кодовой последовательности первого и второго дельтамодуляторов соединены с информационными входами первого и второго регистров сдвига соответственно, выходы которых соединены с информационными входами второго и первого накапливакнцих сумматоров, выходы второго накапливающего сумматора подключены к соответствующим информационным вхо-. дам первого коммутатора, выход линейнрй дельта-кодовой последовательноети первого дельта модулятора соединен с соответствующим информационным входом второго накапливающего сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1986 |

|

SU1425711A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Коррелятор | 1988 |

|

SU1705835A1 |

| Адаптивный автокоррелятор | 1990 |

|

SU1774345A1 |

| Коррелятор | 1989 |

|

SU1665386A1 |

| Коррелятор | 1978 |

|

SU781820A1 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ФАЗОМАНИПУЛИРОВАННЫХ КОДОВЫХ СИГНАЛОВ | 2002 |

|

RU2236086C2 |

| УСТРОЙСТВО ДЛЯ ГЕОЭЛЕКТРОРАЗВЕДКИ | 2017 |

|

RU2668306C1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2018 |

|

RU2701059C1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

Изобретение относится к цифровой электроизмерительной технике и предназначено для аппаратурного определения в масштабе реального времени корреляционной функции с симметричными разнополярными сдвигами случайных процессов. Цель изобретения расширение функциональных возможностей коррелятора .за счет обеспечения возможности определения корреляционной функций с симметричными разнополярными сдвигами. Цель изобретения достигается за счет введения в коррелятор регистра сдвига, блока умножения, распределителя импульсов, коммуQ S татора, двух накапливающих сумматоров, блока накопителей, двух дельта(Л модуляторов и двух блоков элементов И с .соответствующими функциональными связями между ними и известными блоками коррелятора. 3 ил.

| Tones D | |||

| An on board digital correlator for spacecraft VLE radio weva studies - lEE Trans | |||

| Geosi | |||

| Electron., 1974, 12, № I, 9-18 | |||

| Gatland H.B., Lovell B.W | |||

| A correlation computer using delta modulation techniques - l.Sci | |||

| lnstrum,1965,42, 8, p 529-532 | |||

| ЦИФРОВОЙ КОРРЕЛЯТОР | 0 |

|

SU275542A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1985-03-27—Подача