со

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1988 |

|

SU1705835A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Коррелятор | 1985 |

|

SU1262522A1 |

| Коррелятор | 1986 |

|

SU1425711A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

| Устройство для определения взаимной корреляционной функции | 1990 |

|

SU1751779A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1408531A1 |

| Цифровой фильтр | 1990 |

|

SU1780089A1 |

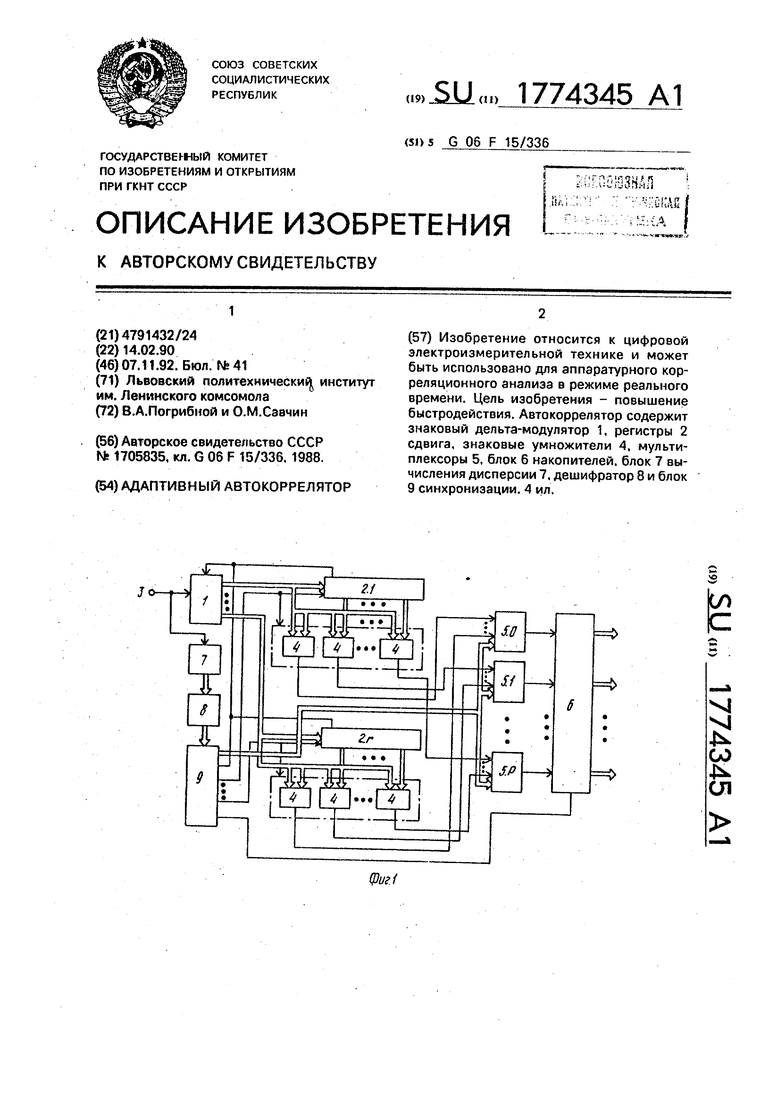

Изобретение относится к цифровой электроизмерительной технике и может быть использовано для аппаратурного корреляционного анализа в режиме реального времени. Цель изобретения - повышение быстродействия. Автокоррелятор содержит знаковый дельта-модулятор 1, регистры 2 сдвига, знаковые умножители 4, мультиплексоры 5, блок 6 накопителей, блок 7 вычисления дисперсии 7. дешифратор 8 и блок 9 синхронизации.4 ил.

VJ VI

Јь СО

4

СЛ

Изобретение относится к цифровой электроизмерительной технике, в частности к цифровым корреляторам, и может быть использовано для аппаратурного определения в режиме реального пременм ав- токорреляционной функции случайного процесса.

Целью изобретения является повышение быстродействия при заданной разрешающей способности.

Отдельный ранг коррелятора работает по алгоритряу

(т)

1

N

N - 1 - т (|) л (Л -- Ј d OdK+m, (1),15 т К о

где f - ранг разности и кода; m - номер канала (сдвига).20

Суммарная корреляционная функция

)(т)|лгхч)(т)

(2)

30

40

вычисляется коррелятором,

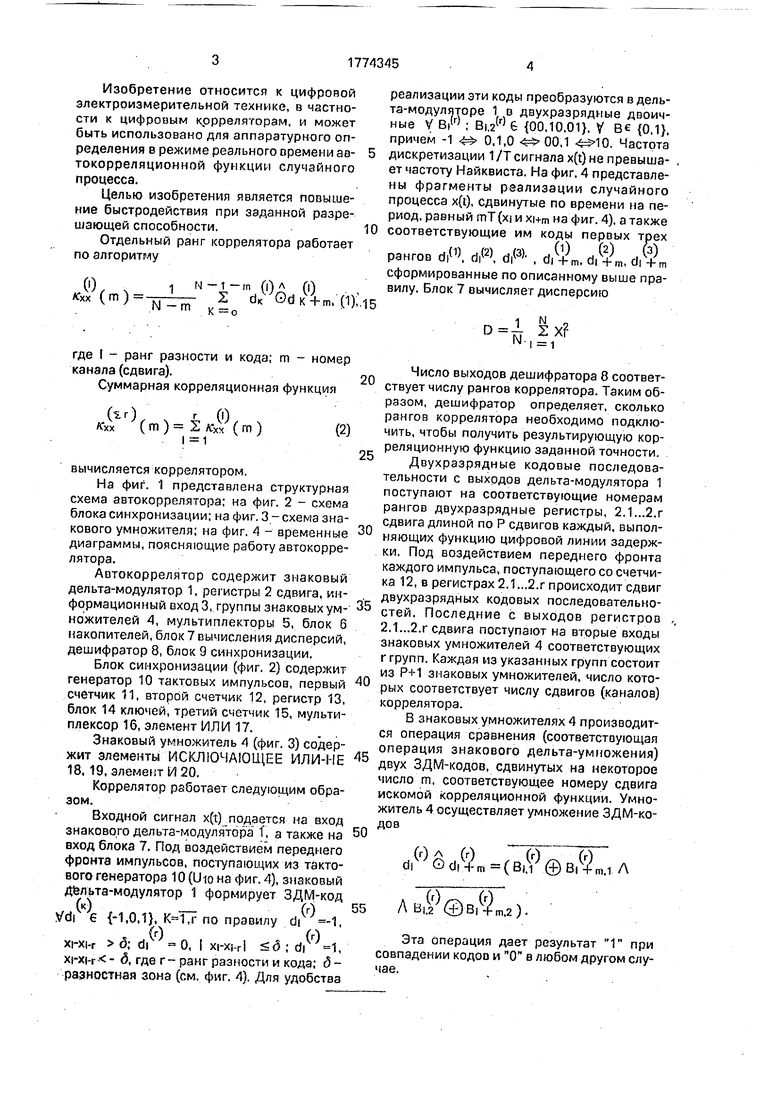

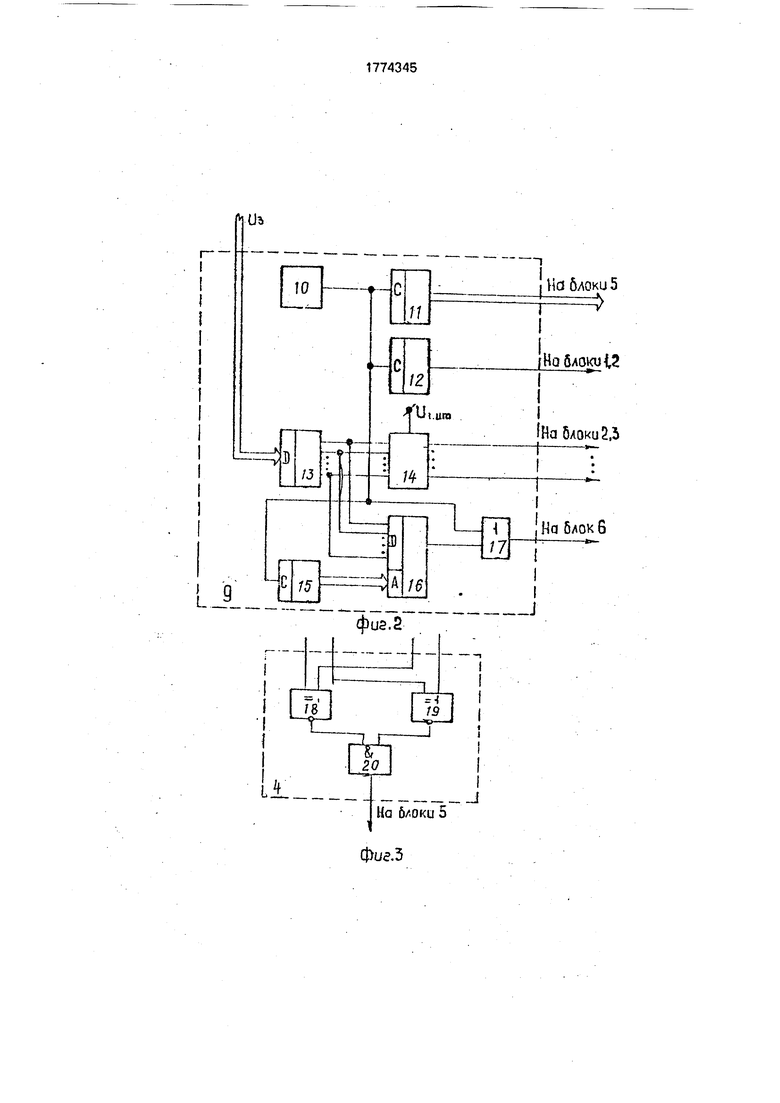

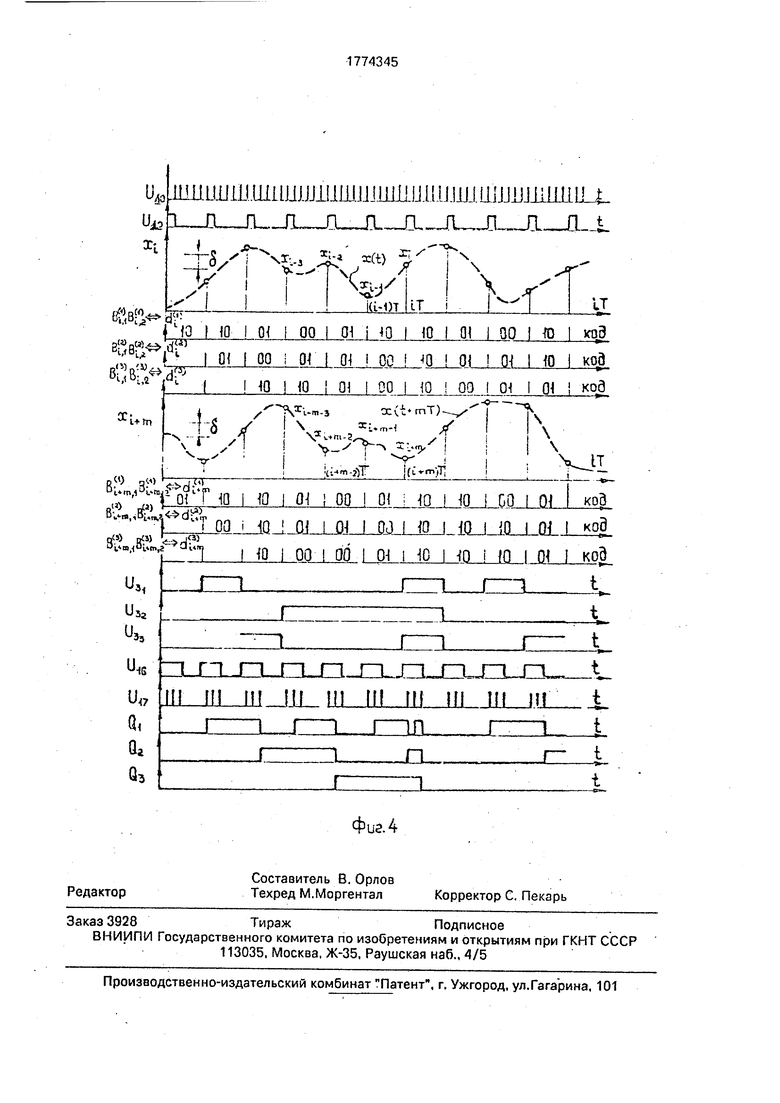

На фиг. 1 представлена структурная схема автокоррелятора; на фиг. 2 - схема блока синхронизации; на фиг. 3 - схема знакового умножителя; на фиг. 4 - временные иаграммы, поясняющие работу автокорреятора.

Автокоррелятор содержит знаковый ельта-модулятор 1, регистры 2 сдвига, информационный вход 3, группы знаковых ум- 35 ножителей 4, мультиплекторы 5, блок б накопителей, блок 7 вычисления дисперсий, дешифратор 8, блок 9 синхронизации.

Блок синхронизации (фиг, 2) содержит генератор 10 тактовых импульсов, первый счетчик 11, второй счетчик 12, регистр 13, блок 14 ключей, третий счетчик 15, мультиплексор 16, элемент ИЛИ 17.

Знаковый уь ножитель 4 (фиг. 3) содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ 18. 19, элемент И 20.

Коррелятор работает следующим образом.

Входной сигнал х(т) подается на вход знакового дельта-модулятора 1, а также на 50 вход блока 7. Под воздействием переднего фронта импульсов, поступающих из тактового генераторз 10 (Uio на фиг. 4), знаковый Дельта-модулятор 1 формирует ЗДМ-код

(к)(г)

di € {-1,0,1}, ,г по правилу di -1,

xi-xi-r б; di - О, I xi-xi-ri д ; di 1, xi-xi-r - 3, где г- ранг разности и кода; д - разностная зона (см. фиг. 4). Для удобства

ьь

0

5

0

5

0

0

5

0

реализации эти коды преобразуются в дельта-модуляторе 1 в двухразрядные двоичные V Bi(r) ; B|,2W G {00.10,01}. V Be {0.1}, причем -1 Ф 0,1,0 ,1 . Частота дискретизации 1/Т сигнала x(t) не превышает частоту Найквиста. На фиг. 4 представле- ны фрагменты реализации случайного процесса x(i), сдвинутые по времени на период, равный mT(xi и xi+m на фиг. 4), а также соответствующие им коды первых трех

i 11 ы га 0) (2) W рангов di(1}, di{2), di(3) , dj Vm, di Vm, diVm

сформированные по описанному выше правилу. Блок 7 вычисляет дисперсию

ИХ N

Число выходов дешифратора 8 соответствует числу рангов коррелятора. Таким образом, дешифратор определяет, сколько рангов коррелятора необходимо подключить, чтобы получить результирующую корреляционную функцию заданной точности.

Двухразрядные кодовые последовательности с выходов дельта-модулятора 1 поступают на соответствующие номерам рангов двухразрядные регистры, 2.1...2.г сдвига длиной по Р сдвигов каждый, выполняющих функцию цифровой линии задержки. Под воздействием переднего фронта каждого импульса, поступающего со счетчика 12, в регистрах 2.1...2.г происходит сдвиг двухразрядных кодовых последовательностей. Последние с выходов регистров 2.1...2.г сдвига поступают на вторые входы знаковых умножителей 4 соответствующих г групп. Каждая из указанных групп состоит из Р+1 знаковых умножителей, число которых соответствует числу сдвигов (каналов) коррелятора.

В знаковых умножителях 4 производится операция сравнения (соответствующая операция знакового дельта-умножения) двух ЗДМ-кодов, сдвинутых на некоторое число т, соответствующее номеру сдвига искомой корреляционной функции. Умножитель 4 осуществляет умножение ЗДМ-кодов

:(вн

(О

В$га.1

А

50

ьь

л (0/ (О Л В,,2 ©B|Vm.2).

Эта операция дает результат 1 при совпадении кодоо и О в любом другом случае.

Результаты ЗДМ-умножений поступают на соответствующие информационные входы мультиплексоров 5.0...5.Р, число которых соответствует числу сдвигоо (каналов) коррелятора. На управляющие входы мультиплексоров 5.0...5.Р поступает адрес из счетчика 11. Мультиплексоры 5.0...5.Р за один период Т (Ui2 на фиг. 4) опрашивают ЗДМ-умножители 4.1....4.г, задействованные на данной реализации исследуемого процесса. Информация с выходов мультиплексоров подается на информационные входы блока 6 накопителей, состоящего из Р+1 счетчиков импульсов. Тактовые входы счетчиков импульсов объединены с тактовым входом блока 6 накопителей, куда они поступают с выхода элемента ИЛИ 17 (Uie на фиг. 4).

Напряжение Uio представляет собой напряжение на выходе тактового генератора 10, Ui2 (фиг. 4) - напряжение на выходе второго счетчика 12. Диаграмма, представленная на фиг. 4, составлена для случая , т.е. задействовано три ранга коррелятора. На регистр 13 блока 9 поступает код из блока 7. Из регистра 13 код поступает на блок 14 ключей. Блок 14, выполненный на аналоговых ключах, в зависимости от кода, поступающего из регистра 13, подключает напряжение питания 1)пит на нужные регистры 2 сдвига и умножители 4. Выход регистра 13 подключен также к информационным входам мультиплексора 16, на тактовый вход которого подается адрес с выхода третьего счетчика. С выхода мультиплексора напряжение (U16 на фиг. 4) поступает на второй вход элемента ИЛИ, на первый вход которого подается напряжение с выхода тактоеого генератора 10 (Ою на фиг. 4). Элемент ИЛИ формирует тактовую последовательность, соответствующую количеству подключенных рангов коррелятора (Uu на фиг. 4). На фиг. 4 представлены также диаграммы напряжений первых трех разрядов счетчиков блока накопителей (СЬ...Оз).

Таким образом, в устройстве реализовано вычисление алгоритма (1), (2) в масштабе реального времени и с высокой экономичностью.

Формула изобретения

Адаптивный автокоррелятор, содержащий два регистра сдвига, знаковый дельта- модулятор, два знаковых умножителя, первый мультиплексор, блок накопителей, блок синхронизации, первый выход которого соединен с тактовыми входами первого и второго регистров сдвига и знакового дельта-модулятора, выход сигнала первого ранга которого соединен с информационным входом первого регистра сдвига, информационный вход знакового дел ьта-модулятора

является информационным входом автокоррелятора, второй и третий выходы блока синхронизации соединены соответственно с тактовым входом блока накопителей и с управляющим входом первого мультиплексора, группа выходов блока накопителей является группой выходов значений корреляционной функции автокоррелятора, отличающийся тем, что. с целью

0 повышения быстродействия, в него дополнительно введены (г-2)(г- число анализируемых рангов знакового дельта-модулированного сигнала) регистров сдвига, г групп знаковых умножителей, р мультиплексоров (р - число

5 сдвигов сигнала при вычислении автокорреляционной функции), блок вычисления дисперсии и дешифратор, причем вход блока вычисления дисперсии подключен к информационному входу автокоррелятора, выход

0 блока вычисления дисперсии через дешифратор соединен с входом задания временного параметра блока синхронизации, i-й () выход группы блока синхронизации соединен с входами разрешения рабо5 ты 1-го регистра сдвига, первого и второго знаковых умножителей и знаковых умножителей i-й группы, первым и вторым информационными входами первого знакового умножителя, с первым входом второго зна0 кового умножителя и первыми входами знаковых умножителей первой группы, второй вход второго знакового умножителя соединен с первым выходом первого регистра сдвига, j-й ) выход первого регистра

5 сдвига соединен с вторым входом (j-1)-ro знакового умножителя первой группы, выходы первого и второго знаковых умножителей соединены с первыми информационными входами соответственно первого и второго

0 мультиплексоров, выход (j+1)-ro знакового умножителя первой группы соединен с первым входом (j+1)-ro мультиплексора, выход сигнала К-го() ранга знакового дельта-модулятора соединен с информационным

5 входом К-го регистра сдвига, с первыми входами знаковых умножителей r-й группы и вторым входом первого знакового умножителя r-й группы, 1-й (, ..., Р) выход k-ro регистра сдвига соединен с вторым входом

0 (1+1)-го знакового умножителя k-й группы, выходы знаковых умножителей k-й группы соединены с k-ми информационными входами соответствующих мультиплексоров, выходы которых соединены с соотвегству5 ющими информационными входами блока накопителей, тактовые входы с третьего по r-й регистров сдвига соединены с первым выходом блока синхронизации, третий выход которого соединен с управляющими входами с второго по р-й мультиплексоров.

Г

g пяо/д DH

5/ h

п

8/

-f

5 гпф

at Ct Ui

U&

и

I;

to.

Eoua i o,

,

TO«d

mjjHj ojO-fliJ OJOJsS.

i 00 i ОМ (H

.

кой

40 MO т I 00 MO 00 (H I ОМ коД

oc

i+m

.n.j

Л:8Х v-A/ i -4-m-JX() у ,., /

x

-

|(-.)Т

у- I

-ч -с;..ту i

j(i m |T;

VJI

.i;, .,

iO I ffl l ОП 00 I Oi lQ.

o. rfj) .,..ji

коВ

oa M0 . Qn M , QJ , jo M0 i i0 IJH , Kog

rf a «j

,-(,2

.

кой

- /

у- I

-ч -с;..ту i

j(i m |T;

VJI

,

коВ

| Коррелятор | 1988 |

|

SU1705835A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

Авторы

Даты

1992-11-07—Публикация

1990-02-14—Подача