.

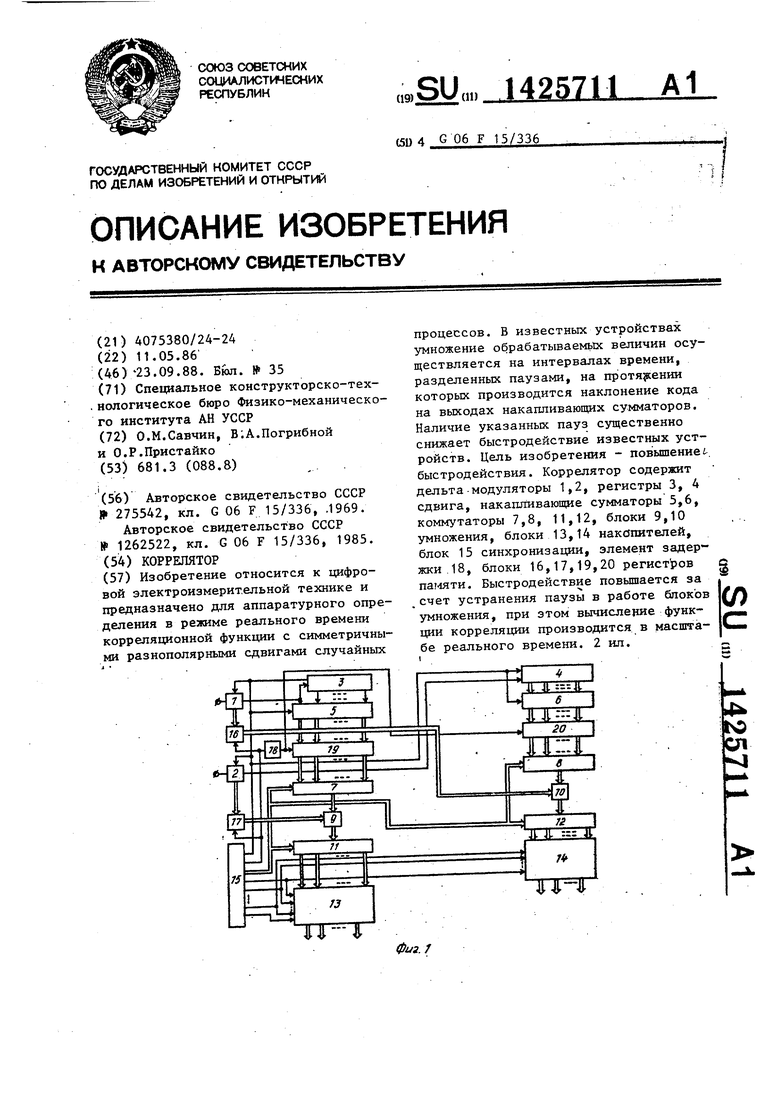

Изобретение относится к цифровой электроизмерительной технике и предназначено для аппаратурного определения в режиме реального времени корреляционной функции с симметричными разнополярными сдвигами случайных процессов.

Цель изобретения - повышение быстродействия.

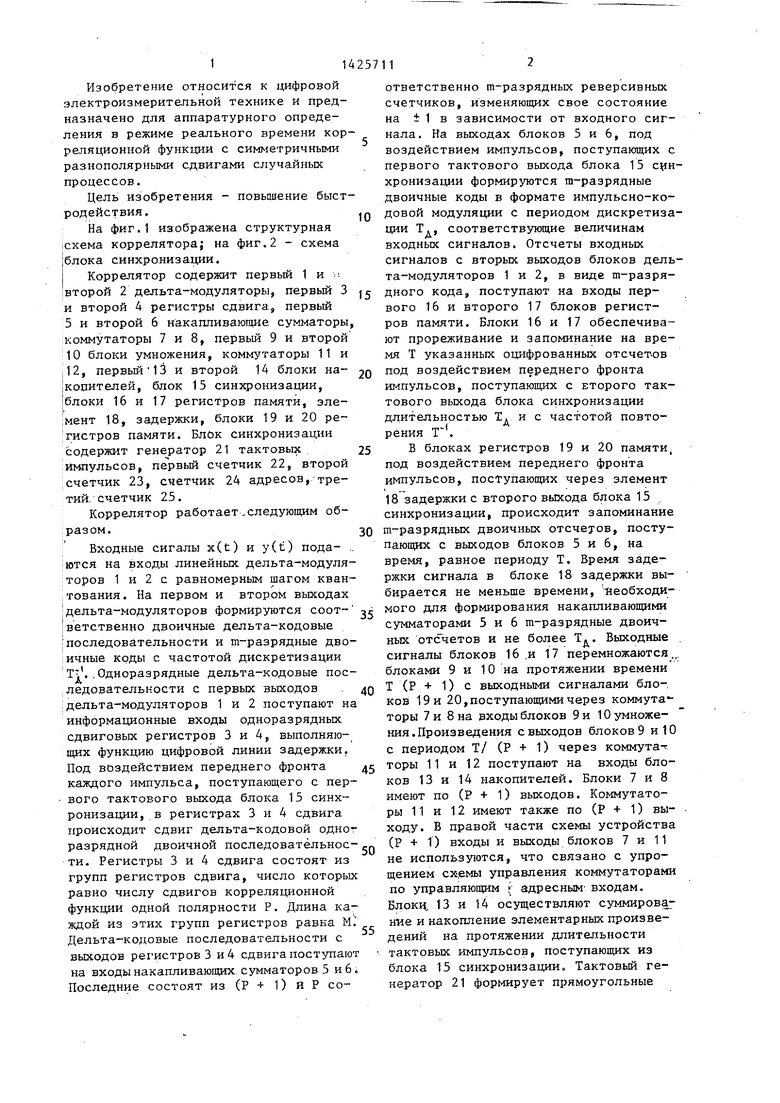

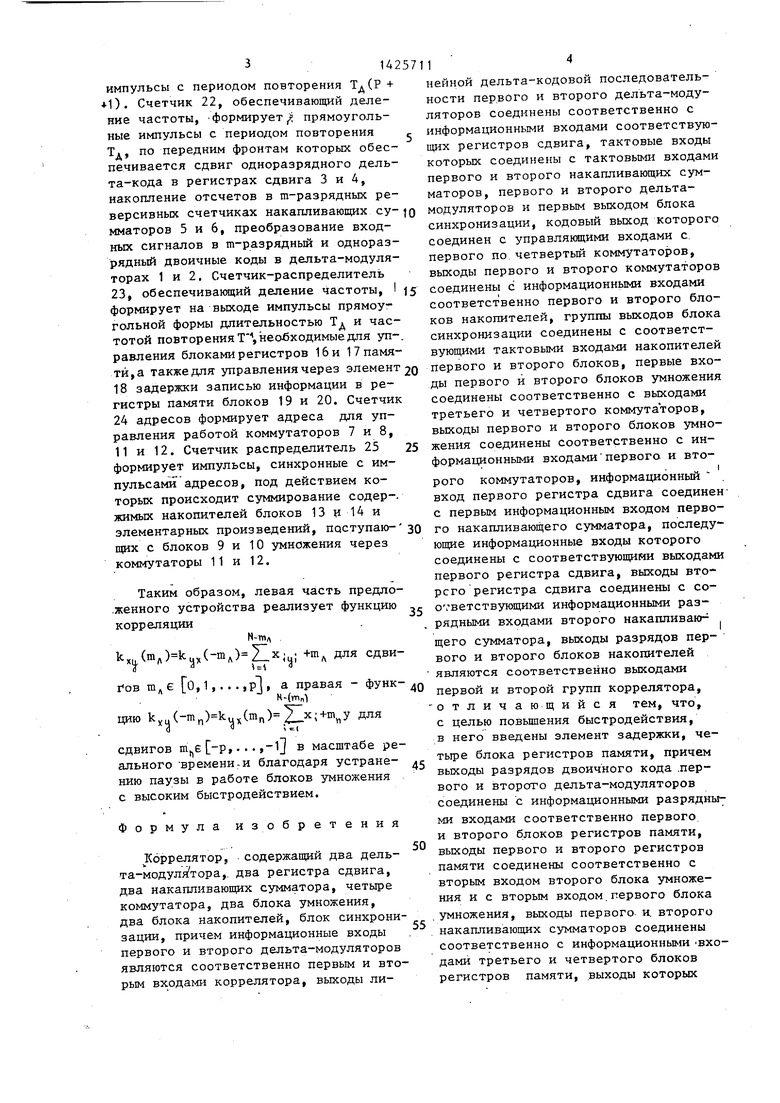

На фиг.1 изображена структурная юхема коррелятора; на фиг.2 - схема |блока синхронизации. I Коррелятор содержит первый 1 и второй 2 дельта-модуляторы, первый 3 и второй 4 регистры сдвига, первый 5 и второй 6 накапливающие сумматоры, коммутаторы 7 и 8, первый 9 и второй 10 блоки умножения, коммутаторы 11 и ;12, первый 13 и второй 14 блоки на- |коцителей, блок 15 синхронизации, (блоки 16 и 17 регистров памяти, эле- ;мент 18, задержки, блоки 19 и 20 ре- :гистров памяти. Блок синхронизации содержит генератор 21 тактовых ;иь«1ульсов, пеЪвьй счетник 22, второй счетчик 23, счетчик 24 адресов, третий, -счетчик 25.

Коррелятор работает.следующим об- :разом.

: Входные сигалы x(t) и y(t) пода- .. ;ются на входы линейных дельта-модуляторов 1 и 2 с равномерньм шагом кван- ; тования. На первом и втором выходах :дельта-модуляторов формируются соот- :ветственно двоичные дельта-кодовые последовательности и т-разрядные дво- :ичные коды с частотой дискретизации . .Одноразрядные дельта-кодовые последовательности с первых выходов :дельта-модуляторов 1 и 2 поступают на информационные входы одноразрядных сдвиговых регистров 3 и 4, выполняю- щих функцию цифровой линии задержки. Под воздействием переднего фронта каждого импульса, поступающего с первого тактового выхода блока 15 синхронизации, в регистрах 3 и 4 сдвига происходит сдвиг дельта-кодовой одног разрядной двоичной последовательности. Регистры 3 и 4 сдвига состоят из групп регистров сдвига, число которых равно числу сдвигов корреляционной функции одной полярности Р. Длина каждой из этих групп регистров равна М, Дельта-кодовые последовательности с выходов регистров 3 и 4 сдвига поступают на входы накапливающих, сумматоров 5 и 6. Последние состоят из (Р -i- 1) и Р со0

5

0

5

0

5

0

5

0

5

ответственно т-разрядных реверсивных счетчиков, изменяющих свое состояние на i1 в зависимости от входного сигнала. На выходах блоков 5 и 6, под воздействием импульсов, поступающих с первого тактового выхода блока 15 срн- хронизации формируются ш-разрядные двоичные коды в формате импульсно-ко- довой модуляции с периодом дискретизации Тд, соответствующие величинам входных сигналов. Отсчеты входных сигналов с вторых выходов блоков дельта-модуляторов 1 и 2, в виде ш-разря- дного кода, поступают на входы первого 16 и второго 17 блоков регистров памяти. Блоки 16 и 17 обеспечивают прореживание и запоминание на время Т указанных оцифрованных отсчетов под воздействием переднего фронта импульсов, поступающих с второго тактового выхода блока синхронизации длительностью Тд и с частотой повторения Т

В блоках регистров 19 и 20 памяти, под воздействием переднего фронта импульсов, поступающих через элемент

18 задержки с второго выхода блока 15 синхронизации, происходит запоминание т-разрядных двоичных отсчетов, поступающих с выходов блоков 5 и 6, на время, равное периоду Т. Время задержки сигнала в блоке 18 задержки выбирается не меньше времени, необходимого для формирования накапливающими сумматорами 5 и 6 т-разрядные двоичных отсчетов и не более Т.. Выходные сигналы блоков 16 .и 17 перемножаются... блоками 9 и 10 на протяжении времени Т (Р + 1) с выходными сигналами блоков 19 и 20,поступающими через коммута - торы 7 и 8 на эхрды блоков 9 и 10 умножения. Произведения с выходов блоков 9 и 10 с периодом Т/ (Р + 1) через коммута торы 11 и 12 поступают на входы блоков 13 и 14 накопителей. Блоки 7 и 8 имеют по (Р + 1) выходов. Коммутаторы 11 и 12 имеют также по (Р + 1) выходу. В правой части схемы устройства (Р + 1) входы и выходы блоков 7 и 11 не используются, что связано с упрощением сх.емы управления коммутаторами по управляющим адресным- входам. БЛОК11 13 и 14 осуществляют суммирование и накопление элементарных произведений на протяжении длительности тактовых импульсов, поступающих из блока 15 синхронизации. Тактовый генератор 21 формирует прямоугольные

. 14 импульсы с периодом повторения Тд(Р + 1). Счетчик 22, обеспечивающий деление частоты, формирует прямоугольные импульсы с периодом повторения Тд, по передним фронтам которых обеспечивается сдвиг одноразрядного дельта-кода в регистрах сдвига 3 и 4, накопление отсчетов в т-разрядных реверсивных счетчиках накапливающих сумматоров 5 и 6, преобразование вход- ньпс сигналов в ш-разрядный и однораз- рядньй двоичные коды в дельта-модуляторах 1 и 2, Счетчик-распределитель 23, обеспечивающий деление частоты, I формирует на выходе импульсы прямоугольной формы длительностью Тд и частотой повторения Т, необходимые для управления блоками регистров 16 и 17 памяти,а такжедля управления через элемент 18 задержки записью информации в регистры памяти блоков 19 и 20. Счетчик 24 адресов формирует адреса для управления работой коммутаторов 7 и 8, 11 и 12, Счетчик распределитель 25 формирует импульсы, синхронные с импульсами адресов, под действием которых происходит суммирование содер-. жимых накопителей блоков 13 и 14 и элементарных произведений, поступаю- щих с блоков 9 и 10 умножения через коммутаторы 11 и 12.

Таким образом, левая часть предло- .женного устройства реализует функцию корреляции

N-m,

х(тл)ух((; +И1л для адвиг ов Шд е 0,1рJ , а правая - функ-

H-(mn1

цию (-m)kux(mn) для о 1 ; . I

сдвигов -р,... ,-lJ в масштабе реального -времени-и благодаря устране- кию паузы в работе блоков умножения с высоким быстродействием.

Формула изобретения

Коррелятор, содержащий два дель- та-модуля тора,. два регистра сдвига, два накапливающих сумматора, четыре коммутатора, два блока умножения, два блока накопителей, блок синхронизации, причем информационные входы первого и второго дельта-модуляторов являются соответственно первым и вторым входами коррелятора, выходы ли575 о 5 о

5

Q

с

0

5

11 4

нейной дельта-кодовой последовательности первого и второго дельта-модуляторов соединены соответственно с информационными входами соответствующих регистров сдвига, тактовые входы которых соединены с тактовыми входами первого и второго накапливающих сумматоров, первого и второго дельта- модуляторов и первым выходом блока синхронизации, кодовый выход которого соединен с управляющими входами с первого по четвертый коммутаторов, выходы первого и второго коммутаторов соединены с информационными входами соответственно первого и второго блоков накопителей, группы выходов блока синхронизации соединены с соответствующими тактовыми входами накопителей первого и второго блоков, первые входы первого и второго блоков умножения соединены соответственно с выходами третьего и четвертого коммутаторов, выходы первого и второго блоков умножения соединены соответственно с информационными входами первого и втоIрого коммутаторов, информационный

вход первого регистра сдвига соединен с первым информационным входом первого накапливающего сумматора, последующие информационные входы которого соединены с соответствующийи выходами первого регистра сдвига, выходы вто- рсго регистра сдвига соединены с со- о ветствующими информационными разрядными входами второго накапливающего сумматора, выходы разрядов первого и второго блоков накопителей являются соответственно выходами первой и второй групп коррелятора, отличающийся тем, что, с целью повьшения быстродействия, в него введены элемент задержки, че- тьфе блока регистров памяти, причем выходы разрядов двоичного кода .первого и вторсгго дельта-модуляторов соединены с информационными разрядными входами соответственно первого и второго блоков регистров памяти, выходы первого и второго регистров памяти соединены соответственно с вторым входом второго блока умножения и с вторым входом.первого блока умножения, выходы первого и. второго накапливающих сумматоров соединены соответственно с информационными вхо- дамй третьего и четвертого блоков регистров памяти, выходы которых

514257116

соединены с информационными входами входами первого и второго регистров соответственно третьего и четвертого памяти и через элемент задержки сое- коммутаторов, второй выход блока динен с тактовьми входами третьего синхронизации соединен с тактовыми с и четвертого регистров памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1985 |

|

SU1262522A1 |

| Коррелятор | 1986 |

|

SU1339584A1 |

| Коррелятор | 1988 |

|

SU1705835A1 |

| Коррелятор | 1989 |

|

SU1665386A1 |

| Адаптивный автокоррелятор | 1990 |

|

SU1774345A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1988 |

|

SU1510091A1 |

| Коррелятор | 1978 |

|

SU781820A1 |

| Цифровой коррелятор | 1985 |

|

SU1251107A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

Изобретение относится к цифровой электроизмерительной технике и предназначено для аппаратурного определения в реаиме реального времени корреляционной функции с симметричными разнополярными сдвигами случайных процессов. В известных устройствах умножение обрабатываемь1х величин осуществляется на интервалах времени, разделенных паузами, на протяжении которых производится наклонение кода на выходах накапливающих сумматоров. Наличие указанных пауз существенно снижает быстродействие известных устройств. Цель изобретения - повышением. быстродействия. Коррелятор содержит дельта-модуляторы 1,2, регистры 3, 4 сдвига, накашшвающие сумматоры 5,6, коммутаторы 7,8, 11,12, блоки 9,10 умножения, блоки 13,14 накопителей, блок 15 синхронизации, элемент задер ЖКИ.18, блоки 16,17,19,20 регист ров . Быстродействие повышается за счет устранения паузы в работе блоков умножения, при этом вычисление функции корреляции производится в масштабе реального времени. 2 ил. (Л с

Фие,2

| ЦИФРОВОЙ КОРРЕЛЯТОР | 0 |

|

SU275542A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коррелятор | 1985 |

|

SU1262522A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1986-05-11—Подача