пульсов, делитель 2 частоты (двоичньй счетчик), блок 3 сравнения кодов младших разрядов, блок 10 сравнения старших разрядов, преобразователь 4 кодов, блок 5 переноса фазового сдвига, триггер, шину 15 Код фазы, введены блок 12 вычитания, шина 16 Код поправки , блок 13 задержки, коммутатор 14, а триггер выполнен в виде D -триггера П. Блок 5 включает в себя смесители 6 и 8, фильтр 7, вьщеляющий разностную частоту (f - f/N), и фильтр 9, выделя62712

ющин суммарную частоту (f - f/N)+ + f/N3 f. Преобразователь, 4 выполняет функцию хранения кодов. Сущность изобретения заключается в том, что первая составляющая, ошибки устраняется вьиитанием из входного кода числа К, ,1,..,, N-I, а вторая составляющая устраняется задержкой импульсов, приходящих на D -вход триггера при входных кодах , допускающих возможность неправильного срабатьюания схемы . 3 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазовращатель | 1986 |

|

SU1319267A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Цифровой фазовращатель | 1975 |

|

SU544125A1 |

| Цифровой фазовращатель | 1982 |

|

SU1041957A1 |

| УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 1997 |

|

RU2119717C1 |

| Многоканальный преобразователь угол-фаза-код | 1983 |

|

SU1120385A1 |

| Преобразователь перемещения в код | 1983 |

|

SU1091205A1 |

| Преобразователь сдвига фазы в код | 1983 |

|

SU1104565A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Устройство фазирования шкалы времени электронных часов | 1990 |

|

SU1746356A1 |

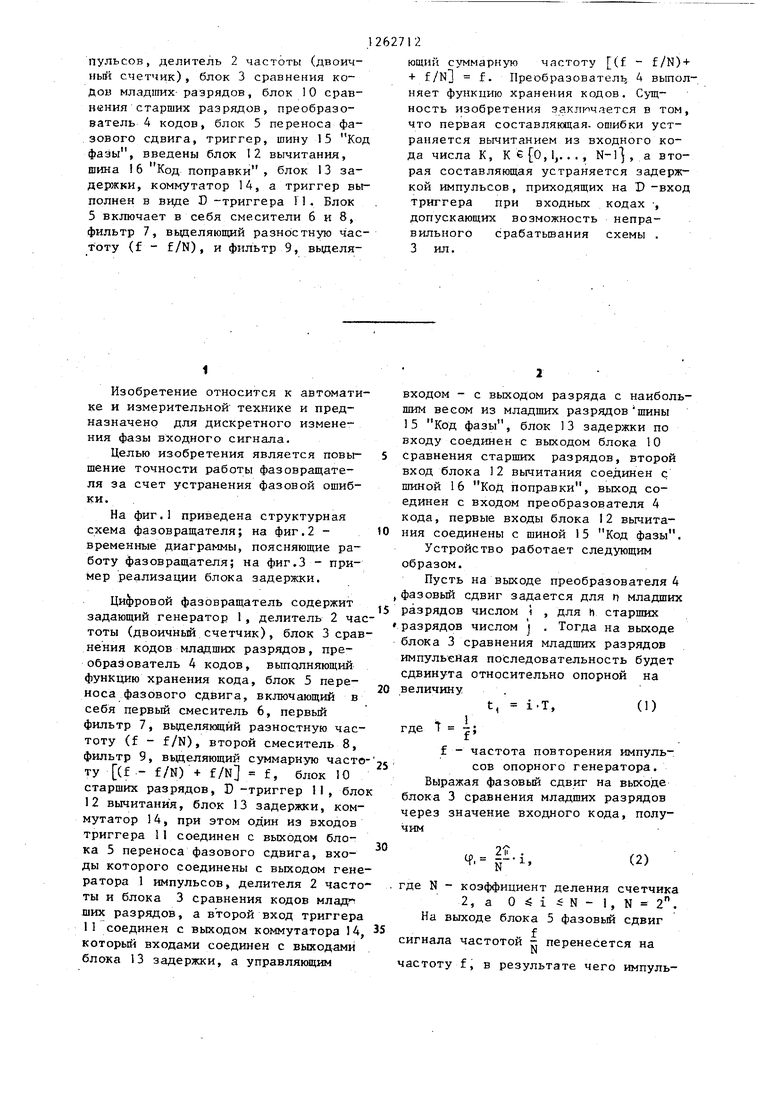

Изобретение относится к автоматике и измерительной технике. Предназначено для дискретного изменения фазы входного сигнала. Целью изобретения является повьшение точности работы фазовращателя за счет устранения фазовой ошибки. Для этого в устройство, содержащее генератор 1 имвб/Jfffd фиг.1

Изобретение относится к автомати ке и измерительной технике и предназначено для дискретного изменения фазы входного сигнала. Целью изобретения является повышение точности работы фазовращателя за счет устранения фазовой ошибки. На фиг.1 приведена структурная схема фазовращателя; на фиг.2 временные диаграммы, поясняющие работу фазовращателя; на фиг.З - пример реализации блока задержки. Цифровой фазовращатель содержит задающий генератор 1, делитель 2 ча тоты (двоичньй счетчик), блок 3 срав нения кодов младших разрядов, преобразователь 4 кодов, вьшалняющий функцию хранения кода, блок 5 переноса фазового сдвига, включающий в себя первый смеситель 6, первый фильтр 7, выделякщйй разностную частоту (f - f/N), второй смеситель 8, фильтр 9, выделяющий суммарную частв ту (.- /N) + f/N f, блок 10 старших разрядов, D -триггер II, бло 12 вычитания, блок 13 задержки, коммутатор 14, при этом один из входов триггера 11 соединен с выходом блока 5 переноса фазового сдвига, входы которого соединены с выходом гене ратора 1 импульсов, делителя 2 часто ты и блока 3 сравнения кодов младгт ших разрядов, а второй вход триггера 11 соединен с выходом коммутатора 14 которьш входами соединен с выходами блока 13 задержки, а управлякнцим входом - с выходом разряда с наибольшим весом из младших разрядовшины 15 Код фазы, блок 13 задержки по входу соединен с выходом блока 10 сравнения старших разрядов, второй вход блока 12 вычитания соединен с шиной 16 Код поправки, выход соединен с входом преобразователя 4 кода, первые входы блока 12 вычитания соединены с шиной 15 Код фазы. Устройство работает следующим образом. Пусть на выходе преобразователя 4 фазовый сдвиг задается для п младших разрядов числом , для h старших разрядов числом j . Тогда на выходе блока 3 сравнения младших разрядов импульсная последовательность будет сдвинута относительно опорной на величину . 1 ,Т - 1 1, t 1 где f - частота повторения импульсов опорного генератора. Выражая фазовый сдвиг на выходе блока 3 сравнения младших разрядов через значение входного кода, получим-г. где N - коэффициент деления счетчика 2, а О 4 i i N - 1, N 2. На выходе блока 5 фазовый сдвиг сигнала частотой - перенесется на частоту f, в результате чего импуль3сы на его выходе будут смещенными относительно опорных на выходе зад ющего генератора 1 на величину 1 -Т N N Аналогично иа выходе блока 10 сравнения старших разрядов получим 4. 1 Т 2 J 4. N-J j где О i j ё N - 1. Если подавать сигнал с выхода бл .ка 10 сравнения старших разрядов на 1)-вход триггера 11, а сигнал с выхо да блока 5 переноса фазового сдвига на вход синхронизации, получим сигнал на выходе, сдвинутый относитель но опорного на величину Ч t; j .Т + Выражая суммарный фазовый сдвиг на выходе триггера 11 через значени входного кода, получим , 21Г .27 2-5- ,.„ .. ( + 1м м (JN + i). Цена единицы старшего разр5{да ра на 21Г/К. Из выражения (7) видно, чт данный фазовращатель обеспечивает фазовьй сдвиг в пределах (N - 1). При Зтом обеспечивается дискрет изм нения фазы 2ir (9) при частоте выходных импульсов F i.ПО)

Однако фазовращатель при таком подключении D -триггера имеет два основных недостатка. Первый заклю чается в том, что в результате временных задержек в схеме при нулевом 55 заданяцем коде разность фаз между опорным и выходным сигналами может быть отличной от нуля. В результате

50

и при любом коде старших разрядов.

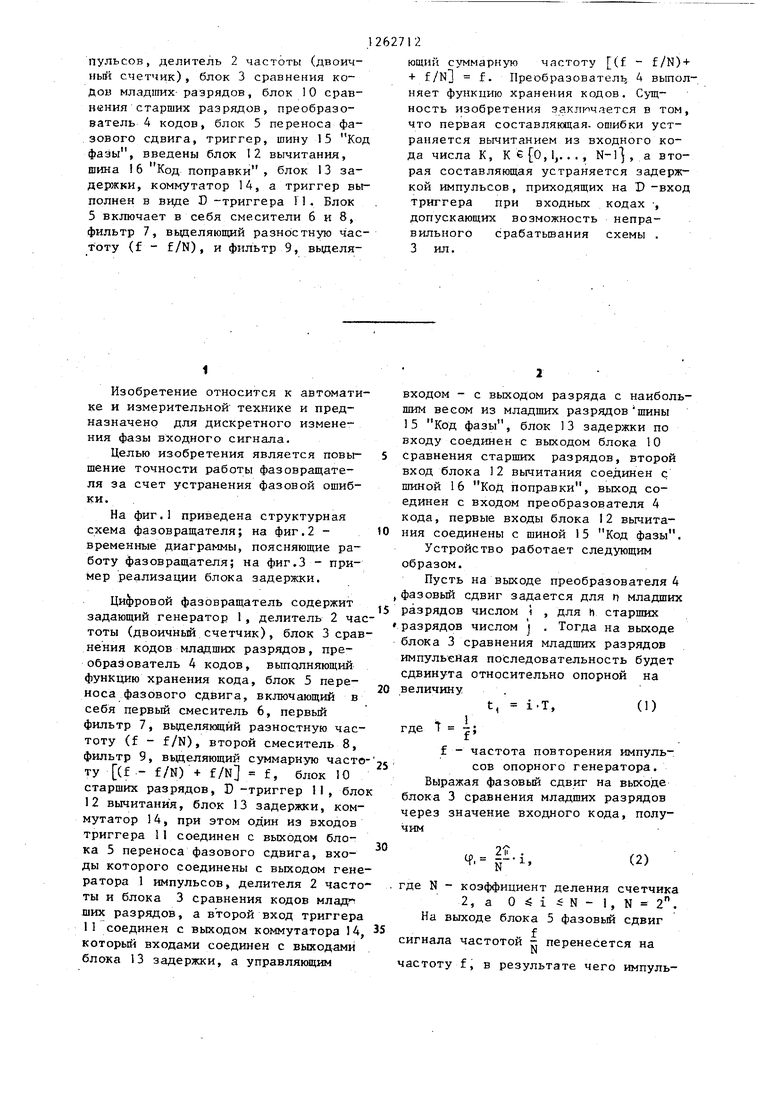

Если при кодах, значение которых определяется вьфажением (16), им-. пульсы на выходе блока 10 сравнения старших разрядов будут задержаны на величину At, причем

(17)

it Т, 124 полученньй фазовьй сдвиг qi оказывается отличным от задаваемого на Ч- :: q f (П ) Положим для определенности, что Кр ЛЧ(К -ь 1У||, где Ке 0,1,..., N - 1. Второй недостаток заключается в том, что, если временное положение фронтов импульсов, приходящих на входы D -триггера, совпадают, то схема может давать сбой. Возникшая фазовая ошибка при этом будет равна п 9ff,С -Число кодов при таких положениях им пульсов равно N. Значение кода, при котором может возникать ошибка йС| -К -ь 1, (14) будет равно Ф К + J.N. (15) При этом первая составляющая ошибки iqi принимается с точностью до млад- шего разряда. В выражении (14) она равна - К. Сущность изобретения заключается в том, что первая составляющая ошибки устраняется вычитанием из входного кода числа К, а вторая составляющая устраняется задержкой импульсов, приходящих на Б -вход триггера при входных кодах, допускающих возможность неправильного срабатывания схемы. Из формулы (15) следует, что совпадение фронтов импульсов на входах триггера 11 будет возникать при коде младших разрядов, равном i К, 5 то неоднозначность срабатьшания тр гера 1I исчезает и дополнительная фазовая погрешность возникать не будет. Проще всего получить задержку . Возможная принципиальная схема блока 13 задержки на D -триггерах приведена на фиг,3. На выходах блока 13 сигнал U,, задержан относительно U,o на Т , а сигнал 0|. на /2, что соответству ет задержке, задаваемой кодами i N 4- к и i I + К. Если вычитать из входного кода величину 1 N + К, а на D -вход триггера 11 подавать сигналы и 13 и QI-J таким образом, ч NII при 1 - -(- к подается U,, ; . NI при 1 + К подается U, ., то неоднозначность устраняется и д полнительной фазовой ошибки не буд Вычитанием из взводного кода кр не величины К величины N компенсир ется задержка U|, и и, наТ . Для унравления коммутатором 14 можно использовать самый старший р ряд кода младших разрядов, поскол его вес равен N/2. . Число К находится опытньм путе при отладке фазовращателя.. 126 Формула изобретения Цифровой фазовращатель, содержащий генератор импульсов, подключенный к входу делителя частоты, первые входы которого соединены соответственно с первыми входами блока сравнения кодов младших разрядов и с первыми входами блока сравнения кодов старших разрядов, вторые входы которых соединены соответственно с выходами преобразователя кодов, второй выход делителя частоты подключен к первому входу блока переноса фазового сдвига, второй вход которого соединен с выходом генератора импульсов , третий - с вьгходом блока сравнения кодов младших разрядов, а выход - со счетным входом триггера, шину Код фазы, отлич ающийс я тем, что, с целью повьш1ения точности,- в него введены блок вычитания, шина Код поправки, блок задержки, коммутатор, а триггер выполнен в виде D -триггера, D -вход которого соединен с выходом коммутатора, входы которого соединены с выходами блока задержки,входы которого подключены соответственно к выходу генератора импульсов и выходу блока сравнения кодов старших разрядов, при этом управляющий входкоммутатора подключен к разряду с наибольшим весом из младших разрядов шины Код фазы, которая соединена соответст-венно с первыми входами блока вычи- : тания, вторые входы которого подключены к шине Код поправки, а вход блока вычитания соединен с входом : преобразователя кодов.

фиг.З

| Цифровой фазовращатель | 1972 |

|

SU474102A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой фазовращатель | 1975 |

|

SU544125A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Код qjasbf | |||

Авторы

Даты

1986-10-07—Публикация

1984-11-23—Подача