Изобретение относится к приборостроению и измерительной технике, предназначено для фазирования шкалы времени автономных приборов и может найти широкое применение в синхронизируемых вторичных часах.

Целью изобретения является повышение точности фазирования шкалы времени.

В предлагаемом устройстве после остановки и обнуления основного счетчика-делителя происходит его пуск внешней эталонной метки времени (ЭМВ). При этом временной дискриминатор сравнивает взаимное положение ЭМВ и выходного импульса устройства и вырабатывает сигнал ошибки, который поступает на дополнительный счетчик, переключающий (через первый сумматор) на коммутаторе отводы линии задержки. Таким образом, удается осуществить компенсацию начального фазового сдвига выходных импульсов устройства и ЭМВ вызванного задержкой срабатывания основного счетчика-делителя. Данный режим работы устройства называется калибровкой. Обработка младших и старших кодов поправки разрешает устройство управления только после проведения калибровки. При этом значение младших разрядов кода поправки и значение калибровочной поправки, записанной в дополнительном счетчике, складываются на первом сумматоре. Таким образом, удается повысить реализуемую предлагаемым устройством точность фазирования шкалы времени за счет исключения погрешности, вызванной задержкой тракта деления частоты.

Введенная совокупность признаков с указанной целью в известных источниках информации не обнаружены, что свидетельствует о существенности отличий предложенного технического решения.

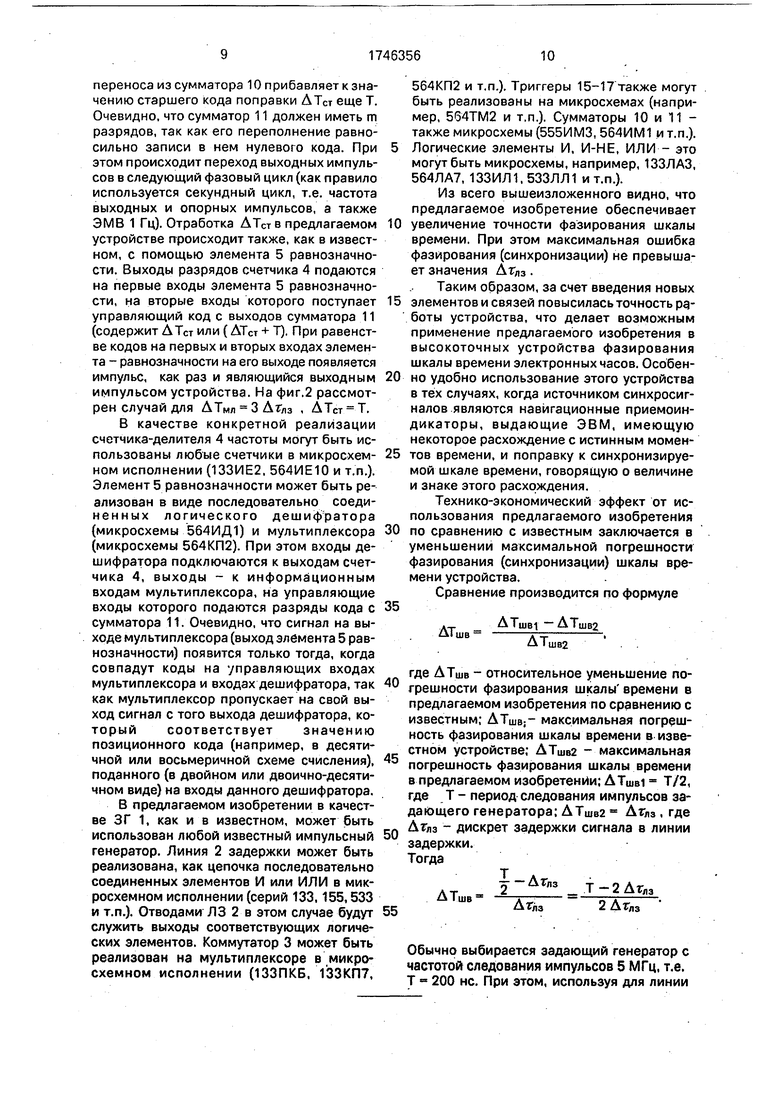

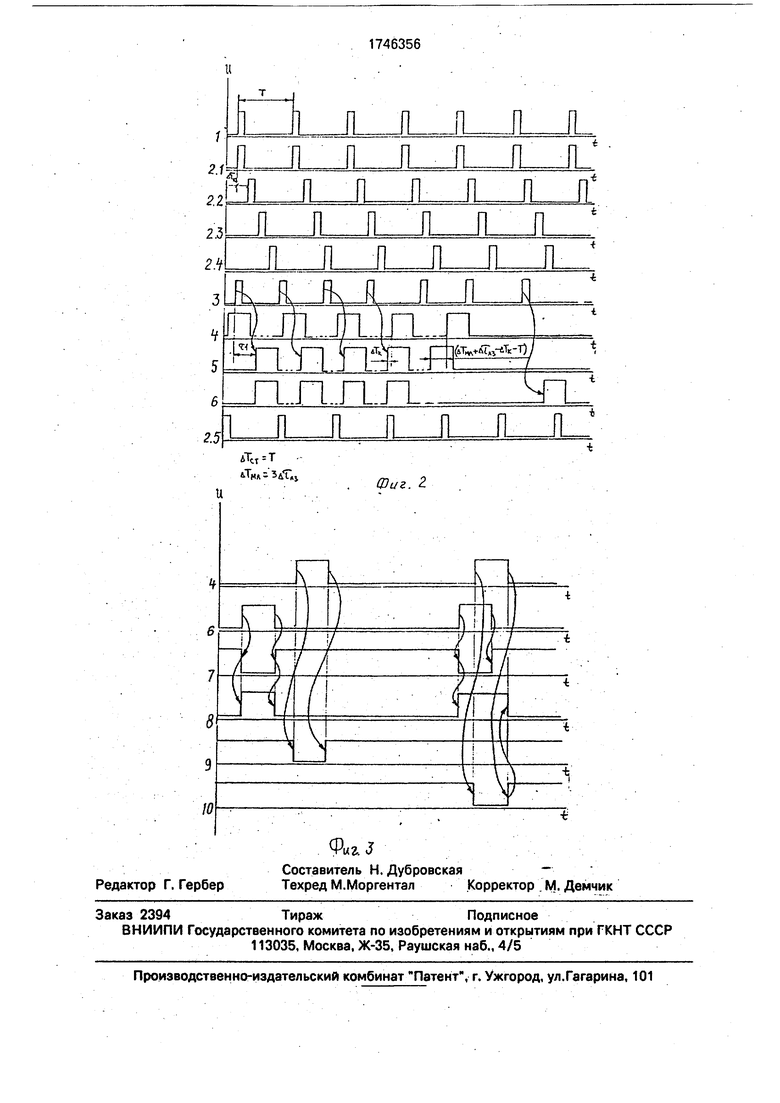

На фиг.1 приведена функциональная схема предлагаемого изобретения;на фиг. 2- диаграммы работы предлагаемого го изобретения; на фиг.З - диаграммы работы временного дискриминатора устройства.

Устройство содержит задающий генератор (ЗГ) 1 линию 2 задержки (ЛЗ) с отводами, коммутатор 3, счетчик-делитель 4 частоты, элемент 5 равнозначности, временной дискриминатор (ВД) 6, элемент ИЛИ 7, элемент И 8, входящие в состав устройства 9 управления, первый логический сумматор 10, второй логический сумматор 11, дополнительный счетчик 12, группу из п элементов И13, группу из (т+1) элементов И 14, RS-триггер 15. В состав устройства управления входят первый D-триггер 16. второй D-триггер 17, дополнительный элемент ИЛИ 18. В состав временного дискриминатора входят первый элемент И-НЕ 19,

второй элемент И-НЕ 20, третий элемент И-НЕ 21, четвертый элемент И-НЕ 22.

В рассматриваемом устройстве фазирования шкалы времени выход ЗГ 1 соединен

с входом ЛЗ 2, отводы которой подключены к соответствующим информационным входам коммутатора 3, выход которого соеди- рен с тактовым входом счетчика 4, а управляющие входы - с соответствующими

0 выходами первого сумматора 10. Выходы счетчика 4 соединены с соответствующими первыми входами элемента 5 равнозначности, при этом выход старшего разряда счетчика 4 является выходом опорных

5 импульсов устройства. Вторые входы элемента 5 равнозначности подключены к соответствующим выходам второго логического сумматора 11, а выход является выходом устройства и соединен с первым входом

0 элемента И-НЕ 19, являющимся первым входом временного дискриминатора 6. Входы младшего кода поправки устройства соединены с первыми входами группы из п элементов И 13, вторые входы этой группы

5 элементов объединены с вторыми входами группы из (т+1) элементов И 14 и подключены к выходу элемента И 8, являющемуся третьим выходом устройства 9 управления и соединенному с вторыми входами элемен0 тов ИЛИ 7 и 18. Выходы группы из п элементов И 13 соединены с соответствующими входами первого слагаемого числа первого сумматора 10, входы второго слагаемого числа которого соединены с соответствую5 щими выходами дополнительного счетчика 12, а выход переноса - с вторым входом (т+1)-го элемента из группы (т+1) элементов И 14. Первый вход дополнительного счетчика 12 соединен с выходом элемента

0 ИЛИ 7, являющимся первым выходом устройства 9 управления, второй вход счетчика 12 подключен к второму выходу устройства 9 управления, в качестве которого используется выход элемента ИЛИ 18, первый вход

5 которого является вторым входом устройства 9 управления и соединен с С-входом триггера 17, выходом элемента И-НЕ 21, являющимся вторым выходом ВД 6, третьим входом элемента И-НЕ 20 и первым входом

0 элемента И-НЕ 22. Первым входом устройства 9 управления является объединение С- входа триггера 16 и первого входа элемента ИЛИ 7, подключенное к первому выходу ВД 6, в качестве которого поступает выход эле5 мента И-НЕ 20, соединенный с вторым входом элемента И-НЕ 19, выход которого подключен к первому входу элемента И-НЕ 20 и к второму входу элемента И-НЕ 22, выход которого соединен с вторым выходом элемента И-НЕ 21. Инверсные выгерое 16 и 17 соединены с первым и вторым входами элемента И 8 соответственно, D- входы обоих триггеров подключены к общей шине устройства, а S-входы - к командному входу устройства и к S-входу триггера 15, R-вход которого соединен с входом эталонной метки времени (ЭВМ) устройства, с вторым входом ВД 6, который представляет собой объединение второго входа элемента И-Н Е 20 и первого входа элемента И-Н Е 21. Выход триггера 15 подключен к входу сброса счетчика 4. Выход (m+1)-ro элемента из группы (т+1) элемента И 14 соединен с входом младшего разряда второго слагаемого числа второго сумматора 11, входы первого слагаемого числа этого сумматора подключены к выходам соответствующих остальных m элементов из этой группы, а первые входы этих m элементов соединены с входами старшего кода поправки устройства.

Устройство работает следующим образом.

Устройство обеспечивает изменение временного положения (фазы) импульсов выходной последовательности относитель- но ЭВМ в зависимости от величины входного кода поправки. При этом код поправки подается на устройство двумя частями. Старшие разряды этого кода обеспечивают изменение фазы выходной импульсной по- следовательности с дискретом Т, где Т - период следования импульсов ЗГ 1. Младшие разряды кода поправки несут информацию об изменении фазы выходных импульсов в пределах интервала Т-3 с дис- кретом Дтлз, где Атлз - задержка сигнала между соседними отводами ЛЗ 2.

При этом импульсы ЗТ 1 с периодом Т поступают на вход ЛЗ 2, в которой они образуют серию импупьсов, задержанных от- носительно друг друга на АгЛз(фиг.2.1. 2.2.1-2.2.5, где выбрана ЛЗ 2 с пятью отводами). ЛЗ 2 должна обеспечивать задержку входных импульсов на величину (Т - Дгяз). Импульсы с отводов ЛЗ 2 поступают на ин- формационные входы коммутатора 3, управляемого кодом с выхода первого сумматора 10. Выходные импульсы коммутатора (фиг.2 и 3) поступают на тактовый вход счегчика-делителя 4 частоты.

С приходом сигнала на командный вход устройства фазирования триггер 15 устанавливается по S-входу в логическую 1 по входу и запрещает счет в счетчике-делителе 4, одновременно обнуляя его содержимое. При этом D-триггеры 16 и 17 устанавливаются по своим S-входам в логический О на инверсных выходах. Тем самым на выходе элемента И 8 устанавливается логический

О, который запрещает прохождение кодам поправки через группу из п элементов И 13 (младшая часть кода) и группу из (т+1) элементов И 14 (старшая часть кода) на сумматоры 10 и 11 элементов по вторым входам. Одновременно этот логический О поступает на вторые входы элементов ИЛИ 7 и 18, разрешая тем самым прохождение через эти элементы сигналов ошибки с выходов ВД 6 на соответствующие входы дополнительного счетчика 12.

Пришедшая на вход устройства фазирования ЭМВ, устанавливает триггер 15 по R-входу в логический О по выходу. Тем самым счетчику 4 делается разрешение на возобновление счета импульсов, идущих на него с выхода коммутатора 3. Выходы разрядов счетчика 4 подаются на первые входы элемента 5 равнозначности, на вторые выходы которого поступает код с выходов второго сумматора 11. При равенстве кодов на первых и вторых входах элемента 5 равнозначности на его выходе появляется импульс, содержащий относительно ближайшего предыдущего Б.ЫХОДНОГО опорного импульса на величину, определяемую кодом, идущим с выходов сумматора 11. Опор- ные импульсы снимаются с выхода старшего разряда счетчика 4. Дискрет изменения фазы выходных импульсов относительно опорных равен Т. В данном случае после возобновления счета в счетчике 4 входы сумматора 11 отключены (на них логический О, а на выходах старших разрядов второго слагаемого числа всегда логический О), поэтому на вторых входах элемента 5 равнозначности код равен нулю. При этом выходные импульсы устройства совпадают с его опорными импульсами (фиг.2.5 и 2.6). Относительно же ЭМВ обе эти импульсные последовательности сразу после возобновления счета в счетчике 4 задержаны на величину ti - задержка сигнала в счетчике (фиг.2.5 и 2.6). Чтобы повысить точность фазирования шкалы времени данным устройством необходимо скомпенсировать данную задержку еще до обработки кода поправки. Процедура компенсации задержки срабатывания тракта - деления частоты в данном устройстве фазирования называется калибровкой. Она обеспечивается следующим образом. Сразу после возобновления счета счетчика 4 ВД 6 начинает сравнивать временное положение выходных импульсов устройства и ЭМВ. ВД 6 представляет собой дискриминатор с релейной характеристикой, т.е. при любом взаимном положении выходных импульсов и ЭМВ на том или ином выходе ВД 6 будет

появляться импульсный сигнал ошибки, информирующий о необходимости сдвига выходной импульсной последовательности в ту или иную сторону относительно ЭМВ. Временные диаграммы работы ВД 6 представлены на фиг.8. Из них видно, что ВД 6 обеспечивает импульс сигнала ошибки на своем первом выходе (выход элемента И-НЕ 20) при любом взаимном расположении выходных импульсов устройства и ЭМВ, кроме случая начала ЭМВ во время действия выходного импульса, а окончания ЭМВ уже после окончания выходного импульса. В этом случае импульсы сигнала ошибки появляются на втором выходе ВД 6 (выход элемента И-НЕ 21) (фиг.3.4, 3.6, 3.9 и 3.10). Происходит это так потому, что во всех случаях расположения сравниваемых импульсов, кроме последнего, не срабатывают триггерные структуры, образованные в ВД 6 парами элементов И-НЕ 19, 20 и 21. 22. При этом ЭМВ, инвертируясь, беспрепятственно проходит на первый вход ВД 6. Во втором же случае, начинающийся раньше, выходной импульс устройства приводит к изменению состояния сначала триггера, образованного элемента И-НЁ 19 и 20 (фиг.З.6 и 3.7), что приводит к изменению состояния триггера на элементах И-НЕ 21 и 22 (фиг.З и 8). Начавшаяся позже ЭМВ, беспрепятственно проходит через элемент И-НЕ 21 на второй выход ВД 6, инвертируясь при этом (фиг.З и 10), и своим задним фронтом устанавливает оба вышеупомянутых триггера в исходное состояние.

Импульсы сигнала ошибки ВД 6 с первого и второго выходов устройства 9 управления поступают соответственно на первый и второй входы дополнительного счетчика 12. Эти входы счетчика оба являются тактовыми, при этом первый вход обеспечивает работу счетчика 12 на вычитание, а второй вход - на снижение. Очевидно, что в качестве счетчика 12 может быть использован реверсивный счетчик в микросхемном исполнении (133ИЕ7, 533ИЕ7 и т.п.), имеющий два тактовых входа. С приходом каждого импульса сигнала ошибки на тот или иной вход счетчика 12 его состояние меняется на единицу значения его выходного кода также меняется на единицу. Этот код напрямую транслируется на выходы сумматора 10 (а, следовательно, и на управляющие входы коммутатора 3), так как на входах первого слагаемого числа сумматора 10 код равен нулю (группа из п элементов И 13 закрыта для прохождения младшего кода поправки). С изменением управляющего кода на входах коммутатора 3 на единицу в ту или иную сторону на выход этого коммутатора подключается сигнал с соседнего отвода ЛЗ 2 (относительно предыдущего отвода). Таким образом, происходит шаг за шагом сближения во времени выходных импульсов устройства и ЭМВ (фиг.2.3, 2.4 и 2.5). При этом очевидно, что сначала импульсы сигнала ошибки будут поступать только с одного выхода ВД 6 (скорее всего это будет первый выход ВД 6, мы уже рассматривали выше

почему). При этом один из D-триггеров устройства 9 управления (например, триггер 16) по первому же импульсу сигнала ошибки установится по С-входу в логическую 1 по инверсному выходу. Второй же 6-триггер

устройства 9 управления установится в логическую 1 по инверсному выходу только после того, как на другом выходе ВД 6 появится первый импульс сигнала ошибки (в рассматриваевом на фиг.2 примере на втором выходе). Появление этого импульса информирует о том, что значение расхождения фаз выходных импульсов и ЭМВ поменяло знак, т.е. что фазы (передние фронты) этих импульсов совпадают с точностью до Аглэ,

а так как это предельно возможная точность фазирования в данном устройстве, то процедуру калибровки можно прекратить (фиг.2.5, гдеЛТк-погрешность калибровки, AT АГдз). При этом на выходе элемента

И 8 появляется логическая 1, открывающая группу из п элементов И 13 для прохождения младшего кода поправки на входы первого слагаемого числа сумматора 10. Группа из (т+1) элементов И 14 открывается

для прохождения старшего кода поправки и сигнала переноса сумматора 10 на соответствующие входы первого и второго слагаемого числа сумматора 11. С этого момента выходной импульс устройства и его опорный импульс перестают совпадать (фиг.2.5 и 2.6). Опорный сигнал сдвигается относительно ЭМВ на величину ( ДТМл + Аглз - АТК. Здесь А Тмл - значение кода младшей поправки. В это выражение может также

входить составляющая (-Т) в том случае, когда сумма значений кода счетчика 12 и младшего кода поправки переполнит разрядную сетку (п-разрядов) сумматора 10. При этом на выходе переноса сумматора 10 появляется сигнал, поступающий через (т+1) элемент И из группы 14 на вход младшегр разряда второго слагаемого числа сумматора 11 (фиг.2.5, где как раз случай с переносом в сумматор 11 и фазовое расхождение

опорных импульсов и ЭМВ равно (АТМл + + Дтлз - АТК - Т. Выходной сигнал устройства (фиг.2.6) сдвигается относительно ЭМВ на полное значение поправки (ДТСт + АТМЛ + + ДГлз - АТК). При этом наличие

переноса из сумматора 10 прибавляет к значению старшего кода поправки АТСт еще Т. Очевидно, что сумматор 11 должен иметь m разрядов, так как его переполнение равносильно записи в нем нулевого кода. При этом происходит переход выходных импульсов в следующий фазовый цикл (как правило используется секундный цикл, т.е. частота выходных и опорных импульсов, а также ЭМВ 1 Гц). Отработка АТСтВ предлагаемом устройстве происходит также, как в известном, с помощью элемента 5 равнозначности. Выходы разрядов счетчика 4 подаются на первые входы элемента 5 равнозначности, на вторые входы которого поступает управляющий код с выходов сумматора 11 (содержит ДТст или (АТСт + Т). При равенстве кодов на первых и вторых входах элемента - равнозначности на его выходе появляется импульс, как раз и являющийся выходным импульсом устройства. На фиг.2 рассмотрен случай для АТмл ЗАгЛз , АТСт Т.

В качестве конкретной реализации счетчика-делителя 4 частоты могут быть использованы любые счетчики в микросхемном исполнении (133ИЕ2, 564ИЕ10 и т.п.). Элемент 5 равнозначности может быть реализован в виде последовательно соединенных логического дешифратора (микросхемы 564ИД1) и мультиплексора (микросхемы 564КП2). При этом входы дешифратора подключаются к выходам счетчика 4, выходы - к информационным входам мультиплексора, на управляющие входы которого подаются разряды кода с сумматора 11. Очевидно, что сигнал на выходе мультиплексора (выход элемента 5 равнозначности) появится только тогда, когда совпадут коды на управляющих входах мультиплексора и входах дешифратора, так как мультиплексор пропускает на свой выход сигнал с того выхода дешифратора, который соответствует значению позиционного кода (например, в десятичной или восьмеричной схеме счисления), поданного (в двойном или двоично-десятичном виде) на входы данного дешифратора.

В предлагаемом изобретении в качестве ЗГ 1, как и в известном, может быть использован любой известный импульсный генератор. Линия 2 задержки может быть реализована, как цепочка последовательно соединенных элементов И или ИЛИ в микросхемном исполнении (серий 133,155,533 и т.п.). Отводами ЛЗ 2 в этом случае будут служить выходы соответствующих логических элементов. Коммутатор 3 может быть реализован на мультиплексоре в микросхемном исполнении (133ПКБ, 133КП7,

564КП2 и т.п.). Триггеры 15-17 также могут быть реализованы на микросхемах (например, 564ТМ2 и т.п.). Сумматоры 10 и 11 - также микросхемы (555ИМЗ, 564ИМ1 и т.п.).

Логические элементы И, И-НЕ, ИЛИ - это могут быть микросхемы, например, 133ЛАЗ, 564ЛА7, 133ИЛ1.533ЛЛ1 и т.п.).

Из всего вышеизложенного видно, что предлагаемое изобретение обеспечивает

0 увеличение точности фазирования шкалы времени. При этом максимальная ошибка фазирования (синхронизации) не превышает значения Дтлз

Таким образом, за счет введения новых

5 элементов и связей повысилась точность работы устройства, что делает возможным применение предлагаемого изобретения в высокоточных устройства фазирования шкалы времени электронных часов. Особен0 но удобно использование этого устройства в тех случаях, когда источником синхросигналов являются навигационные приемоин- дикаторы, выдающие ЭВМ, имеющую некоторое расхождение с истинным момен5 тов времени, и поправку к синхронизируемой шкале времени, говорящую о величине и знаке этого расхождения.

Технико-экономический эффект от использования предлагаемого изобретения

0 по сравнению с известным заключается в уменьшении максимальной погрешности фазирования (синхронизации) шкалы времени устройства.

Сравнение производится по формуле

5

А ДТШв1 - ДТшвз

iilujB- ,

А I шв2

где АТшв - относительное уменьшение по- 0 грешности фазирования шкалы времени в предлагаемом изобретения по сравнению с известным; ДТшв;- максимальная погрешность фазирования шкалы времени в известном устройстве; ДТШв2 - максимальная погрешность фазирования шкалы времени в предлагаемом изобретении; АТШв1 Т/2, где Т - период следования импульсов задающего генератора; ДТшва Атлз , где Аглз - дискрет задержки сигнала в линии

5

0

задержки. Тогда

AT,

5

шв

f-Aii

ЛЗ

Т - 2 Аг,

ЛЗ

ATI

лз

2Дг,

ЛЗ

Обычно выбирается задающий генератор с частотой следования импульсов 5 МГц, т.е. Т 200 не. При этом, используя для линии

задержки элементы микросхем ТТЛ серий, можно получить Аглз m 10 не. Тогда АТШв - 9.

Таким образом, за счет применения предлагаемого изобретения можно снизить погрешность фазирования шкалы времени электронных часов в девять раз.

Формула изобретения Устройство фазирования шкалы време- ни электронных часов, содержащее задающий генератор, линию задержки, коммутатор, счетчик-делитель частоты, элемент равнозначности, временной дискриминатор и элементы ИЛИ и И, при этом выходы линии задержки соединены с информационными входами коммутатора, а выходы счетчика-делителя частоты - с первыми входами элемента равнозначности, выход старшего разряда счетчика является выходом опорных импульсов устройства, отличающееся тем, что, с целью повышения точности фазирования шкалы времени, в него введены первый и второй логические сумматоры, группа из п элемен- товИ, группа из (т+1) элементов И, RS-триг- гер, дополнительный счетчик и устройство управления, первый и второй входы которого соединены с первым и втором выходами временного дискриминатора соответствен- но, а третий вход - с S-входом RS-триггера и с командным входом устройства фазирования, при этом первый выход устройства управления подключен к первому входу дополнительного счетчика, а второй выход соответственно к второму входу дополнительного счетчика, третий выход устройства управления соединен с вторыми входами группы из п элементов И и вторыми входами группы из (т+1) элементов И, первые входы группы из п элементов И являются входами младших разрядов кода поправки устройства, а тп первых входов группы из (т+1) элементов И - входами старших разрядов кода поправки устройства, а первый вход (т+1) элемента И подключен к выходу перекоса первого логического сумматора, остальные выходы которого соединены с управляющими входами коммутатора, выход которого соединен с тактовым входом основного счетчика-делителя частоты, вход обнуления которого подключен к выходу RS-триггера, R-вход которого является входом эталонной метки времени устройства и соединен с вторым входом временного дискриминатора, первый вход которого подключен к выходу

элемента равнозначности, соединенному с выходом устройства, выходы дополнительного счетчика подключены к соответствующим входам второго слагаемого числа первого логического сумматора, входы первого слагаемого числа которого соединены с соответствующими выходами группы из п элементов И, а выходы m элементов И группы из (т+1) элемента соединены с входами первого слагаемого числа второго логического сумматора, выход (т+1) элемента И из этой группы подключен к входу младшего разряда второго слагаемого числа второго логического сумматора, а выходы этого сумматора соединены с соответствующими вторыми входами элемента равнозначности, выход задающего генератора соединен с входом линии задержки, а устройство управления содержит элементы ИЛИ, И, первый и второй D-триггеры и дополнительный элемент ИЛИ, выход которого является вторым выходом устройства управления, первый вход - вторым входом устройства управления и соединен с С-входом второго D-триггера, а второй вход соединен с вторым входом основного элемента ИЛИ, с выходом элемента И и является третьим выходом устройства управления, первый вход основного элемента ИЛИ является первым входом устройства управления и соединен с С-входом первого D-триггера, а выход является первым выходом устройства управления, третий вход которого является обьединением S-входов первого и второго О-триггеров, D-входы которых соединены с общей шиной устройства, а инверсные выходы подключейы соответственно к первому и второму входам элемента И, временной дискриминатор содержит первый, второй, третий и четвертый элементы И-НЕ, первый вход первого элемента И-НЕ является первым входом временного дискриминатора, второй вход первого элемента И-НЕ соединен с выходом второго элемента И-НЕ и является первым выходом дискриминатора, а выход первого элемента И-НЕ соединен с первым входом второго элемента И-НЕ и вторым входом четвертого элемента И-НЕ, первый вход которого подключен к выходу третьего элемента-И-НЕ, к третьему входу второго элемента И-НЕ и второму выходу дискриминатора, а выход - к второму входу третьего элемента И-НЕ, первый вход которого является вторым входом дискриминаг тора и соединен с вторым входом второго элемента И-НЕ.

Jl-JLJLJlIL

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2000 |

|

RU2173934C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Цифровой фазовращатель | 1982 |

|

SU1041957A1 |

| Устройство для кодирования угла поворота | 1988 |

|

SU1644376A1 |

| Устройство для извлечения квадратного корня | 1983 |

|

SU1113799A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

Изобретение относится к приборостроению и измерительной те хнике и предназначено для фазирования шкалы времени автономных приборов. В частности, оно может найти широкое применение в синхрони- зируемых вторичных часах. Сущность изобретения: в устройство фазирования шкалы времени электронных часов, содержащее задающий генератор 1, линию 9. задержки, счетчик-делитель 4 частоты, элемент 5 равнозначности, временной дискриминатор 6, элементы ИЛИ 7 и И 8, коммутатор 3, введены первый 10 и второй 11 логические сумматоры, группа из п элементов И 13, группа из т+1 элементов И 14, RS-триггер 15, дополнительный счетчик 12 и устройство 9 управления. 3 ил. } с & 2 О СА СЛ О

, П П П П П П П

ППППППП

ATCT:T

Фиг-J

Редактор Г. Гербер

Составитель Н.Дубровская

Техред М.МоргенталКорректор . М. Демчик

Фиг. 2.

| Устройство для синхронизации часов | 1978 |

|

SU732793A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровой фазовращатель | 1984 |

|

SU1213434A1 |

| Видоизменение пишущей машины для тюркско-арабского шрифта | 1923 |

|

SU25A1 |

| Устройство фазирования шкалы времени электронных часов | 1982 |

|

SU1084720A1 |

| кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство синхронизации | 1984 |

|

SU1223390A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство компенсации сдвига частот | 1985 |

|

SU1316097A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Цифровой фазовращатель | 1982 |

|

SU1041957A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| 0atSr лопро&и | |||

Авторы

Даты

1992-07-07—Публикация

1990-10-02—Подача