CD 01

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство фазирования шкалы времени электронных часов | 1990 |

|

SU1746356A1 |

| Цифровой фазовращатель | 1984 |

|

SU1262712A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Устройство для считывания графической информации | 1986 |

|

SU1481813A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Преобразователь угол-код | 1988 |

|

SU1596461A1 |

| Многоканальный преобразователь угол-фаза-код | 1983 |

|

SU1120385A1 |

| Цифровой фазовращатель | 1988 |

|

SU1525616A1 |

| Устройство синхронизации фаз сигналов двух генераторов | 1978 |

|

SU771886A1 |

ЦИФРОВОЙ ФАЗОВРАЩАТЕЛЬ, ; содержащий задающий генератор, элемент задержки, элемент И, коммутатор и счетчик опорной фазы, вход .: которого подключен к входу элемента задержки, выходы которого соединены с входами коммутатора, отличающийся тем, что, с , целью повышения быстродействия и расширения функциональных возможностей, в него введены дополнительный комму татор, временной дискриминатор, элемент равнозначности и элемент ИЛИ, первый вход которого соединен с выходом задающего генератора, второй вход элемента ИЛИ соединен с выходом дополнительного коммутатора и первым входом временного дискриминатора, выход элемента. ИЛИ подключен к входу счетчика опорной фазы, выход старшего разряда которого соединен с шиной опорных импульсов фазовргицателя, выходы разрядов счетчика опорной фазы подключены к первым входам элемента равнозначности, вторые входы которого соединены с входными шинами старших разрядов управляющего кода фазовргоцателя, а выход элемента равнозначности подключен к первому входу элемента И, дополнительный, выход элемента задержки соединен ,с вторым в.ходом временного дискриминатора, выход которого подключен к управляющему входу дополнительного коммутатора, допрлнительные входы коммутатора соединены с входными шинами младших разрядов управляющего кода фазовращателя, выход коммутатора под-о ключей к второму входу элемента И, выход которого соединен с выходной шиной фазовращателя.

iT

Изобретение относится к радиотехнике и может быть использовано в радиолокации, радионавигации, а также в устропствах измерительной техники.

Известно устройство цифрового регулирования фаз в широком диапазоне час;тот, содержащее регистр, расщепитель фазы, коммутатор, коммутирующие Входы которого подключены к вы ходам расщепителей фазы, а управляющий дход подключен к одному из выходов регистра, суммирующий каскад, два преобразователя код-напряжение, входы эталонных напряжений которых подключены к выходам коммутатора, а .выход каждого из преобразователей подключен к соответствующему входу суммирукйцего каскгша, выход которого является выходом устройства Ш.

Недостатками данного фазовращателя являются наличие большого чила настррниваемых злементов, .усилительных схем, резирторных делителей, необходимых для построения преобразователей код-напряжение и, следовательно, недостаточная надежность работы схемы.

Наиболее близким к предложенному по технической сущности является преобразователь код-сдвиг фазы. Содержащий задающий генератор импулсов, соединенный со счетчиком опорной фазы,.выход которого является выходом опорной последовательности, и управляемой линией задержки, выполненной в виде линии задержки с отводами, соединенной с младшими разрядами преобразуемого кода шиной и подключенной к входам двух.командного коммутатора, выходы которого соединены с входом счетчика переменной фазы, соединенного шиной поразрядно с группой вентилей старших разрядов преобразуемого кода, а выход счетчика является выходом устройства, управляющие входы коммутатора подключены к выходам схемы И, выходы которой соединены с выходами счетчика опорной фазы 2 .

Недостатками известного устройства является низкое быстродействие, связанное с тем, что изменение величины задержки в устройстве возможно только один раз за период счета счетчика опорной фазы, а также отсутствие возможности формирования пакетов задержанных импульсов.

Цель изобретения - повышение быстродействия устройства и расширение функциональных возможностей путем формирования пакета задержанных импульсов.

Поставленная цель достигается тем что в цифровой фазовращатель, содержащий задающий генератор, злемент задержки, элемент И, коммутатор и счетчик опорной фазы, вход которогоподключён к входу злемента задержки, выходы которого соединены с входами коммутатора,введены дополнительный коммутатор, временной дискриминатор, злемент равнозначности и злёмент ИЛИ, первый вход которого соединен с выходом задающего генератора, второй вход злемента ИЛИ соединен с выходом дополнительного коммутатора и первым входом временного дискриминатора, выход злемента ИЛИ подключен к входу счетчику, опорной Фаз,ы, выход старшего разряда которого соединен с шиной опорных импульсов фазовращателя, выходы разрядов счетчика опорной фазы подключены к первым входам злемента равнозначности, вторые входы которого соединены с входными шинами старших разрядов управляющего кода фазовращателя, а выход.злемента равнозначности подключен к первому входу злемента И, дополнительный выход злемента задержки соединен с вторым входом временного дискриминатора, выход которого подключен куправляювяему входу дополнительного коммутатора, дополнительные входы коммутатора соединены с входными шинами младших разрядов управляющего кода фазовращателя, выход коммутатора подключен к второму входу злемента И, выход которого соединен с выходной шиной фазовращателя.

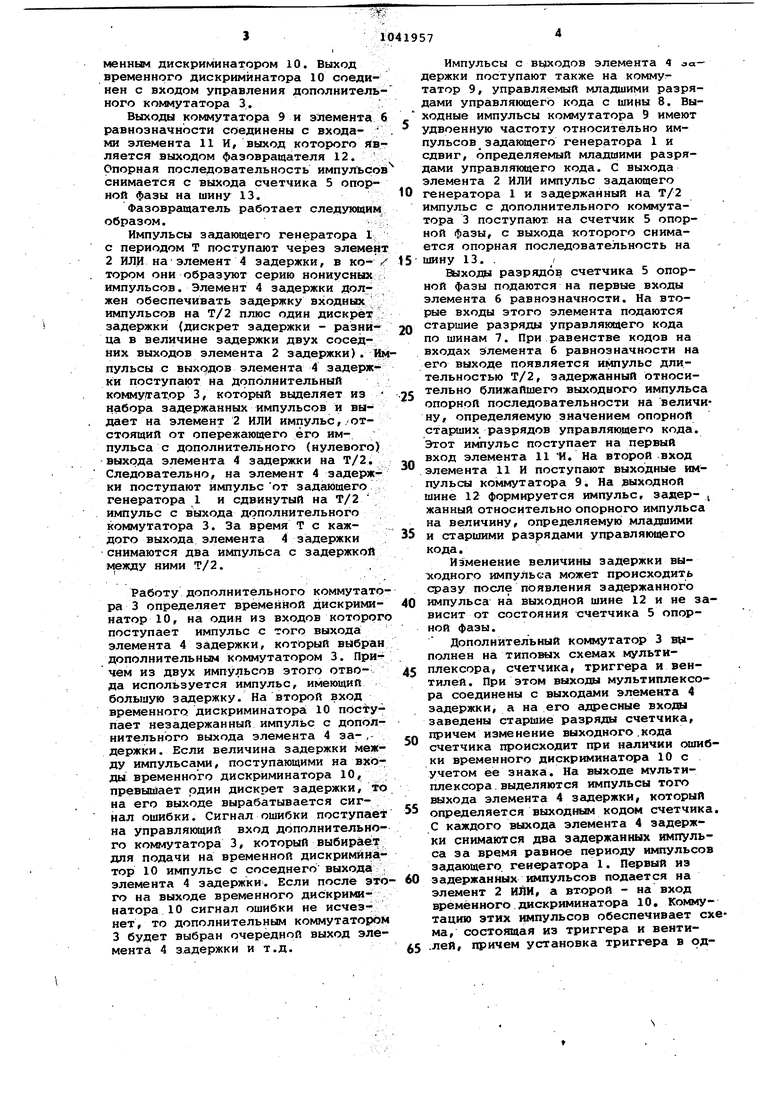

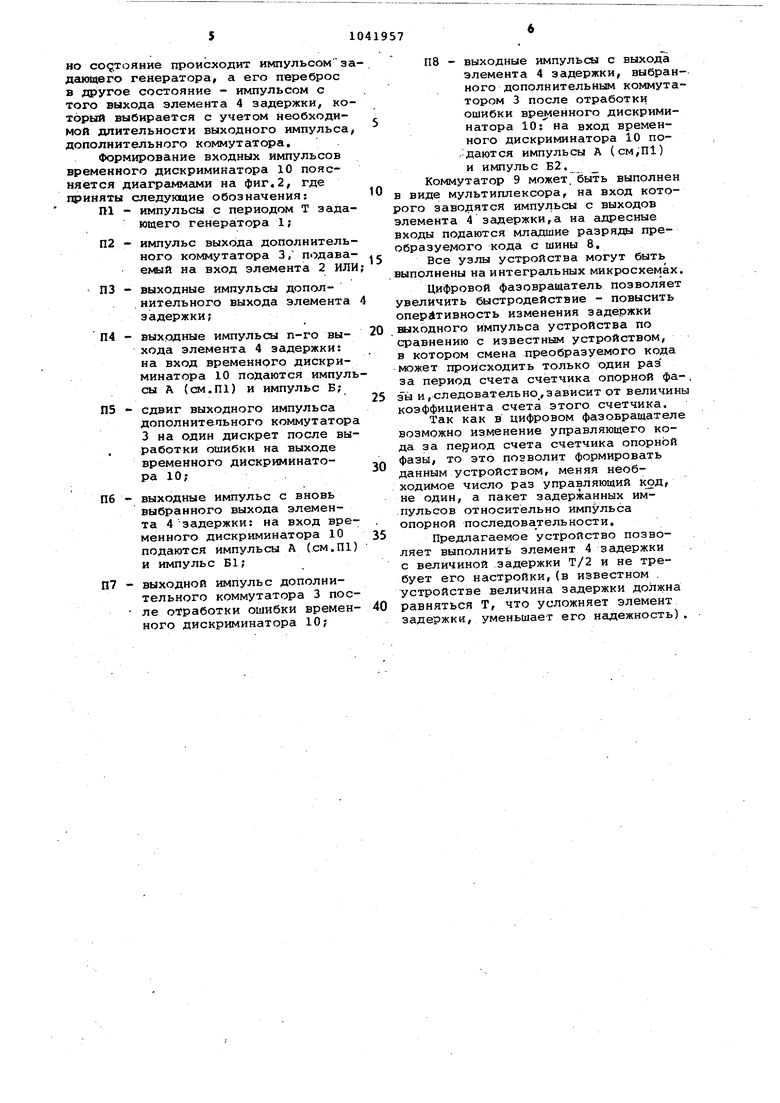

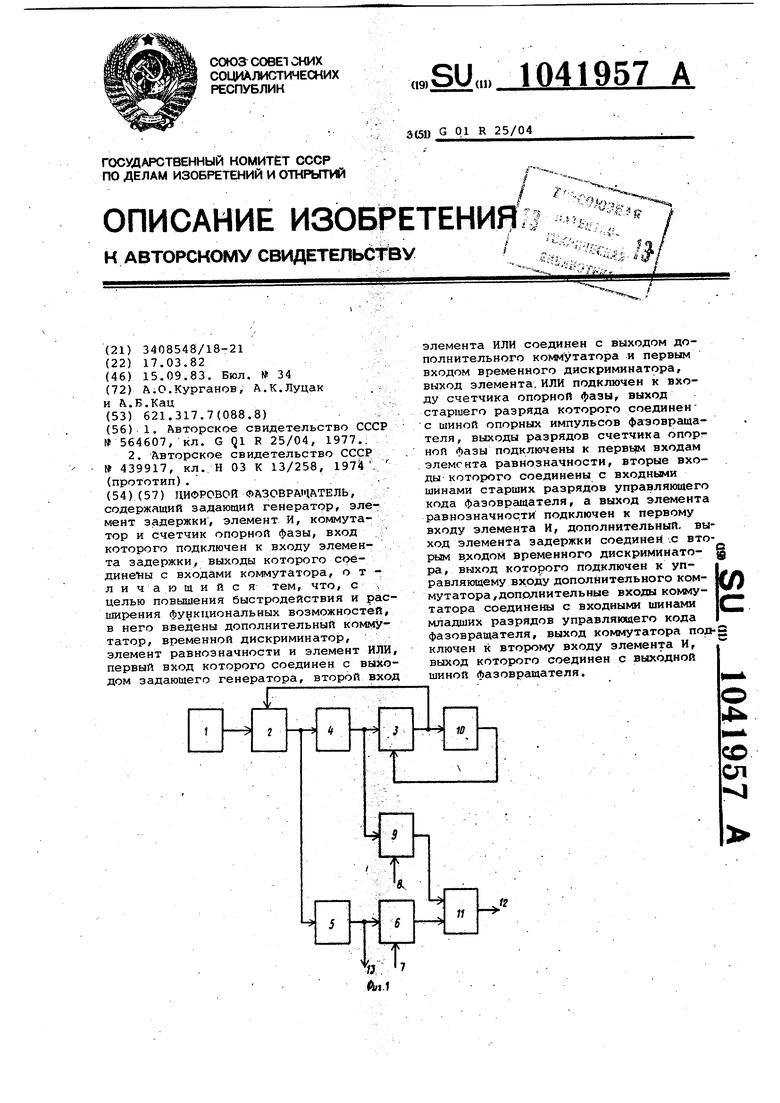

На фиг.1 приведена блок-схема фазовращателя; на-фиг.2 - временные диаграм|Ф1 формирования выходных импульсов коммутатора.

Фазовращатель содержи- задающий генератор 1, элемент 2 ИЛИ, дополнительный коммутатор 3, злемент 4 задержки, счетчик 5 опорной фазы, элемент 6 равнозначности, шины 7 и 8 старших и младших разрядов управляющего кода устройства, коммутатор 9, временной дискриминатор 10, элемент 11 И, выходную шину 12, шину 13 опорных импульсов.

Задающий генератор 1 соединен с первым входом элемента 2 ИЛИ, второй вход .которого соединен с выходом дополнительного коммутатора 3, а выход соединен с элементом 4 задержки и счетчиком 5 опорной фазы, выходы разрядов которого соединены с первыми входами элемента 6 равнозначности, другие входы которого соединены поразрядно шиной 7 со старшими разрядами преобразуемого кода, младшие разряды которого соединены с шиной 8 с входами коммутатора 9. Другие входы коммутатора 9 соединены с выходами элемента 4 задержки,- которые соединены также через дополнительный коммутатор 3 с вр менным дискриминатором 10. Выход временного дискриминатора 10 соединен с входом управления дополнитель ного коммутатора 3. Выходы коммутатора 9 и элемента равнозначности соединены с входами элемента 11 И, выход которого яв ляется выходом фаэовращателя 12. Опорная последовательность импульсо снимается с выхода счетчика 5 опорной фазы на шину 13. Фазовреицатель работает следующим образом.. Импульсы задающего генератора 1 с периодом Т поступают через элемен 2ИЛИ на элемент 4 задержки, в котором они образуют серию нониусных импульсов. Элемент 4 задержки должен обеспечивать задержку входных импульсов на Т/2 плюс один дискрет задержки (дискрет задержки - разиица в величине задержки двух соседних выходов элемента 2 задержки). И пульсы с выхрдов элемента 4 задержки поступают на дополнительный комму/гатор 3, который выделяет из набора задержанных импульсов и выдает на элемент 2 ИЛИ импульс,/отстоящий от опережающего его импульса с дополнительного (нулевого) выхода элемента 4 задержки на Т/2. Следовательно, на элемент 4 задержки поступают импульс от задающего генератора 1 и сдвинутый на Т/2 импульс с выхода дополнительного коммутатора 3. За время Т с каждого выхода элемента 4 задержки снимаются два импульса с задержкой между ними Т/2.. Работу дополнительного коммутато ра 3 определяет временной дискриминатор 10, на один из входов которог поступает нмпульс с того выхода элемента 4 задержки, который выбран дополнительным коммутатором 3. Причем из двух импульсов этого отвода используется импульс, имеющий большую задержку. На второй вход временного дискриминатора 10 поступает незадержанный импульс с дополнительного выхода элемента 4 за- ,держки. Если величина задержки между импульсами, поступающими на входы временного дискриминатора 10, превышает один дискрет задержки, то на его выходе вырабатывается сигнал ошибки. Сигнал ошибки поступа;е на управляющий вход дополнительно го коммутатора 3, который выбирает для подачи на временной дискримина тор 10 импульс с соседнего выхода элемента 4 задержки. Если после это го на выходе временного дискриминатора 10 сигнал ошибки не исчезнет, то дополнительным коммутаторо 3будет выбран очередной выход эле мента 4 задержки и т.д. Импульсы с выходов элемента 4 оедержки поступают также на коммугтатор 9, управляемый младшими разрядами управляющего кода с шины 8. Выходные импульсы коммутатора 9 имеют удвоенную частоту относительно импульсов згшающего генератора 1 и сдвиг, определяемый младшими разрядами управляющего кода. С выхода элемента 2 ИЛИ импульс задающего генератора 1 и задержанный на Т/2 импульс с дополнительного коммутатора 3 поступают на счетчик 5 опорной фазы, с выхода которого снимается опорная последовательность на шину 13. . у Выходы разрядов счетчика 5 опорной фазы подаются на первые входы элемента 6 равнозначности. На вторые входы этого элемента подаются старшие разряды управляющего кода по шинам 7. При равенстве кодов на входах Элемента 6 равнозначности на его выходе появляется импульс длительностью Т/2, задержанный относительно ближайшего выходного импульса опорной последовательности на величину, определяемую значением опорной старших разрядов управляющего кода. Этот импульс поступает на первый вход элемента 11 И. На второй вход элемента 11 И поступают выходные импульсы коммутатора 9. На рыходной шине 12 формируется импульс, заяержанный относительно опорного импульса на величину, определяемую младшими и старшими разрядами управляющего кода. Изменение величины задержки выходного импульса может происходить сразу после появления задержанного импульса на выходной шине 12 и не зависит от состояния хзчетчика 5 ОПОРНОЙ фазы. Дополнительный коммутатор 3 выполнен на типовых схемах мультиплексора, счетчика, триггера и вентилей. При этом выходы мультиплексора соединены с выходами элемента 4 задержки, а на его адресные входы заведены старшие разряды счетчика, причем изменение выходного .кода счетчика происходит при наличии ошибки временного дискриминатора 10 с учетом ее знака. На выходе мультиплексора выделяются импульсы того выхода элемента 4 задержки, который определяется выходным кодом счетчика. С каждого выхода элемента 4 задержки снимаются два задержанных импульса за время равное периоду импульсов задающего генератора 1. Первый из задержанных импульсов подается на элемент 2 ИЛИ, а второй - на вход временного дискриминатора 10, Коммутацию этих импульсов обеспечивает схема, состоящая из триггера и венти-лей, причем установка триггера в одно состояние происходит импульсом э дакицего генератора, а его переброс в другое состояние - импульсом с того выхода элемента 4 задержки, ко торый выбирается с учетом необходимой длительности выходного импульса дополнительного коммутатора. Формирование входных импульсов временного дискриминатора 10 поясняется диаграммс1ми на фиг. 2, где приняты следующие обозначения: Ш - импульсы с периодом Т зада ющего генератора 1; П2 - импульс выхода дополнитель ного коммутатора 3/ подава емый на вход элемента 2 ИЛ выходные импульсы допол.нительного выхода элемента задержки; выходные импульсы п-го выхода элемента 4 задержки: на вход временного дискриминатора 10 подаются импул сы А (cM.ni) и импульс Б; сдвиг выходного импульса дополнительного коммутатор 3 на один дискрет после вы работки ошибки на выходе временного дискриминатора 10; выходные импульс с вновь выбранного выхода элемента 4 задержки: на вход временного дискриминатора 10 подаются импульсы А (см.П и импульс Б1; выходной импульс дополнительного коммутатора 3 после о работки ошибки временного дискриминатора 10; П8 - выходные импульсы с выхода элемента 4 задержки, выбранного дополнительным коммутатором 3 после отработки ошибки Bpe ieHHoro дискриминатора 10: на вход временного дискриминатора 10 по- даются импульсы А (см,п1) и импульс Б2. Коммутатор 9 может, быть выполнен в виде мультиплексора, на вход которого заводятся импульсы с выходов элемента 4 задержки,а на адресные входы подаются младшие разряды преобразуемого кода с шины 8. Все узлы устройства могут быть выполнены на интегральных микросхемах. Цифровой фазовращатель позволяет увеличить быстродействие - повысить оперативность изменения задержки выходного импульса устройства по сравнению с известным устройством, в котором смена преобразуемого кода может происходить только один раз за период счета счетчика опорной фа-, зы и,следовательно,зависит от величины коэффициента счета этого счетчика. Так как в цифровом фазовращателе возможно изменение управляющего кода за период счета счетчика опорной фазы, то это позволит формировать данным устройством, меняя необходимое число раз управляющий код, не один, а пакет задержанных им.пульсов относительно импульса опорной последовательности. Предлагаемое устройство позволяет выполнить элемент 4 задержки с величиной задержки Т/2 и не требует его настройки,(в известном , устройстве величина задержки должна равняться Т, что усложняет элемент задержки, уменьшает его надежность).

т

пг

п п

пз

п J

nt

ns

П П

П6

/77

П8

л

51

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство цифрового регулирования фазы в широком диапазоне частот | 1974 |

|

SU564607A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь код-сдвиг фазы | 1972 |

|

SU439917A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| . | |||

Авторы

Даты

1983-09-15—Публикация

1982-03-17—Подача