1C

с

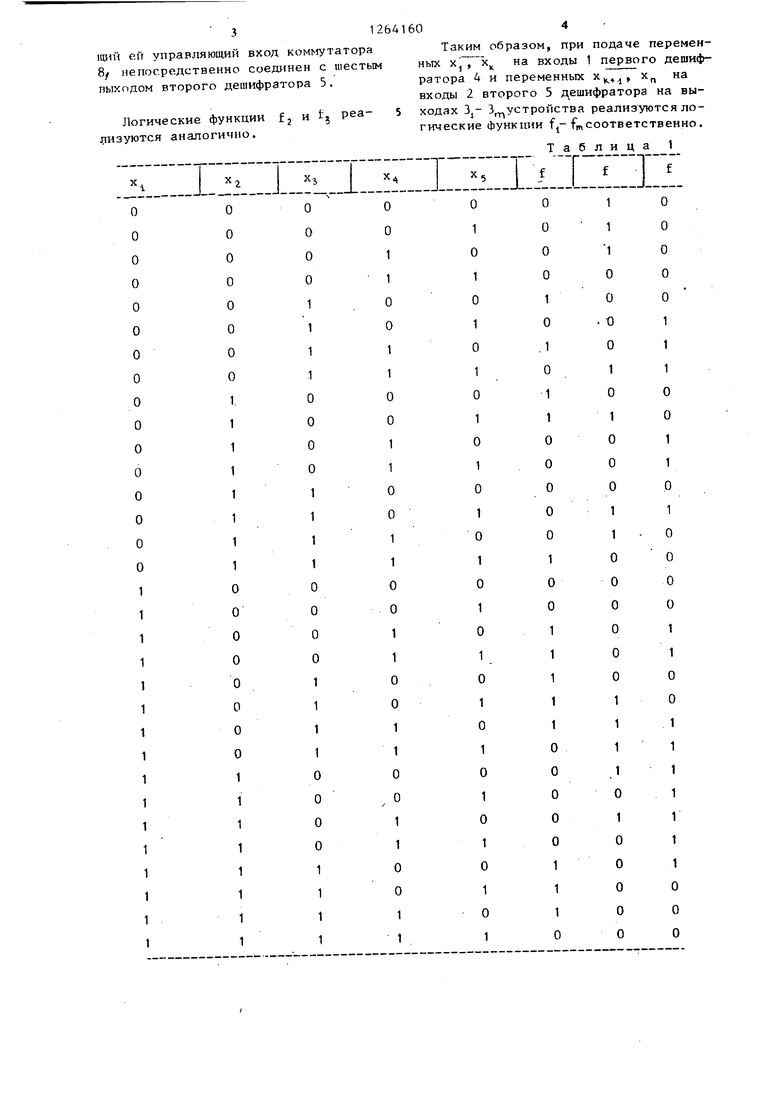

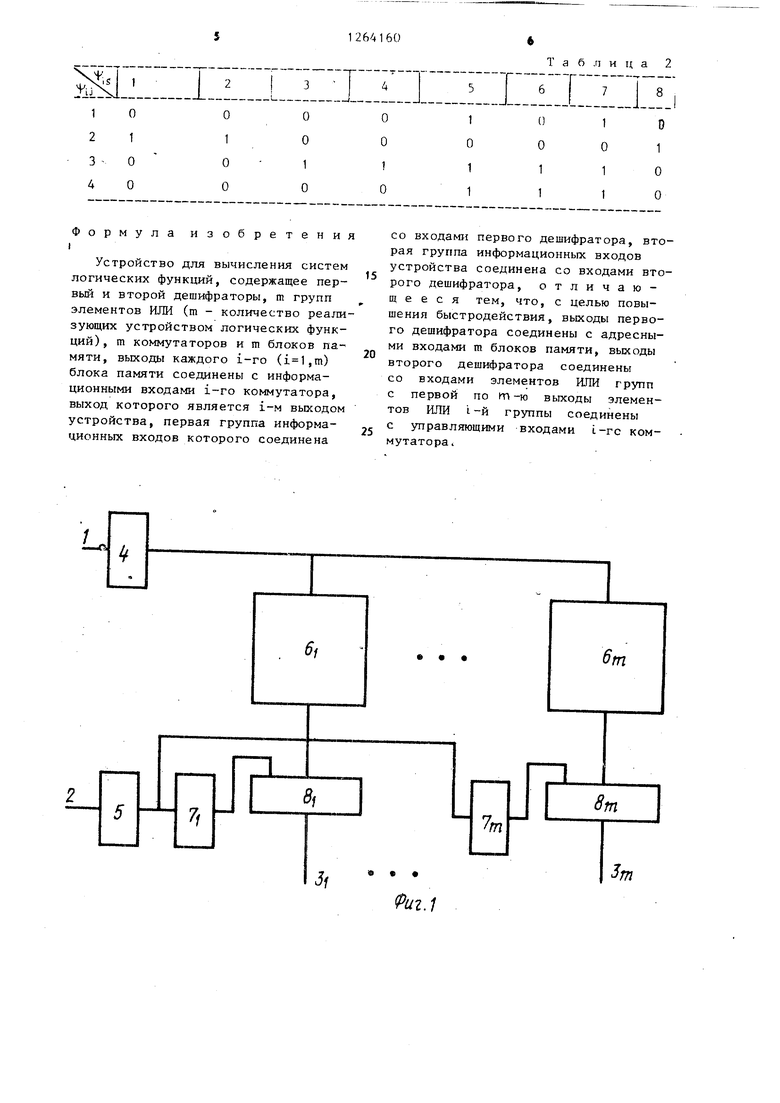

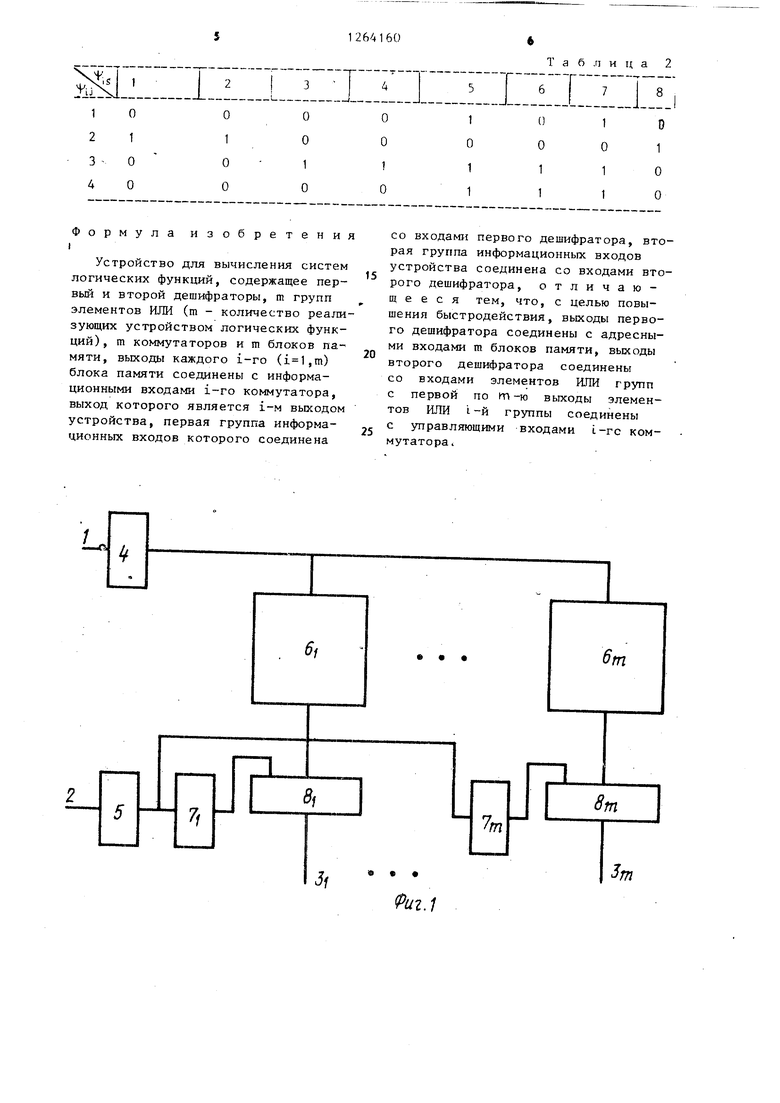

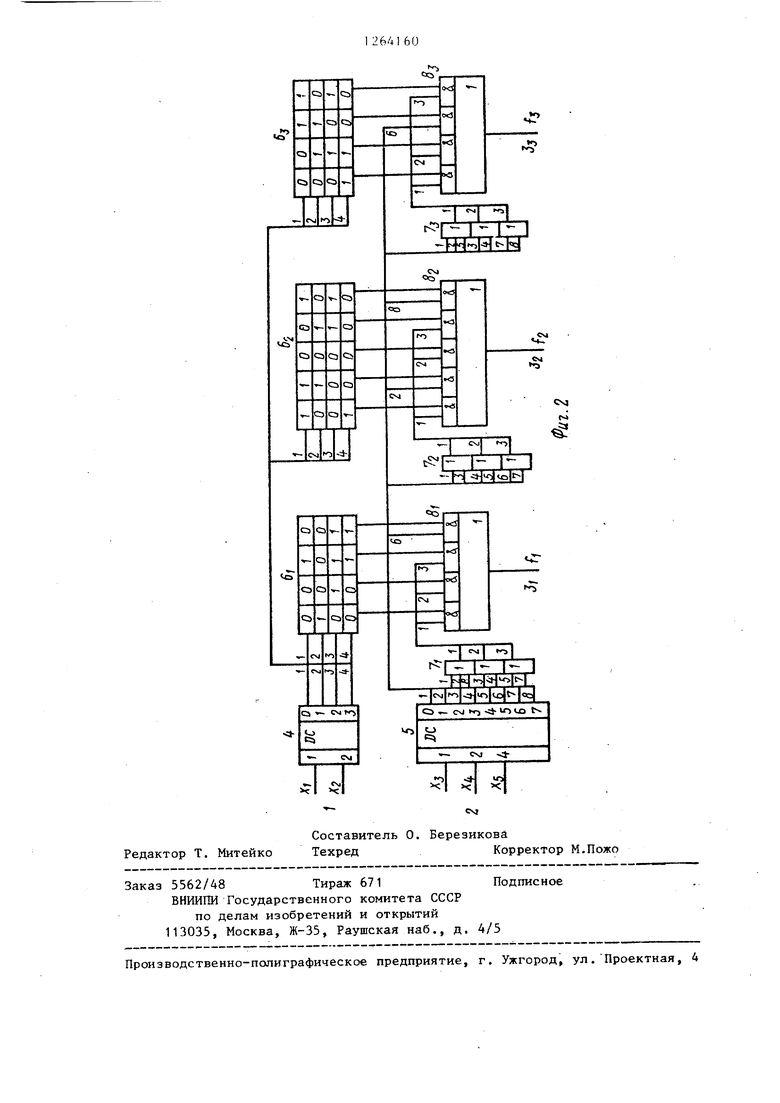

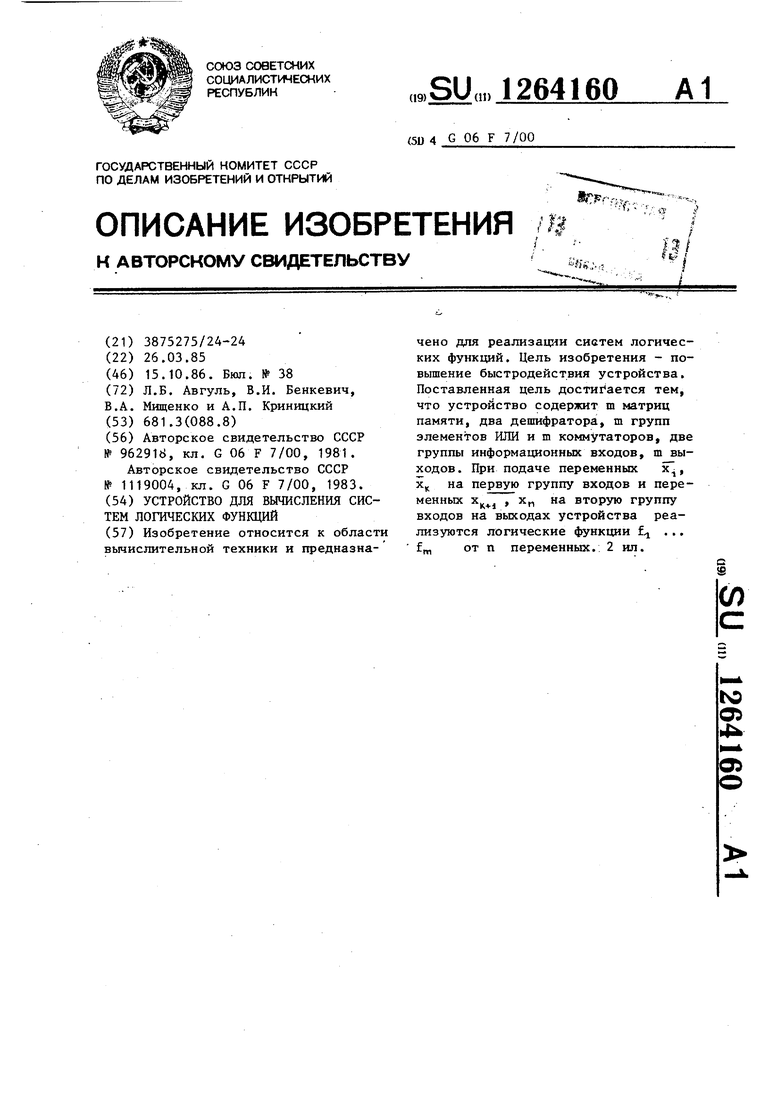

4i Изобретение относится к вычислительной технике и предназначено для реализации систем логических функций описывающих работу цифровых преобразователей. Цель изобретения - повышение быст родействия устройства для вычисления систем логических функций. На фиг.1 приведена структурная схема предлагаемого устройства; на фиг.2 - функциональная схема устройства для рассматриваемого примера Устройство содержит первую Т и вторую 2 группы информационных входов, га (по числу реализуемых устройством логических функций) выходов 3, -3т, первый 4 и второй 5 дешифраторы, га матриц памяти б - 6т, m групп элементов ИЛИ 7 - 7т и m коммутаторов 8гп. Первая 1 и вторая 2 группы информационных входов устройства соединены с входами первого 4 и второго 5 дешифраторов соответственно. Выходы первого дешифратора 4 соединены с адресными шинами матриц памяти 6i бгп, выходы которых соединены с информационными входами коммутаторов Вт соответственно. Выходы второго дешифратора 5 соединены с входами элементов ИЛИ 7 - 7, выходы KOTORsrx соединены с управляющими входами коммутаторов 8 - соответ ственно, «Выходы коммутаторов 8 - Bin являются выходами устройства Зщ Устройство работает следующим образом. Система га логических функций п переменных f (х ) , ni -разлагается по Шейному по к (к п) переменным х,, Xj. на функции п-к переменных 4iJ (ХцТТТ п) Таким образом, каждой функции f; соответствует 2 функций U , Функции Ii размещаются в памяти так, что каждая из них занимает одно слово (строку) в i-й матрице памяти. Очевидно, одноименным разрядам S ( ,) функций vfLi () (J 1,2) будут соответствовать v булевы функции .S (У) ц) каждая из которых занимает S-й столбец в i-й матрице памяти. Следовательно переменные Хц,х определяют функ цию 4is в i-й матрице, а переменные х, х( - значение выбранной функции , которое совпадает со значением 02 функции f (х, ,Хп) на данном наборе переменных х, х. Если переменные х, х подать на первый дешифратор, выход которого подключить к адресным шинам матриц памяти, переменные Xj,,n подать на второй дешифратор, выход которого подключить к управляющим входам коммутаторов, информационные входы которых соединить соответственно с выходами матриц памяти, то на выходе коммутаторов реализовываются функ ции f- (х ,х) , Однако, с целью уменьшения аппаратурных затрат все попарно тождественные функции H. V,f (S 1,, I 1, , S/1) , которым соответствуют сигналы на и выходах второго дешифратора, размещаются в памяти так, чтобы они занимали один столбец. Тогда собтветствующий управляющий вход коммутатора подключается к выходу элемента ИЛИ, входы которого соединяются с и выходами второго дешифратора. Более подробная работа предлагаемого устройства рассмотрена на примере реализации системы трех булевых функций пяти переменных (табл,1), а функциональная схема устройства для рассматриваемого примера приведена на фиг,2, Разложим f (xTTxg) по переменным (табл,2), Очевидно,.Н„ V,j S,j f (х ,х„), y., f2(x,, хг); f,,(x,, хг); Ч6 f 3 (х , X j) , Следовательно, функции У,,, 4,, У размещаются в одном столбце первой матрицы памяти 6j, выход которого подключается к информационному входу коммутатора 8, соответствующий управляющий вход которого подключен к выходу элемента ИЛИ группы 7 , входы которого соединены с первым, вто- рым и восьмым выходами второго дешифратора 5. Функции Н и H-i , и 7 также занимают по одному столбцу в матрице памяти 6j , Соответствующие управляющие входы коммутатора 8 также соединяются с выходами элементов ИЛИ группы 7 , Поскольку функция не имеет тождественной функции, то соответствую312641

1ЦНЙ ей управляющий вход коммутатора 8f непосредственно соединен с шестым

60

Таким образом, при подаче переменна входы 1 первого дешифных х, х

Т а 6 ,ri и ц а 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем логических функций | 1987 |

|

SU1432499A1 |

| Логическое запоминающее устройство | 1984 |

|

SU1359801A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Устройство для логического дифференцирования булевых функций | 1988 |

|

SU1541591A1 |

| Устройство для вычисления булевых производных | 1986 |

|

SU1370651A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1474671A1 |

| Устройство для преобразования булевых функций | 1988 |

|

SU1532946A1 |

| Магнитооптическое устройство для реализации дискретного преобразования Фурье | 1990 |

|

SU1795472A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

Изобретение относится к области вычислительной техники и предназначено для реализации систем логических функций. Цель изобретения - повышение быстродействия устройства. Поставленная цель достиг ается тем, что устройство содержит ш матриц памяти, два дешифратора, m групп элементов ИЛИ и m коммутаторов, две группы информационных входов, m выходов. При подаче переменных х, х на первую группу входов и переменных x., ) Xf, на вторую группу входов на выходах устройства реализуются логические функции f ... fm от п переменных. 2 ил.

Формула изобретения I

Устройство для вычисления систем логических функций, содержащее первый и второй дешифраторы, m групп элементов ИЛИ (т - количество реализующих устройством логических функций), m коммутаторов и m блоков памяти, выходы каждого i-ro (,m) блока памяти соединены с информационными входами i-ro коммутатора, выход которого является i-м выходом устройства, первая группа информационных входов которого соединена

6l

Si

3i

со входами первого дешифратора, вторая группа информационных входов устройства соединена со входами второго дешифратора, отличающееся тем, что, с целью повышения быстродействия, выходы первого дешифратора соединены с адресными входами m блоков памяти, выходы второго дешифратора соединены со входами элементов ИЛИ групп с первой по кп-ю выходы элементов ИЛИ i-и группы соединены с управляющими входами L-гс коммутатора.

6т

8т

Ут

т

в

(Риг.1

| Арифметико-логический модуль | 1980 |

|

SU962916A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления логических выражений @ переменных | 1983 |

|

SU1119004A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-03-26—Подача