Изобретение относится к вычислительной технике и может быть примене- н5 для реализации систем логических функций и построения цифровых функциональных преобразователей.

Цель изобретения - повышение надежности и упрощение логического запоминающего устройства.

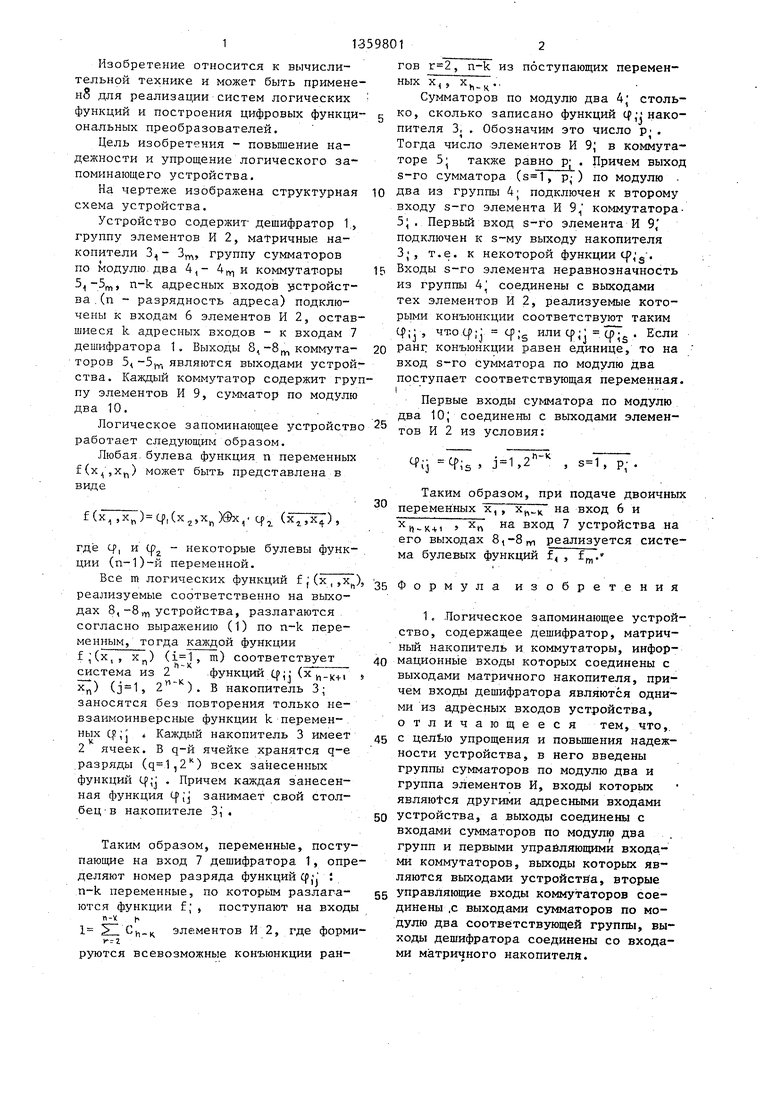

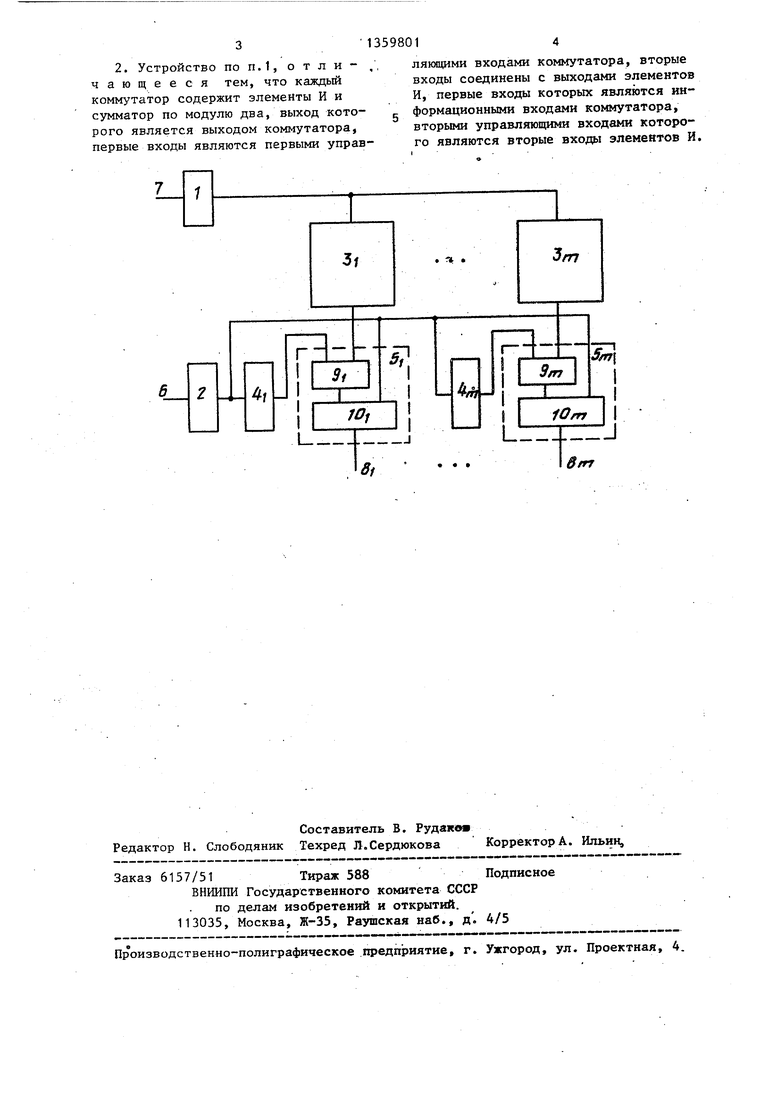

На чертеже изображена структурная схема устройства.

Устройство содержит дешифратор 1,, группу элементов И 2, матричные накопители 3,- 3т, группу сумматоров по модулю, два 4,- 4 и коммутаторы , n-k адресных входов устройства , (и - разрядность адреса) подключены к входам 6 элементов И 2, оставшиеся k адресных входов - к входам 7 дешифратора 1. Выходы 8,-8 коммутаторов 5, -5|Yi являются выходами устройства. Каждый коммутатор содержит группу элементов И 9, сумматор по модулю два 10..

Логическое запоминаюш,ее устройство работает следующим образом.

Любая.булева функция п переменных f(x,х,) может быть представлена в виде.

f (х ,х„)Ср,(х2,х)@х,- ср (Х4,х),

где СР| и tp2 некоторые булевы функции (п-1)-й переменной.

Все m логических функций f |(х,,Х| реализуемые соответственно на выходах 8,-8,у) устройства, разлагаются . согласно выражению (1) по n-k переменным, тогда каждой функции f (х,, х) (, т) соответствует система из 2 .функций Cf;; (х,,(, х) (j 1, ). В накопитель 3; заносятся без повторения только не- взаимоинверсные функции k перемен-. ных ср; j 4 Каждый накопитель 3 имеет 2 ячеек. В q-й ячейке хранятся cj-e разряды (,2) всех занесенных функций Ц);; . Причем каждая занесенная функция Cf ;j занимает свой столбец-в накопителе 3, .

Таким образом, переменные, поступающие на вход 7 дешифратора 1, определяют номер разряда функций Cf,-. ; n-k переменные, по которым разлагаются функции f;, поступают на входы

П-У f

1 51. Cj,n элементов И 2, где формиv-груются всевозможные конъюнкции ран

гов , n-k из поступающих переменных X,, х..

Сумматоров по модулю два 4| столько, сколько записано функций накопителя 3, , Обозначим это число р . Тогда число элементов И 9; в коммутаторе 5 также равно pj . Причем выход s-ro сумматора , р;) по модулю два из группы 4; подключен к второму входу s-ro элемента И 9, коммутатора- 5; . Первый вход s-ro элемента И 9, подключен к s-му выходу накопителя 3;, т.е. к некоторой функции . Входы s-ro элемента неравнозначность из группы 4 соединены с выходами тех элементов И 2, реализуемые которыми конъюнкции соответствуют таким cpij, 4T.o.q);j. ср; илис .(;p7s Если ранг конъюнкции равен единице, то на вход s-ro сумматора по модулю два

поступает соответствующая переменная. I

Первые входы сумматора по модулю

два 10; соединены с выходами элементов И 2 из условия:

h-K

q ij , 3 1.2 , , р;.

Таким образом, при подаче двоичных переменных х, , х, на вход 6 и X , , х на вход 7 устройства на его выходах 8,-8го реализуется система булевых функций f , f.

Формула изобретения

1, Логическое запоминающее устройство, содержащее дешифратор, матрич- ньй накопитель и коммутаторы, информационные входы которых соединены с выходами матричного накопителя, причем входы дешифратора являются одними из адресных входов устройства, отличающееся тем, что,.

с целЬю упрощения и повьщ1ения надежности устройства, в него введены группы сумматоров по модулю два и группа элементов И, входь которых являюФся другими адресными входами

устройства, а выходы соединены с входами сумматоров по модулю два групп и первыми управляющими входами коммутаторов, выходы которых являются выходами устройства, вторые

управляющие входы коммутаторов соединены ,с выходами сумматоров по модулю два соотвб тствующей группы, выходы дешифратора соединены со входами матричного накопителя.

3

2. Устройство по П.1, о т л и - чающееся тем, что каждый коммутатор содержит элементы И и сумматор по модулю два, выход которого является выходом коммутатора, первые входы являются первыми управ

лякнцими входами коммутатора, вторые входы соединены с выходами элементов И, первые входы которых являются информационными входами коммутатора, вторыми управляющими входами которого являются вторые входы элементов И.

вт

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2007 |

|

RU2373564C2 |

| Устройство для логического дифференцирования и интегрирования булевых функций | 1988 |

|

SU1541592A1 |

| САМОПРОВЕРЯЕМЫЙ МОДУЛЯРНЫЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ ЛОГИЧЕСКИХ ФУНКЦИЙ | 2009 |

|

RU2417405C2 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство для полиномиального разложения логических функций | 1987 |

|

SU1441380A1 |

| Устройство для решения булевых дифференциальных уравнений | 1989 |

|

SU1661791A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ СИСТЕМ БУЛЕВЫХ ФУНКЦИЙ | 2011 |

|

RU2461868C1 |

| Модуль для вычисления булевых функций | 1989 |

|

SU1803908A1 |

Изобретение относится к области вычислительной техники и может быть применено для реализации систем логических функций и построения цифровых функциональных преобразователей. Цель изобретения - повышение надеж- ности и упрощение устройства. Устройство содержит дешифратор, группу элементов И, m матричных накопителей, m групп сумматоров по модулю два и m коммутаторов. При подаче на входы элементов И двоичных переменных х, , Т и на входы дешифратора двоичных переменных х , , х„ (где п - разрядность адреса устройства) на выходах устройства реализуется система булевых функций f,, f. 1 з.п. ф-лы, 1 ил. со ел QD 00

| Зарубежная электроника, 1982, № 4, с | |||

| Приспособление для получения кинематографических стерео снимков | 1919 |

|

SU67A1 |

| Авторское свидетельство СССР № 1146730, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-15—Публикация

1984-07-23—Подача