Изобретение относится к вычислительной технике и может найти применение при построении однородньлх универсальных электронных вычислительных машин (ЭВМ) высокой производитэльности.

Известен арифметико-логический модуль, который содержит триггеры и первую и вторую группы шин управления, первую и вторую входные и первую и вторую выходные шины данных/ входную и первую и вторую выходные шины переноса, входную и выходную шины обратной связи и шину тактовых импульсов, соединенную с входами с.инхронизации триггеров, первого и второго разрядов ll.

Недостатком известного модуля являются узкие функциональные возмож:юсти, обусловленные тем, что каждый разряд и первый функциональный перенос налево описываются ограниченным набором переключательных функций трех аргументов: разрядов операндов и первого функционального переноса налево из предыдущего разряда. Этот , модуль позволяет реализовать лишь шесть основных операций, выполняемых за один такт синхронизации: арифметическое сложение в дополнительных

кодах-, поразрядные логическое сложение, умножение л инверсия суммы по модулю 2, сдвиг влево и вправо на один разряд. Второй функциональный перенос налево отсутствует, а функциональный перенос направо сводится к одной операции - сдвигу вправо на . один разряд.

Наиболее близким к предлагаемому

10 техническому решению является модуль, который содержит триггеры первого и второго разрядов,- первую и вторую группы шин управления, первую и вторую входные и первую и вторую выходt5ные шины данных, первую входную и первую и вторую выходные шины переноса, входную и выходную шины обратной связи, шину тактовых импульсов, первый, второй, третий и четвер20тый мультиплексоры, первую и вторую асинхронные выходные шины данных, соединенные соответственно с выходом второго мультиплексора, D-входом триггера первого разряда и выходом

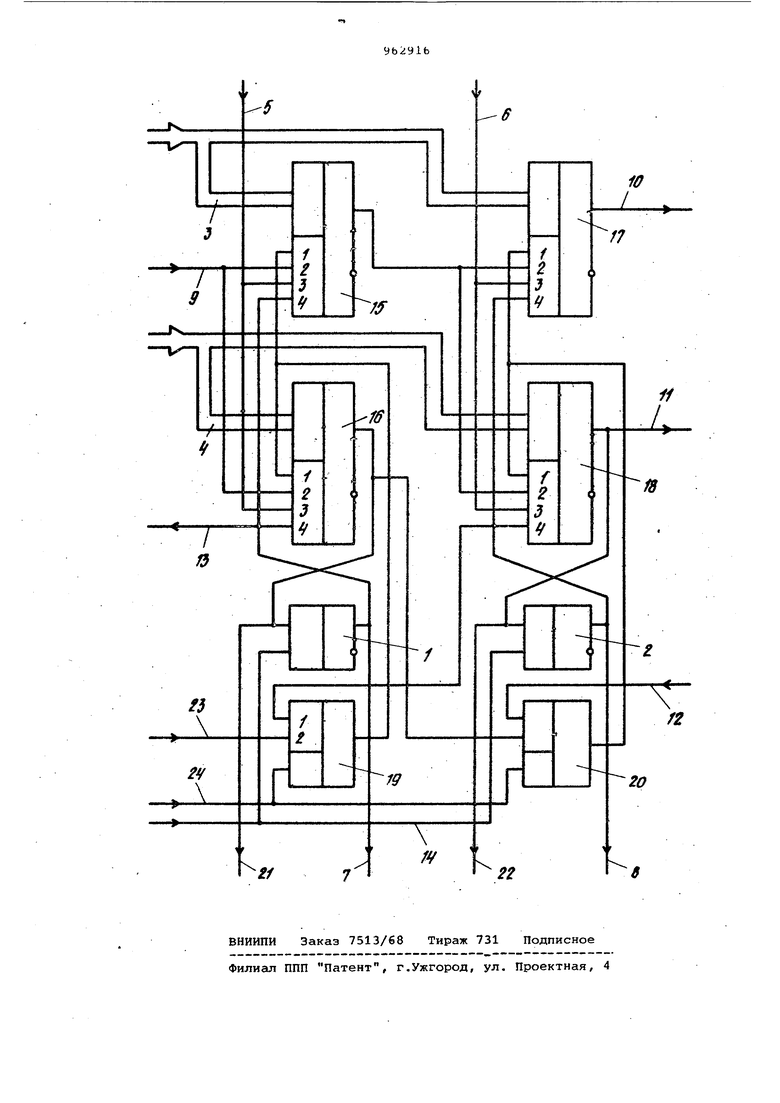

25 четвертого мультиплексора, D-входом триггера второго разряда, входы синхронизации триггеров первого и второго разрядов соединены с шиной тактовых импульсов, а выходы - с четвер30тыми управля1тщими входами первого и второго мультиплексоров, первой выходной ш-ной данных, выходной шиной обратной связи и с четвертыми управляющилт входами третьего и четвертого мультиплексоров, второй выходной шиной данных соответственно, первая и вторая входные шины данных соединены с третьими управляющими входами-первого и второго, третьего и четвертого мультиплексоров соответственно, вторые управляющие входы первого и второго, третьего и четвер того мультиплексоров соединены соответственно с первой входной шиной пе реноса и с выходом первого мультиплексора, первые управляющие входы первого и второго/ третьего и четвертого мультиплексоров соответственно соединены, информационные входы первого и третьего, второго и четвертого мультиплексоров соединены с первой и второй группами шин управления соответственно, а выход третьего мультиплексора соединен с первой выходной шиной перекоса С2 Недостатком известного модуля являются узк-ие ф /нкциональные возможности, обусловленные тем, что каждый разряд результата и первый функциональный перекос налево описываются полным набором переключательных функ ций лишь четырех аргументов: разря дов операндов, первого переноса из предыдущего разряда и сигнала обратной связи из последующего разряда, что не позволяет реализовать операции совместного ангшиза операндов, причем второй перекос отсутствует. Цель изобретения - раомирение функциональных возможностей ъюдупя за счет выполнения операции сравнения чисел, логических операций с проверкой на четность, операции параллельной проверки обоих операндов на четность, совмещенной поразрядной логической операции со сдвигом резул тата Влево, операции маскирования ре зультатом данной операции следующих разрядов результата другой логической операции над теми же операндами Поставленная цель достигается тем, что в арифметико-логический мо дуль, содержащий первый, второй, третий и четвертый мультиплексоры и два триггера, причем выход первого триггера подключен к первой шине вы ходных данных модуля, к выходной ши обратной связи модуля, к входу перв гО операнда первого и второго мульт плексоров, выход второго триггера подключен к второй шине выходных данных модуля и к входу первого опе ранда третьего и четвертого мультиплексоров, вход второго операнда пе вого и второго мультиплексоров подключен к первой шине второго операн модуля, к второй ш.ине второго опера да модуля подключен вход второго on ранда третьего и четвертого мультиплексоров, группы управляющих входов первого и третьего Mv-льтиплексоров соединены сперво шиной управления модуля, группы управляющих входов второго и четвертого мультиплексоров соединены с второй шиной управления модуля, первый вход переноса первого и второго мультиплексоров подключен к первой входной шине переноса модуля, первый вход переноса третьего и четвертого мультиплексоров подключен 1 выходу первого мультиплексора, выход второго мультиплексора соединен с первой асинхронной выходной шиной данных модуля и с 0-входом первого триггера, С-вход которого соединен с шиной тактовых импульсов модуля и с С-входом второго триггера, D-вход которого соединен с выходом четвертого мультиплексора, соединенного с первой выходной шиной переноса модуля, и с второй асинхронной выходной шиной данных модуля, выход третьего льтиплексора соединен с второй выходной шиной переноса модуля, введены пятый и шестой мультиплексоры,управляющий вход которых подключен к шине выбора режима модуля, вход переноса пятого мультиплексора соединен с второй входной шиной переноса модуля, вход данных пятого мультиплексора подключен к выходу второго триггера, а выход - к второму входу переноса первого и второго мультиплексоров, вход переноса шестого мультиплексора соединен с выходом второго мультиплексора, информационный вход - с входной шиной обратной связи модуля, а выход - с вторым входом переноса ретьего и четвертого мультиплексоров. На чертеже показана блок- схема арифметико-логического модуля. Арифметико-логический модуль содержит триггеры 1 и 2, шины 3 и 4 управления, первую шину 5 второго операнда, вторую шину б второго операнда, первую и вторую шины 7 и 8 в,ыходных данных, входную шину 9 и выходные шины 10 и 11 переноса, входную шину 12 и выходную ыину 13 обратной связи, шину 14 тактовых импульсов, мультиплексоры 15-20, асинхронЕ1ые выходные шины 21 и 22 данных, вторую входную шину 23 переноса и шину 24 выбора режима. Арифметико-логический модуль работает следующим образом. Двоичный код, подаваемый по шинам 3 и 4, задает вид реализуемой операции над двумя операндами,один из которых записан в триггерах первого 1 и второго 2 разрядов, а второй операнд установлен на входных . шинах 5 и 6. На выходах мультиплексоров 16 и 18 формируются соответственно первый и второй разряды кода

результата операции При этом i-тый разряд результата (первый или второй в зависимости от уровня сигнала на шине 24 выбора режима есть переключательная функция следующих аргументов: сигнала на i-той шине выходных данных (7 или 8); сигнала на i-той шине (5 или 6); сигнала первого переноса, поступающего по шине 9 или непосредственно с выхода мультиплексора 15, и сигнала обратной связи, поступающего непосредственно с шины 8 или по шине 12, если уровень сигнала на шине выбора режима равен логическому нулю, либо первых трех аргументов, указанных выше, и сигнала второго переноса, поступающего по второй входной шине 23 п.ереноса или непосредственно с выхода мультиплексора 16, если уровень сигнала на шине выбора режима равен логической единице. Вид этой функции определяется двоичным кодом, подаваемым по шине 4.

Одновременно на выходах мультиплексоров 15 и 17 формируются сигналы первого переноса из первого и второго разрядов, которые являются переключательными функциями тех же аргументов, что и сигналы результата операции в зависимости от уровня сигнала на шине 24 выбора режима. Вид этих функций определяется двоичным кодом, подаваемым по шине 3.

По фронту тактового импульса, поступающего по шине 14 на входы синхронизации триггеров 1 и 2 первого и второго разрядов, происходит запись кода результата операции с асинхронных выходны шин 21 и 22 данных в триггеры 1 и 2, Этот код подается на шины 7 и 8. Одновременно сигнал с выхода триггера 1 поступает на выходную шину 13 обратной связи, сигнал с выхода триггера 2 второго разряда - на вход пятого мультиплексора 19, сигнал с входной шины обратной связи - на вход шестого мультиплексора 20.

При этом начнется формирование нового кода результата операции, первый разряд которого поступит на второй информационный вход шестого мультиплексора 20, а второй - на шину переноса 11, причем на вход пятого мультиплексора 19 поступит сигнал с второй входной шины переноса 23. Одновременно будет происходить формирование первого Переноса, который с выхода третьего мультиплексора 17 поступит на первую выходную шину переноса.

Код, записанный в триггеры 1 и 2 первого и второго разрядов, остается неизменным до прихода фронта следующего тактового импульса.

Использование данного арифметикологического модуля позволяет расширить функциональные возможности по

сравнению с известным устройством. Оно обеспечивает реализацию 2 8,589.934.592 (количество возможных кодовых комбинаций на шинах управления и шине выбора режима) различных арифметико-логических операций с двумя операндами, каждая из которых выполняется за один такт синхронизации.

Это обусловлено тем, что каждый разряд результата, первый и второй

o перенос описываются полным набором переключательных функций следующих аргументов: либо разрядов операндов, первого переноса из предыдущего разряда и сигнала обратной связи из последующего разряда , либо трех первых

s вышеназванных, а также сигнала второго переноса из предыдущего разряда.

Кроме известных, данный арифметико-логический модуль позволяет, например, реализовать операцию сравне0ния чисел, заданных в прякых кодах I результат сравнения , или формируется на первой и второй выходных шинах переноса); совмещенную поразрядную логическую операцию с проверкой

5 результата на четность; совмещенную операцию выделения хотябы одной 1 из разрядов операндов, следующих за разрядами, в обоих.из которых находятся 1, с одновременной проверкой

0 результата на четность; операцию параллельной проверки обоих операндов на четность (результат формируется на первой iP второй выходных шиндх переноса и имеет 4 исхода: четный-четный;

5 четный-нечетный; нечетный-четный; нечет-, ный-нечетный) ;совмещенную поразрядную логическую операцигс со сдвигом результата влевог совмещенную поразрядную логическую операцию и маскирование

0 результатом этой операции следующих разрядов результата другой поразрядной логической операции над теми же операндги«1И. .

Реализация за один такт совмещенных арифметико-логических опе5раций позволяет повысить быстродействие предложенного модуля по сравнению с известным.

Кроме того, данный модуль может быть использован для реализации сис-

O тем переключательных функций.

Изобретение дает возможность строить однородные универсальные рднои мультипроцессорные ЭВМ.

5

Таким образом, будучи выполненным в виде большой интегральной схемы, модуль обеспечит себе широкую сферу применения в области вычислительной техники; начиная от узлов специали0зированных вычислительных устройств, таких как комбинационные cxenti, реа лизирующие системы переключательных функций, цифровые анализаторы, универсальные регистры, счетчики, сум5маторы и др., и кончая блоками однородных универсальных мультиьшкропроцессорных ЭВМ.

Формула .изобретения

Арифметико-логический модуль,содержащий первый, второй, третий и четвертый мультиплексоры и два триггера, причем выход первого триггера подключен к первой шине выходных данных модуля, к выходной шине обратной связи модуля, к входу первого операнда первого и второго мультиплексоров, выход второго триггера подключен к второй шине выходных данных модуля и к входу первого операнда третьего и четвертого мультиплексоров, вход второго операнда первого и второго мультиплексоров подключен к первой шине второго операнда модуля, к .второй шине второго операнда модуля подключен вход второго операнда третьего и четвертого мультиплексоров, группы управляющих входов первого и третьего мультиплексоров , с пеЬвой шиной управления модуля, группыуправляющих входов второго и четвертого мультиплексоров соединены с второй шиной управления, модуля, первый вход переноса первогб и второго мультиплексоров подключен к первой входной шине переноса моду ля, первый вход переноса третьего и четвертого мультиплексоров подключен к выходу первого мультиплексора выход второго мультиплексора соединен с первой асинхронной выходной шиной данных модуля и с D-входом первого триггера, С-вход которого соединен с Ш1-$ной тактовых импульсов моду- ля и с с-входом второго триггера.

D-вход которого соединен с выходом четвертого мультиплексора, соединенного с первой выходной шиной переноса модуля, и с второй асинхронной выходной шиной данных модуля, выход третьего мультиплексора соединен с второй выходной шиной переноса модуля, отличающийся тем, что, с целью расширения функциональных возможностей модуля за счет

0 выполнения операции сравнения чисел, логических операций с проверкой на четность, операции параллельной проверки обоих операндов на четность, совмещенной поразрядной

S логической операции со сдвигом результата влево, операции маскирования результатом данной операции следунвдих разрядов результата другой логической операции над теми же операндами, в него введены пятый и шестой мультиплексоры, управляющий вход которых подключен к .шине выбора режима модуляг вход переноса пятого мультиплексора соединен с второй входной

5 шиной переноса модуля, вход данных пятого Мультиплексора подключен к выходу второго триггера, а выход - к второму входу переноса первого и второго мультиплексоров, вход переноса шестого мультиплексора,информационный вхоД - с входной шиной обратной свяп зи модуля, а йыход - с вторым входом переноса третьего и четвертого муль-; типлексоров..

Источники информации,

5 принятые во внимание при экспертизе

1. Зарубежная электронная техника. М. 1977, № 9, с.19-21.

2.Авторское свидетельство СССР по заявке 2786482/18-24,

0 кл. G Об F 7/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Микропроцессорная секция | 1979 |

|

SU842789A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Многофункциональный модуль | 1984 |

|

SU1238098A1 |

| Арифметико-логический модуль | 1988 |

|

SU1539765A1 |

| Операционный модуль | 1982 |

|

SU1083198A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

| Арифметико-логический модуль | 1988 |

|

SU1501032A1 |

Авторы

Даты

1982-09-30—Публикация

1980-05-30—Подача