&9

i4

: Изобретение относится к вычислительной технике и предназнячено для реализации сргстем логических функций описывающих работу цифровых преобра- з(рвателей.

: Цель изобретения - упрощение уст рбйства за счет уменьшения количест- вй элементов памяти.

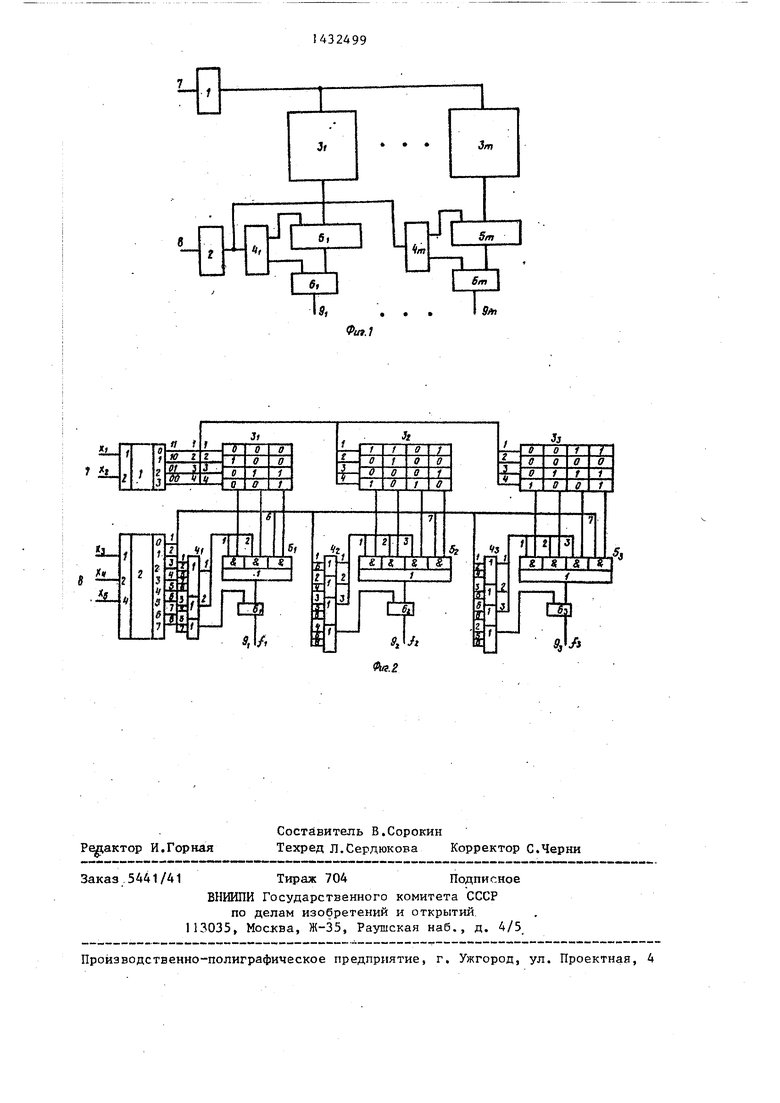

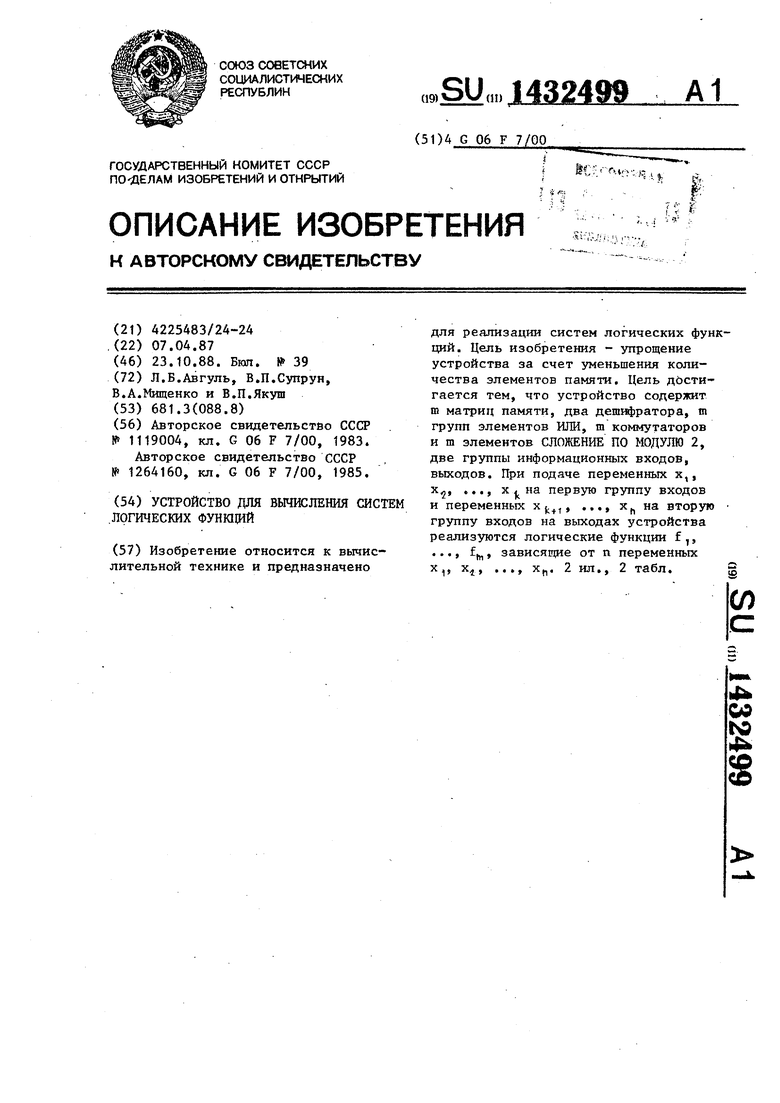

На фиг. 1 приведена структурная схема предлагаемого устройства; на фг 1г. 2 - пример функциональной схемы устройства.

Устройство (фиг. 1) содержит де 1Ш1фратор 1 и 2, m (по числу реализуе- устройством логических функций) блоков 3.1-З.т памяти, m групп 4.1- 4„т элементов ИЛИ, m коммутаторов 5 1-5.т, элементов СЛО})(ЕНИЕ ПО МОДУ- Л) 2 б,1-6,т, первую 7 и вторую 8 группы информационных входов, m вы- . х(})дов 9.1-9.т.

Устройство работает следующим образом.

I На вход 7 первого дешифратора 1 пфдаются двоичные переменные х, ,.., на вход 8 второго дешифратора 2 -

двоичные переменные х

kM

ц

выходах ,т устройства реализуются логические функции f (х

,)

ft

., X1) , ffjjCx, «.., X

соответственно.

Система m логических функций .(х,, х, ..., х), где i 1,2, . if. t ™ разлагается по Шеннону по k{k (. п) переменным х х, ..,, х на функции (f. (х,, ..., х), где j; 1,2..,2 „ Таким образом, каждо ф гнкции f ; соответствует 2 функций

%

Логические функции Ц-- размеща

ются в памяти так, что каждая из них занимает одно слово (строку) в i-й матрице (блоке) памяти. Очевидно одноименным ра;5рядам

S (S 1,.

) функций g,-j(x .,, ..,, j 1 , 2., ..., 2, соотв

,),

где

логические фз нкции

соответствзпот

Х(), каждая из которых

М,-5(Х

19 л, . ,

занимает

столбец в i-й матрице памяти. Следовательно., переменные х , , .,.,

i-й мат 5 к

значение выбранной функции ( - , которое совпгщает со значением функ hрице.

определяют функцию а переменные х,.

4,-sB

-4.

) на данном

..., . .,

х.

щт fi-(x,, -X

наборе переменных х,, у.,

Если переменные х,, х, подают на первый дешифратор, выход

которого подключает к адресным шинам матриц памяти, переменные У i , t ..., х подают на второй дешифратор, выход которого подключают к управляющим входам коммутаторов, информационные входы которых соединяют соответственно с выходами матриц памяти, на выходе коммутаторов реализуются функции f j(x,j х, ..., х ) , где i 1, 2, ...,m.

С целью уменьшения аппаратурных затрат все попарно тождественные и взаимоинверсные функции ij Vif (V,-pC f V,T ifb S Ь 2, ..., 1 1, 2, ..., 2 - , S 7 1), которым соответствуют сигналы на S-м и 1-м выходам второго дешифратора, размещаются в памяти так, чтобы они занимали один столбец. Тогда соответствующий управляющий вход коммутатора прдключается к выходу элемента ИЛИ, входы которого соединяются с S-M и 1-м выходам второго дешифратора 2. Таким образом, в результате такого объединения в i-ю матрицу 3i памяти заносятся Р{ логических функг

X

ций k переменных

х.) (е „ Xj, .1;; Xj.),

Jii

1 .«.. )b Ь 2, ..., P.

л п. г -

S 1, 2, ..., 2 . При этом г-е выходы второго дешифратора 2, для которых (f I fi объединяются на входе одного из элементов ИЛИ i-й группы 4,-, выход которого подключается к первому входу i-ro элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 61, второй вхо которого подключен к выходу i-ro коммутатора 5,., а выход соединяется с iM выходом 9. устройства, на котором и реализуется заданная логическа функция (х, Xj, ..., Xf,).

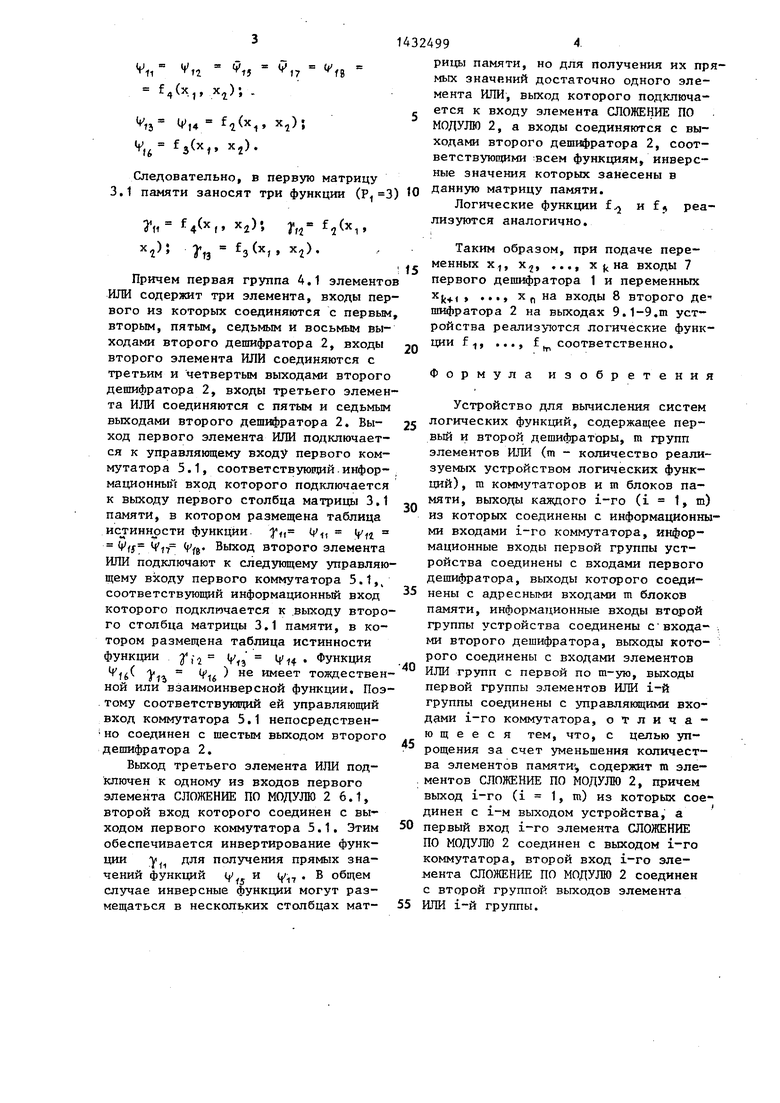

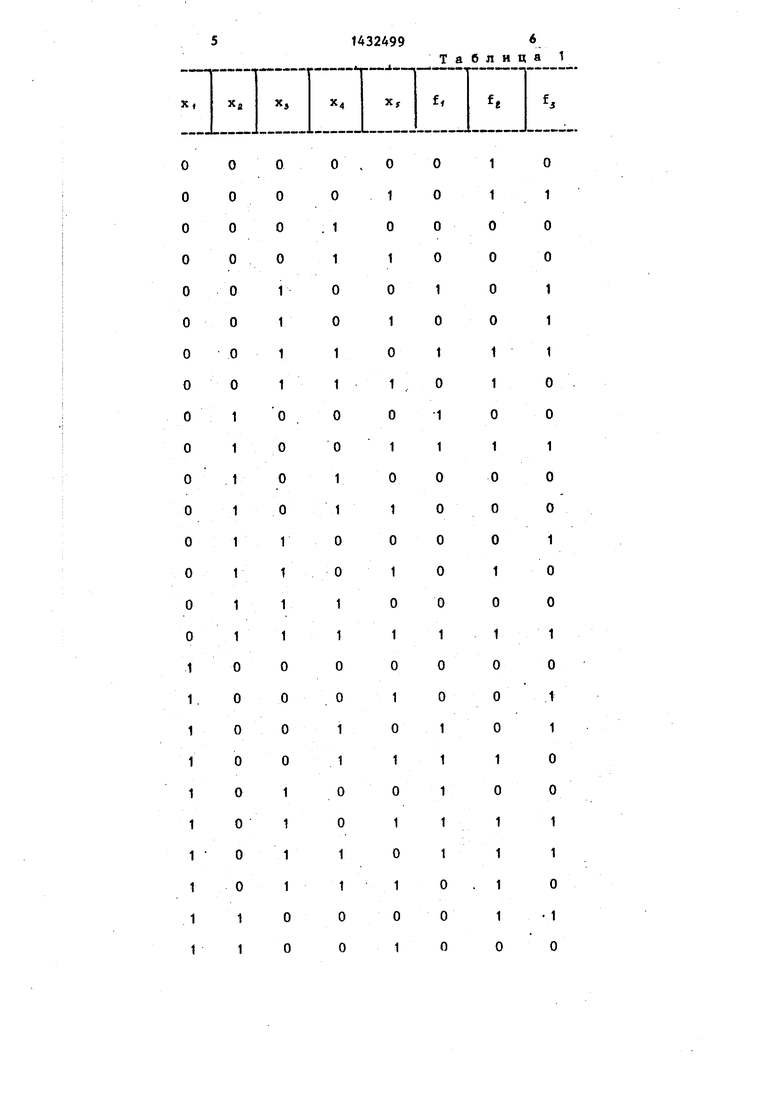

Работу предлагаемого устройства рассматривают на примере реализации трех логических функций памяти переменных (табл. 1),

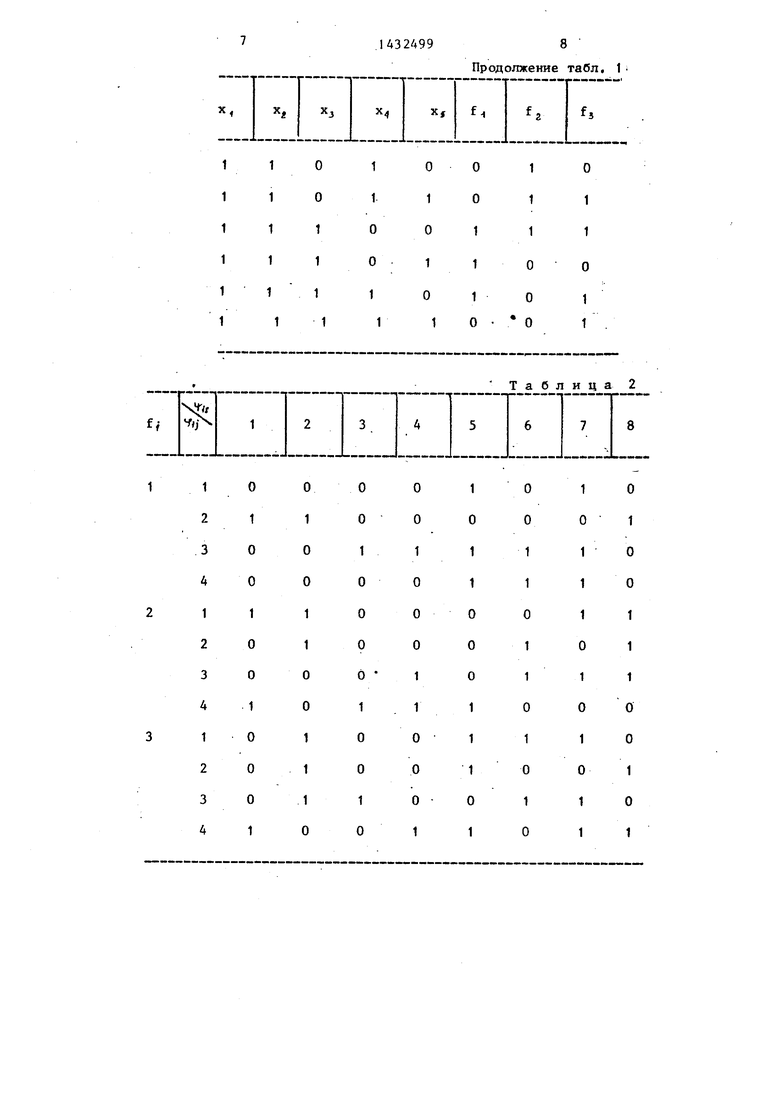

Разлагают функции f-(х,, х,, х,, где i 1, 2, 3, по k 2 переменным х. и х, (табл. 2):

f,(x,, Xj,Xj, Х,,Х.5) Х.,, Х2 V Х .,VX,:, .jVX Xjt..

Рассматривают, например, реализации функции fi(x,,, X,j, Xj, Х, Ху).

Из табл. 2 следует

V,, x); .

V

17

V

f8

V,

73- i4 x,);

V, fiCx,, xj)

Следовательно, в первую матрицу 3,1 памяти заносят три функции (Р, 3) О

и ГгГ

2 t3 3

Причем первая группа 4,1 элементов ИЛИ содержит три элемента, входы первого из которых соединяются с первым вторым, пятым, седьмым и восьмым выходами второго дешифратора 2, входы второго элемента ИЛИ соединяются с третьим и четвертым выходами второго дешифратора 2, входы третьего элемента ИЛИ соединяются с пятым и седьмым выходами второго дешифратора 2, Выход первого элемента ИЛИ подключается к управляющему входу первого коммутатора 5,1, соответствующий.информационный вход которого подключается к выходу первого столбца матриць 3,1 памяти, в котором размещена таблица )сти функции fit- t li Уп (j)y ,7 ((g. Выход второго элемента ИЛИ подрслючают к следующему управляющему входу первого коммутатора 5,1,/ соответствующий информационный вход которого подключается к .выходу второго столбца матрицы 3.1 памяти, в котором размещена таблица истинности функции , 2 fИ Функция -j ( ) не имеет тождественной или взаимоинверсной функции. Поэтому соответствующий ей управляющий вход коммутатора 5,1 непосредствен- но соединен с шестым выходом второго дешифратора 2,

Выход третьего элемента ИЛИ подключен к одному из входов первого элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 6,1, второй вход которого соединен с выходом первого коммутатора 5,1, Этим обеспечивается инвертирование функции у для получения прямых значений функций 15 Vi7 общем случае инверсные функции могут размещаться в нескольких столбцах матО

5

0

рицы памяти, но для получения их прямых значений достаточно одного элемента ИЛИ, выход которого подключается к входу элемента СЛОЖЕНИЕ ПО МОЛУЛЮ 2, а входы соединяются с выходами второго дешифратора 2, соответствующими всем функциям, инверсные значения которых занесены в данную матрицу памяти.

Логические функции f и fj реализуются аналогично.

Таким образом, при подаче переменных X,, х, .,., Х|(На входы 7 первого дешифратора 1 и переменных Xfc+i п 3 входы 8 второго де- шифратора 2 на выходах 9,1-9,т устройства реализуются логические функции f 1, ,

f соответственно.

5

0

5

0

5

0

5

Формула изобретения

Устройство для вычисления систем логических функций, содержащее первый и второй дешифраторы, m групп элементов ИЛИ (т - количество реализуемых устройством логических функций) , m коммутаторов и m блоков памяти, выходы каждого i-ro (i 1, m) из которых соединены с информационными входами i-ro коммутатора, информационные входы первой группы устройства соединены с входами первого дешифратора, выходы которого соединены с адресными входами m блоков памяти, информационные входы второй группы устройства соединены с входа- , ми второго дешифратора, выходы которого соединены с входами элементов ИЛИ групп с первой по т-ую, выходы первой группы элементов ИЛИ i-й группы соединены с управляющими входами i-ro коммутатора, отличающееся тем, что, с целью упрощения за счет уменьшения количества элементов памяти , содержит m элементов СЛОЖЕНИЕ ПО МОДУЛЮ 2, причем выход i-ro (i 1, m) из которых соединен с i-M выходом устройства, а первый вход i-ro элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 соединен с выходом i-ro коммутатора, второй вход i-ro элемента СЛОЖЕНИЕ ПО МОДУЛЮ 2 соединен с второй группой выходов элемента НИИ i-й группы.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления систем логических функций | 1985 |

|

SU1264160A1 |

| Устройство для вычисления логических выражений @ переменных | 1983 |

|

SU1119004A1 |

| Устройство для полиномиального разложения логических функций | 1987 |

|

SU1441380A1 |

| Устройство для вычисления систем логических функций | 1982 |

|

SU1269146A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Преобразователь формы представления логических функций | 1987 |

|

SU1441381A1 |

| Устройство для организации мультиветвления процессов в электронной вычислительной машине | 1980 |

|

SU922743A1 |

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| Устройство для вычисления элементарных функций | 1985 |

|

SU1298764A1 |

| Аналого-цифровое устройство для вычисления полиномиальной функции | 1985 |

|

SU1262530A1 |

Изобретение относится к вычислительной технике и предназначено для реализации систем логических функций. Цель изобретения - упрощение устройства за счет уменьшения количества элементов памяти. Цель дЬсти- гается тем, что устройство содержит m матриц памяти, два дешифратора, m групп элементов ИЛИ, m коммутаторов и m элементов СЛОЖЕНИЕ ПО МОДУЛЮ 2, две группы информационных входов, выходов. X, При подаче переменных х 1 k, .., и переменных первую группу входов fc+,. .... х на вторую группу входов на выходах устройства реализуются логические функции f Xj , . ., 1 зависящие от п переменных X, 2 ил., 2 табл.

О О О

о

о

о

о

о

1

1

1

1

1

1

1

1

о

о

о

о

о

о

о

о

1

1

о

о

о

о

1

1

1

1

о

о

о

о

г

1

1

1

о

о

о

о

1

1

1

1

о

о

о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о 1 1 о о

о о о о 1 о 1 о 1 1

о о о о о 1 о о 1 1 1 1 1 о о о

1 1 о о о о 1 1 о 1 о о о 1 о 1 о о о 1 о 1 1 1 1 о

о 1 о о 1 1 1 о о 1 о о 1 о о 1 о 1 1 о о 1 1 о 1 о

О О 1 1 1

.14324998

Продолжение табл. 1

о 1 о 1

о 1

о о 1 1

1 о

1

1 1 о

о о

о

1 1

о

1

1

Таблица 2

| Устройство для вычисления логических выражений @ переменных | 1983 |

|

SU1119004A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления систем логических функций | 1985 |

|

SU1264160A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-07—Подача