Од

со

Изобретение относится к автоматие и вычислительной технике и может быть использовано в системах контроля .

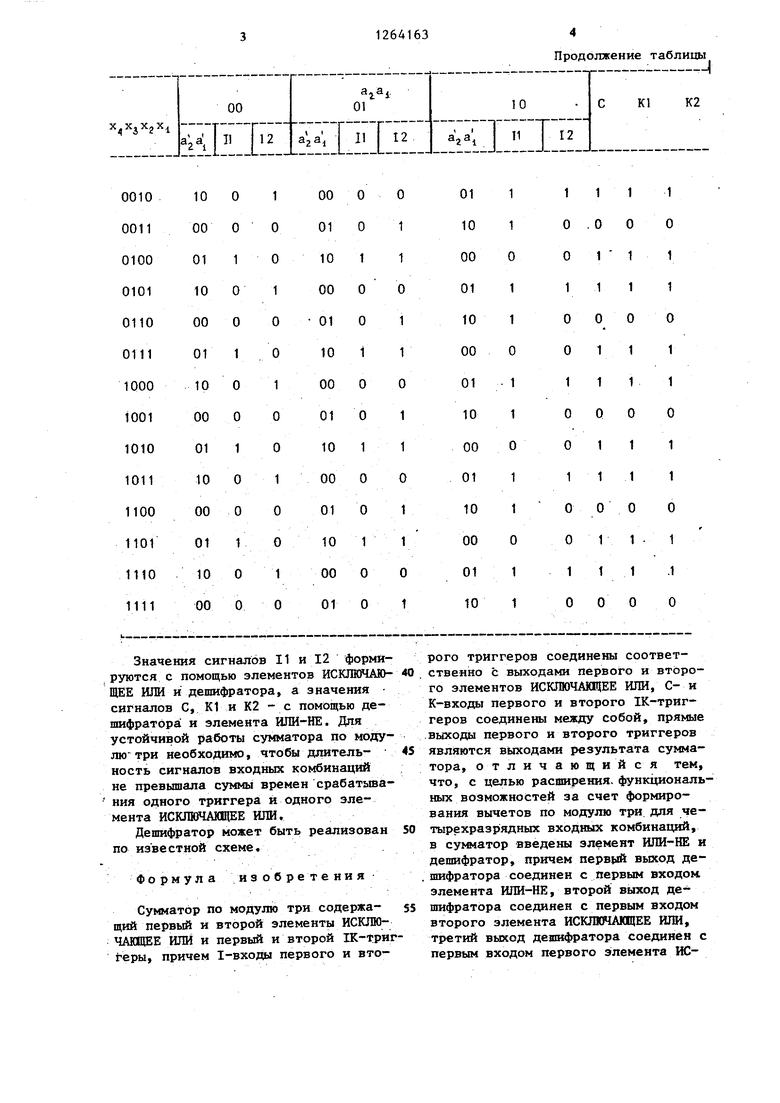

Цель изобретения - расширение ункциональных возможностей за счет ормирования вычетов для четырехазрядных входных комбинаций.

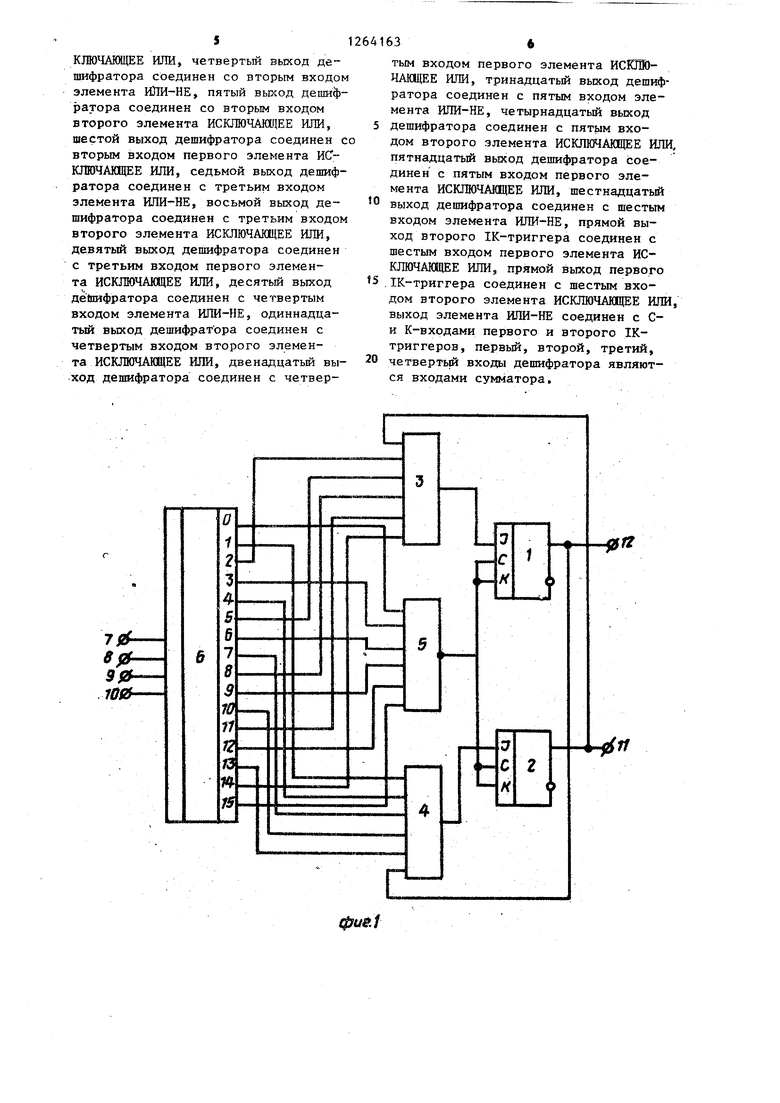

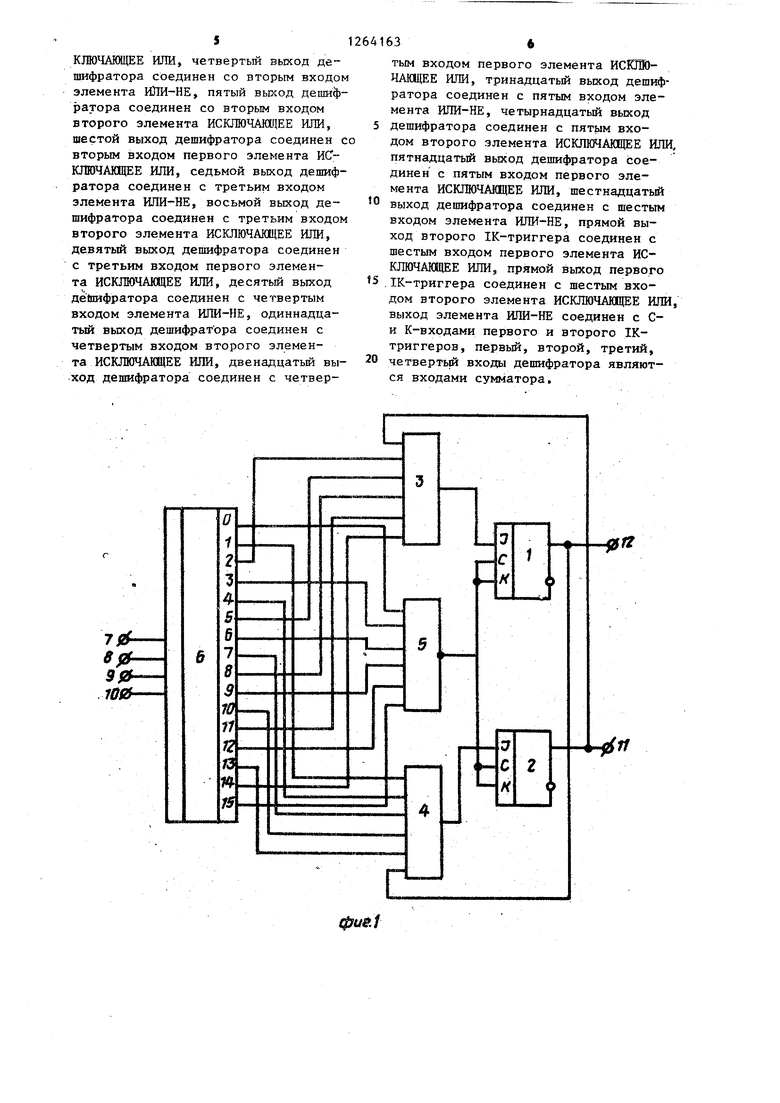

На фиг.1 представлена структурная схема сумматора по модулю три, на фиг.2 - графа переходов сумматора по модулю три.

Сумматор по модулю три (фиг.1) содержит первьй и второй триггеры 1 и 2, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 3 и 4, элемент ШШ-НЕ 5 и дешифратор 6, первый 7, второй 8, третий 9 и четвертьй 10 информационные входы, первьй 11 и второй 12 выходы результата.

Сумматор работает следующим образом.

На графе (фиг.2) номера вершин 0,1,2 соответствуют значениям суммы по модулю три. Дугами показаны направления переходов при поступлении на входы сумматора по модулю три всех входных комбинаций, заданных

функцц;|1ми fj x XjXj 3 Vx j jX2XjV x XjXjX vx XjXjX vXj, JCjXj x.,XjX2Xj;.

f j X X Xj X.( V X Кд Xj X V X Xj Xj X V/ X XjXjX V X XjXjX V K XjSjX V V Х4ХзХл| Х У ,X

где старший с весом 8, Xj - с весом 4, Х2 - с весом 2, х - с ве- . сом 1 разряды этих комбинаций. Сумма по модулю три кодируется состоянияи триггеров Т2, Т1 следующим образом: О - 00, 1 - 01, 2 - 10, состояния триггеров обозначены символами aj а (aj - старший с весом 2, а - младший с весом 1 разряды суммы). В исходном состоянии триггеры Т1 и Т2 находятся в нулевом состоянии (цепи установки триггеров в исходное состояние на фиг,1 не поKasaHbJ). В каждом такте работы триггеры сначала находятся в определенном текущем состоянии CL, о.. соответствующем сумме по модулю три всех поступивших ранее входных комбинаций x XjXjX, Затем на первый 7, втрой 8, третий 9 и четвертый 10 входы поступают соответственно значения х, Xj, Xj, X., разрядов входной комбинации, под воздействием которых триггеры переходят в очередное состояние, которое определяет сумму по модулю три всех входных комбинаций в том числе и поступившей в данном такте работы.

Из графа переходов видно, что при поступлении на входы комбинаций x XjXjX, заданных функций fj (с значениями разрядов 0000 ООП, 0110, 10001 1111), суша по модулю три не изменяется и триггеры не изменяют своих состояний. В этом случае сигнал синхронизации на Свходах обоих триггеров равен нулю. В остальных случаях сигнал синхронизации на С-входах триггеров равен 1 и триггеры могут изменять свои состояния при поступлении входных комбинаций, заданных функциями fj и f 3 .

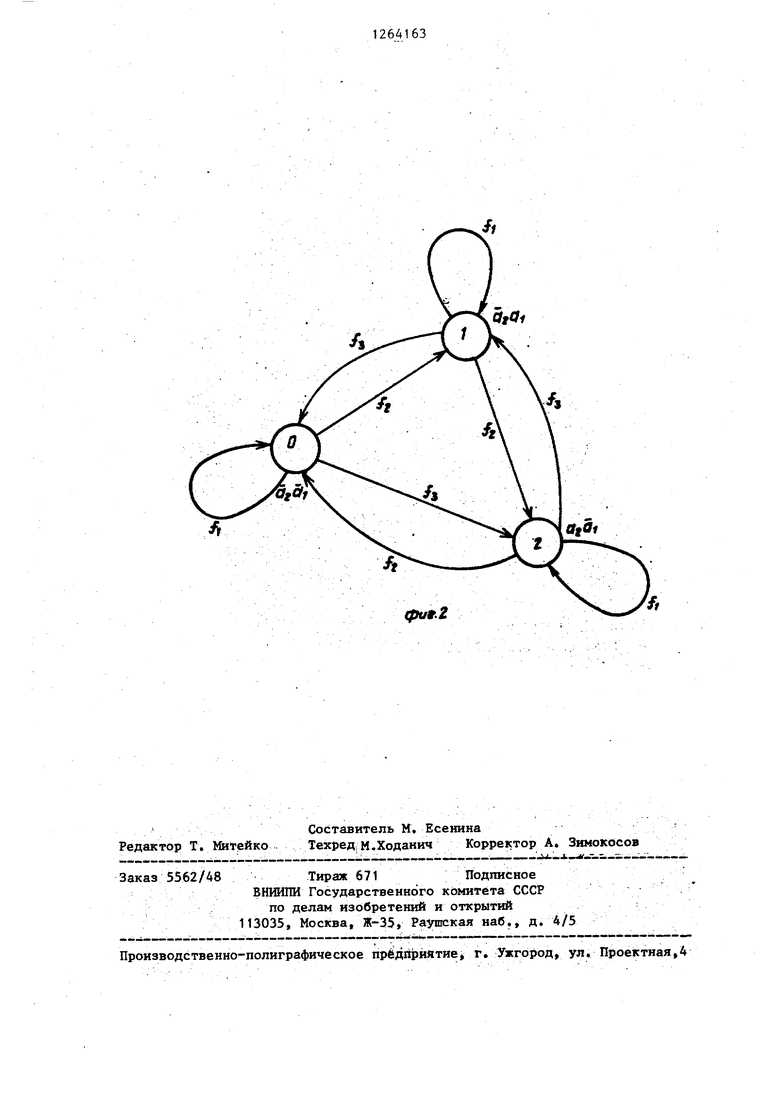

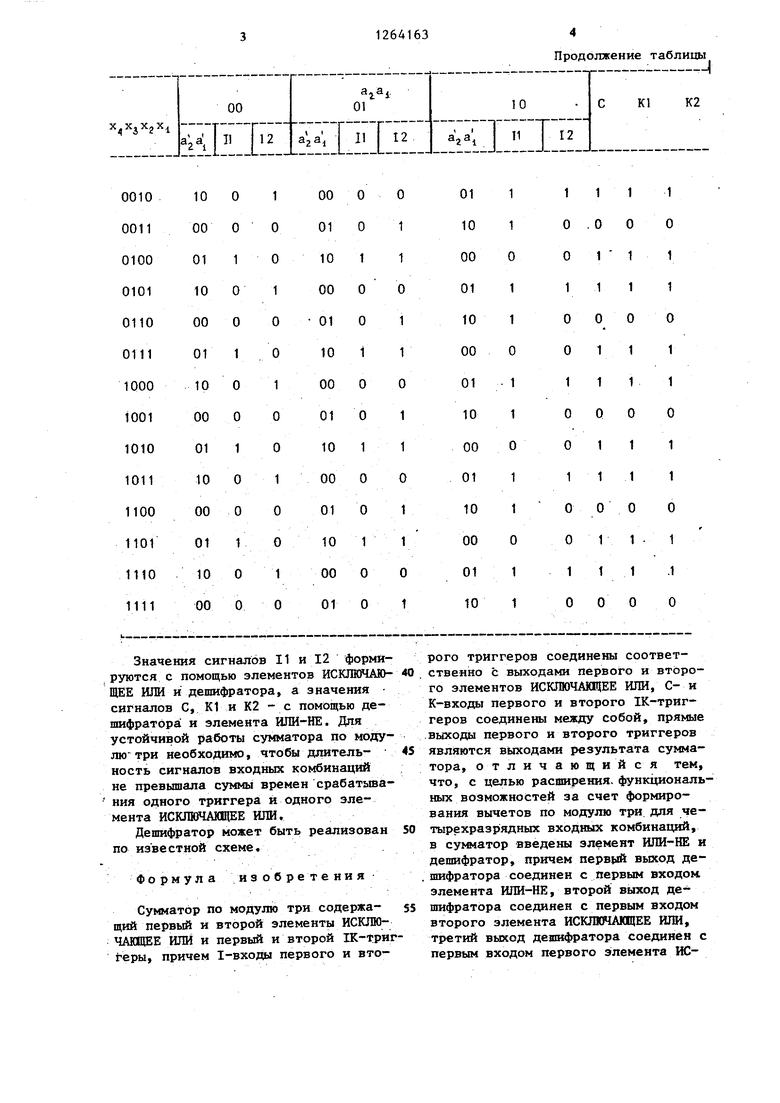

Переходы триггеров сумматора по модулю три из всех возможных текущих состояний о., ai(00, 11, 11) в очередные состояния схз а при различных значениях входных комбинаций

x XjX2Xi приведены в таблице. Там же приведены значения сигналов синхронизации (с) на С-входах и сигналов на I- и К-входах первого II,К1 и второго 12,К2 триггеров, обеспечивающих, эти переходы. Значения сигналов II, 12 приведены для тех случаев, когда текущее состояние триг,геров равно , 01, 10. Сигналы синхронизации (С) и сигналы на К-входах совпадают и не зависят от текущего состояния триггеров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1983 |

|

SU1153324A1 |

| Устройство для формирования и хранения вычетов по модулю три | 1984 |

|

SU1164710A1 |

| Устройство для контроля параметров | 1984 |

|

SU1166065A1 |

| Управляемый арифметический модуль | 1982 |

|

SU1062688A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Четырехканальный время-импульсный преобразователь | 1986 |

|

SU1388821A1 |

| Устройство для декодирования с коррекцией ошибок | 1985 |

|

SU1446695A1 |

| Устройство для умножения в системе остаточных классов | 1984 |

|

SU1166098A1 |

Изобретение предназначено для систем контроля, применяемых в автоматике и вычислительной технике. Целью изобретения является расшире- ние функциональных возможностей за счет формирования вычетов по модулю три для N-разрядных входных слов, поступающих последовательно по четыре разряда. В сумматоре по модулю три осуществляется формирование вычета по модулю три для входных Nразрядных слов, поступающих по четыре разряда. Устройство содержит два триггера, два логических элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, злемент ИЛИ-НЕ и дешифратор. Использование логического злемента И и дешифратора позволило сократить время формирования вычетов для N-разрядных входных слов и расширить функциональные возможности за счет формирования вычес S тов по модулю три для четырехраз(Л рядных входных комбинаций. 2 ил.

000000 О О 01 О 1

000101 1 О 10 1 1

О О

1

О 1

О 1 О О 1

Значения сигналов II и 12 формйрзгются с помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и дешифратора, а значения сигналов С, К1 и К2 - с помощью дешифратора и элемента ШШ-НЕ. Для устойчивой работы сумматора по модулю три необходимо, чтобы длительность сигналов входных комбинаций не превышала суммы времен срабатьтания одного триггера и одного элемента ИСКЛЮЧАИЩЕЕ ИЛИ.

Дешифратор может быть реализован по известной схеме.

Формула и 3 обре тения

Сумматор по модулю три содержащий первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и первый и второй 1К-триг еры, причем Т-входал первого и втоПродолжение таблицы

рого триггеров соединены соответственно с выходами первого и второго элементов ИСКЛЮЧАИДЕЕ ИЛИ, С- и К-входы первого и второго 1К-триггеров соединены между собой, прямые ,выходы первого и второго триггеров являются выходами результата сумматора, отличающийся тем, что, с целью расширения, функциональных возможностей за счет формирования вычетов по модулю три для четырехраэр 1дных входных комбинаций, в cyi«iaTop введены элемент ШШ-НЕ и дешифратор, причем первый выход дешифратора соединен с первым входом элемента ИПИ-НЕ, второй выход дешифратора соединен с первым входом второго элемента ИСКЛКНАЩЕЕ ИЛИ, третий выход дешифратора соединён с первым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четвертый выход дешифратора соединен со вторым входом элемента ИЛИ-НЕ, пятый выход дешифратора соединен со вторым входом второго элемента ИСКЛЮЧАНШЩЕ ИЛИ, шестой выход дешифратора соединен с вторым входом первого элемента ИСКЛГОЧАЩЕЕ ИЛИ, седьмой выход дешифратора соединен с третьим входом элемента ИЛИ-НЕ, восьмой выход дешифратора соединен с третьим входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, девятый выход дешифратора соединен с третьим входом первого элемента ИСКШЧАЮЩЕЕ ИЛИ, десятый выход дёШифратора соединен с четвертым входом элемента ИПИ-НЕ, одиннадцатый выход дешифратора соединен с четвертым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ, двенадцатьм выход дешифратора соединен с четвертым входом первого элемента ИСЮТОЧАЩЕЕ ИЛИ, тринадцатый выход дешифратора соединен с пятым входом элемента ИЛИ-НЕ, четырнадцатый выход дешифратора соединен с пятым входом второго элемента ИСКЛЮЧАКЩЕЕ ШШ пятнадцатый выход дешифратора соединен с пятым входом первого элемента ИСКЛОЧАНЩЕЕ ИЛИ, шестнадцатьй выход дешифратора соединен с шестым входом элемента ИЛИ-НЕ, прямой выход второго 1К-триггера соединен с шестым входом первого элемента ИСКЛЮЧАЩЕЕ ИЛИ, прямой выход первого . 1К-триггера соединен с шестым входом второго элемента ИСКЛЮЧАЩЕЕ ИЛИ выход элемента ИЛИ-НЕ соединен с Си К-входами первого и второго IKтриггеров, первый, второй, третий, четвертьй входы дешифратора являются входами сумматора.

| Сумматор по модулю три | 1980 |

|

SU890393A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сумматор по модулю три | 1983 |

|

SU1153324A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-15—Публикация

1985-02-19—Подача