(5) СУММАТОР ПО МОДУЛЮ ТРИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1983 |

|

SU1153324A1 |

| Перестраиваемый шифратор | 1989 |

|

SU1651384A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2037958C1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| Устройство для формирования признаков распознаваемых образов | 1986 |

|

SU1328830A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1164724A1 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

i

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля.

Известен сумматор по модулю три, содержащий три установочных триггера с элементами управления в каждом плече триггера на элементах И-НЕ 1 .

Недостатком его является низкое быстродействие.

Наиболее близким техническим реше- О нием к изобретению является сумматор по модулю три, содержащий схемы совпадения, два триггера и две схемы ИЛИ, выходами подключенные ко входам триггеров, первый вход первой схемы сов- падения совместно с первым входом второй схемы совпадения, а второй вход совместно с первым входом третьей схемы совпадения являются входами сумматора по модулю три, а вторые входы второй и третьей схемы совпадения подключены к входу первой схемы совпадения 2 .

Недостатком известного устройства является низкое быстродействие, обусловленное наличием линии задержки.

Цель изобретения - увеличение быстродействия сумматора.

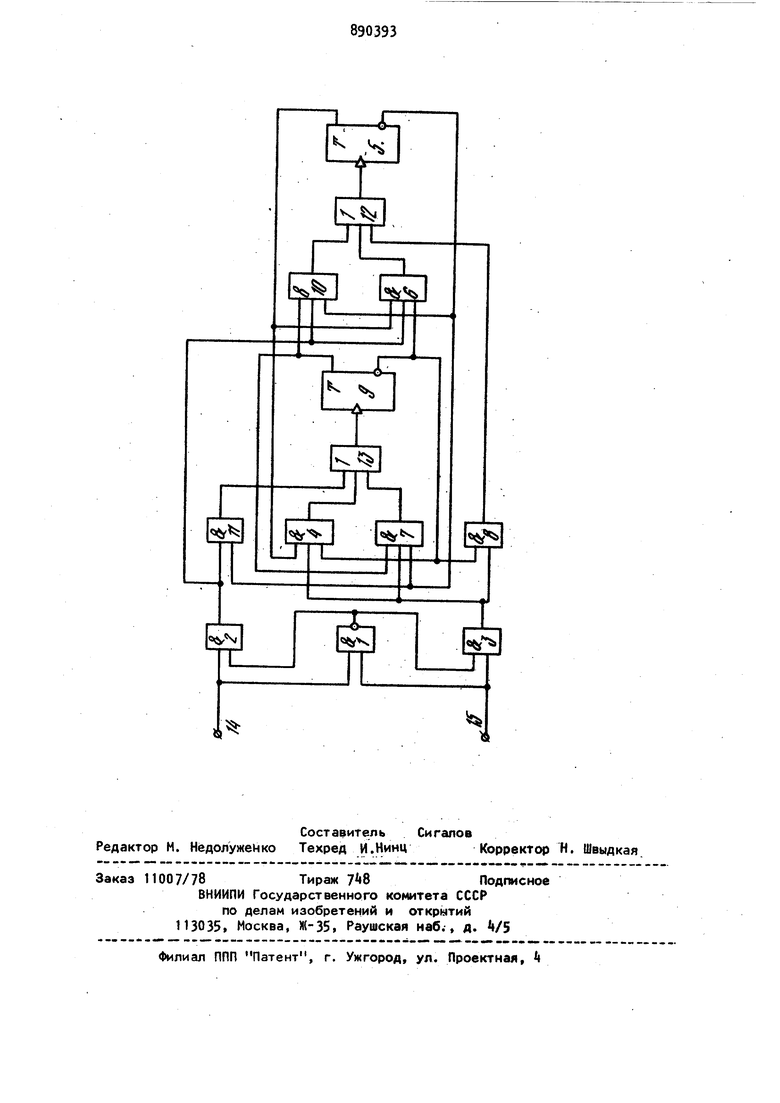

Поставленная цель достигается Тем, что в сумматор по модулю три, содержащий первый и второй триггеры, первый и второй элементы ИЛИ, первый, второй и третий элементы И, причем первый вход сумматора соединен с первым входом первого и второго элементов И, второй вход сумматора соединен с первым входом третьего элемента И и вторым входом первого элемента И, инверсный выход которого соединен со вторыми входами второго и третьего элементов И, выходы первого и второго элементов ИЛИ соединены соответственно со счетными входами первого и второго триггеров, введены четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем прямой выход первого триггера соединен с первыми вхо38дами четвертого и пятого элементов И, . выходы которых соединены соответствен но с первыми входами второго и первого элементов ИЛИ, выход третьего элемента И соединен с. первыми входами Шестого и седьмого элементов И и со вторым входом четвертого элемента И, выход второго элемента И соединен с первыми входами восьмого и девятого элементов И и вторым входом пятого эле мента И, инверсный выход первого триг гера соединен со вторыми входами шестого элемента И, восьмого элемента И и девятого элемента И, вУход которого соединен со вторым входом второго элемента ИЛИ, инверсный выход второго триггера соединен с третьими входами четвертого и пятого элементов И и вто . рым входом седьмого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, прямой выход второго триггера соединен с третьими входами шестого элемента И и восьмого элемента И, выход которого соединен с третьим входом первого элемента И, выход шестого элемента И соединен с третьим входом второго элемента ИЛИ. На чертеже представлена функционал ная схема сумматора по модулю три. Схема содержит первый, второй, тре тий и четвертый элементы И соответственно 1-. Первый триггер 5, пятый, шестой и седьмой элементы И соответственно 6-8, второй триггер 9 восьмой и девятый элементыИ соответственно 10 и 11, первый и второй элементы ИЛИ соответственн.0 12 и 13i вхо ды 14 и 15 сумматора. Первый вход 1 сумматора совместно с первым входом второго элемента И 2, а второй вход 15 совместно с первым входом третьего элемента И 3 являются входами сумматора по модулю три, а вторые входы второго и третьего элементов И 2 и 3 подключены к выходу первого элемента И 1. Первый вход третьего элемента И Ц соединен с выходом триггера 5 и третьим входом пятого элемента И 6, второй вход четвертого элемента И с первыми входами шестого и седьмого элементов И 7 и 8 и выходом третьего элемента И 3, третий вход четвертого элемента ИЛ - с третьим входом пятого элемента И 6 вторым входом седьмого элемента И 8 и инверсным выходом второго триггера 9- Третьи входы шестого элемента И 7 и восьмого элемента И 10 соединены с выходом триггера 9, вторые входы шестого элемента И7со вторыми входами восьмого и девятого элементов 11 и инверсным выходом первого триггера 5- Выход второго элемента И 2 подключен к первому входу с. девятого элемента И 11, к первому входу восьмого элемента И 10 и второму входу элемента И 6. Выходы элементов И 6, 8 и 10 подключены ко входам первого элемента ИЛИ 12, выход которого подключен ко входу триггера 5, а выходы элементов И i, 7 и 11 подключены ко входам второго элемента ИЛИ 12, выход которого подключен ко входу триггера 9. Сумматор по модулю три работает следующим образом. Контролируемый двоичный код поступает параллельно на вХоды 1 и 15Пусть на вход It поступает нечетный разряд двоичного кода, на вход 15 четный. В этом случае во втором триггере 9 хранится младший разряд остатка, в триггере 5 - старший. В процессе работы на входы 1 и 15 могут подаВаться коды 00, 01, 10, 11, а в сумматоре может храниться остаток 00, 01, 10. Входные коды 00 и 11 образуют на выходах схемы совпадения 2 и 3 логический О и изменений состояния триггеров 5 и 9 не вызывают. Входные коды 01 и 10 изменяют код остатка сумматора, и работа сумматора в этомслучае зависит от состояния триггеров 5 и 9При нулевом состоянии триггеров 5 и 9 логические О с их прямых выходом блокируют элементы И t, 6, 7 и 10. При этом входной код 01 образует на выходе третьего элемента И 3 логический О, блокирующий элемент И 8, а на выходе элемента И 2 логическую 1, сигнал которой проходит через элемент И 11 и ИЛИ 13 на вход триггера 9 и устанавливает его в единичное состояние. Таким образом, в сумматоре устанавливается код 01. Входной код 10 при нулевом состоянии триггеров 5 и 9 образуют на выходе элементами 2 логический О, блокирующий элемент И 11, а на выходе элемента И 3 логическую 1, сигнал которой проходит через элемент И 8 и ИЛИ 12 на вход триггера 5 и устанавливает его в единичное состояние, т.е. в сумматоре устанавливается код 10. При остатке в сумматоре 01 логический О с прямого выхода триггера 5 и инверсного выхода триггера 9 блокирует элементы И , 6 и 8. Логический О с выхода элемента И 3 при входном коде 01 блокирует элемент И 7. а сигнал логической 1 поступа ет с выхода элемента И 2 через элеме И 11 и ИЛИ 13 на триггер 9 и через схемы элемента 10 и ИЛИ 12 на триггер 5, устанавливая их соответственно в нулевое и единичное состояние. Таким образом, в сумматоре устанавливается код 10. Логический Q с выхода элемента И 2 при входном коде 10, а остатке в сумматоре 01 блокирует элементы И 10 и 11, а сигнал логичес кой 1 поступает с выхода элемента И 3 через элемент И 7 и ИЛИ 13 на триггер 5 устанавливая его в нулевое состояние. В сумматоре устанавливаетс код 00 без установки промежуточного кода 11, т.е. за один такт работы триггеров. При остатке в сумматоре 10 логический О с прямого выхода триггера 9 и инверсного выхода триггера 5 блокирует элементы И 7 10 и 11. Логический О, с выхода элемента И 3 входного кода 01, блокирует элементы И t и 8, а сигнал логической поступает с выхода элемента И 2 через элементы И 6 и ИЛИ 12 на триггер 5. устанавливая его в нулевое состояние, т.е. в сумматоре устанавливается код 00, как и в предыдущем случае, без установки промежуточного кода 11. Логический О с выхода элемента И 2 входного кода 10 и при остатке в сумматоре 10, блокирует элемент И 6, а сигнал логической единицы поступает с выхода элемента И 3 через элементы И 4 и ИЛИ 13 на триггер 9 и через элементы И 8 и ИЛИ 12 на три гер 5. устанавливая их соитьетственио в единичное и нулевое состояния, т.е. в сумматоре устанавливается код 10. Благодаря тому, что сумматор во всех случаях вычисляет остаток от деления двоичного хода на три за один такт, он обладает примерно в двое большим быстродействием по сравне нию с известным. Формула изобретения Сумматор по модулю три, содержащий первый и второй триггеры, первый и 8 второй элементы ИЛИ, первый, второй и третий элементы И, причем первый вход сумматора соединен с первыми входами первого и второго элементов И, второй вход сумматора соединен с первым входом третьего элемента И и вторым входом первого элемента И, инверсный выход которого соединен со вторыми вхбдами второго и третьего элементов И, выходы первого и второго элементов ИЛИ соединены соответственно со счетными входами первого и второго триггеров, отличающийся тем, что, с целью увеличения быстродействия, в сумматор введены четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, причем прямой выход первого триггера соединен с первыми входами четвертого . и пятого элементов И, выходы которых соединены соответственно с первыми аходаг второго и первого элементов ИЛИ, выход третьего элемента И соединен с первыми входами шестого и седьмого элементов И и со вторым входом четвертого элемента И, выход второго элемента И соединен с первыми входами восьмого и девятого элементов И и вторым входом пятого элемента И, инверсный выход первого триггера соединен со вторыми входами шестого элемента И, восьмого элемента И и девятого элемента И, выход которого соединен со вторым входом второго элемента ИЛИ инверсный выход второго триггера соединен с третьими входами четвертого и пятого элементов И и вторым входом седьмого элемента И, выход которого соединен со вторым входом первого элемента ИЛИ, прямой выход второго триггера соединен с третьими входами шестого элемента И и восьмого элемента И, выход которого соединен с третьим входом первого элемента И, выход шестого элемента И соединен с третьим входом второго элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 60i«155, кл. Н 03 К 23/02, 1976. 2.Авторское свидетельство СССР If StliyS, кл. G Об F 11/00, 1978 (проотип).

Авторы

Даты

1981-12-15—Публикация

1980-02-26—Подача