Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах контроля.

Известен сумматор по модулю три, содержащий .схемы совпадения, два триггера и два элемента ИЛИ, выходами подключенные к входам триггеров, первый вход первой схемы совпадения совместно с первым входом второй схемы совпадения, а второй вход совместно с первым входом третьей схемы совпадения являются входами сумматора по модулю три, вторые входы второй и третьей схемы совпадения подключены к входу первой схе совпадения ClJ

Недостатком такого сумматора по модулю три является низкое быстродействие.,

Наиболее близким по технической сущности к предлагаемому является сумматор по модулю три, содержащий первый и второй триггеры, прямые выходы которых соединены с соответcтвyшI J ми выходами сумматора, первый и второй элементы ИЛИ, первый, второй, третий, четвертьй, пятый, шестой, седьмой, восьмой и девятьй элементы И, первый вход сумматора соединен с первыми входами первого и второго элементов И, второй вход сумматора соединен с первым входом третьего элемента Ни вторым входом первого элемента И, инверсный выход которого соединен с вторыми входами второго и третьего элементов И, вькоды первого и второго элементов ИЛИ соединены соответственно со счетными входами первого и второго триггеров прямой вькод первого триггера соединен с первыми входами четвертого и пятого элементов И, выходы которьи соединены соответственно с первыми входами второго и первого элементов ШЩ, выход третьего элемента И соединен с первыми входами шестого и седьмого элементов И и с вторьм входом четвертого элемента И, выход второго элемента И соединен с первыми входами восьмого и девятого элементов Ни вторыми входами пятого элемента И, инверсный выход первого триггера соединен с вторьми йходами шестого, восьмого и девятого элементов И, выход последнего соединен с .вторым входом второго элемента ИЛИ, инвареный выход второго триггера соединен с третьими входами четвертого л пятого элементов И и вторым входом седьмого элемента И, выход которого соединен с вторым входом первого элемента 1ШИ, прямой вькод второго триггера соединен с третьими входами шестого элемента И и восьмого элемента И, выход которого соединен с

10 третьим входом элемента И, выход шестого элемента И соединен с третьим входом второго элемента ИЛИ С2. Недостатком известного сумматора по модулю три также является низкое

15 быстродействие,

Выстродействйе известного сумматора определяется временим последовательного срабатывания элементов самой длинной цепочки, состоящей из

20 первого, третьего, шестого элементов И, второго элемента ИЛИ, второго триггера, пятого элемента И, первого элемента Ш1К и первого триггера, и равно Т бТ э1-2Тг, где время срабатывания одного логического элемента , Т-pi-- время переключения триггера из одного состояния э ДРУ гое. ..; .

Целью изобретения является повы шейное быстродействие сумматора по модулю три.

Поставленная цель достигается тем, что сумматор по модулю три, содержащий первый и второй триггеры,

35 прямые выходы которых соединены с соответствуюЕрши выходами сумматора содержит первый, второй и третий элементы ИСКЛ10ЧАШ.1ЕЕ ИЛИ, причем Квходы и тактовые входы первого и рого триггеров соединены с выходом первого элемента ИСКЖЧАЩЕЕ ИЛИ, 0-входы первого и второго триггеров соединены с выходами соответственно второго и третьего элементов ИСКЛЮ 5 ЧАЮЩЕЕ ИЛИ, первый вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с пе вьы входом сумматора и с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соеданен

50 прямым выходом первого триггера, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЖ соединен с вторым входом сумматора и с первым входом второго элемента ЙСКШОЧАЩЕЕ ШШ, второй

55 вход которого соединен с прямым выходом второго триггера.

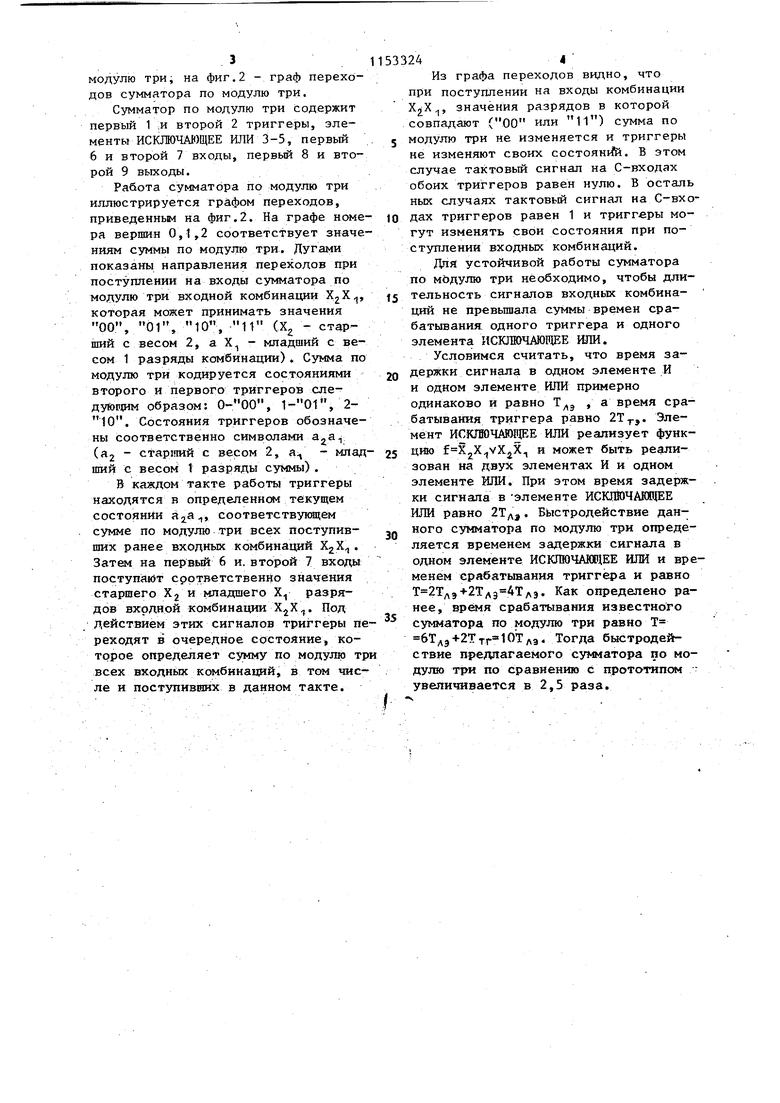

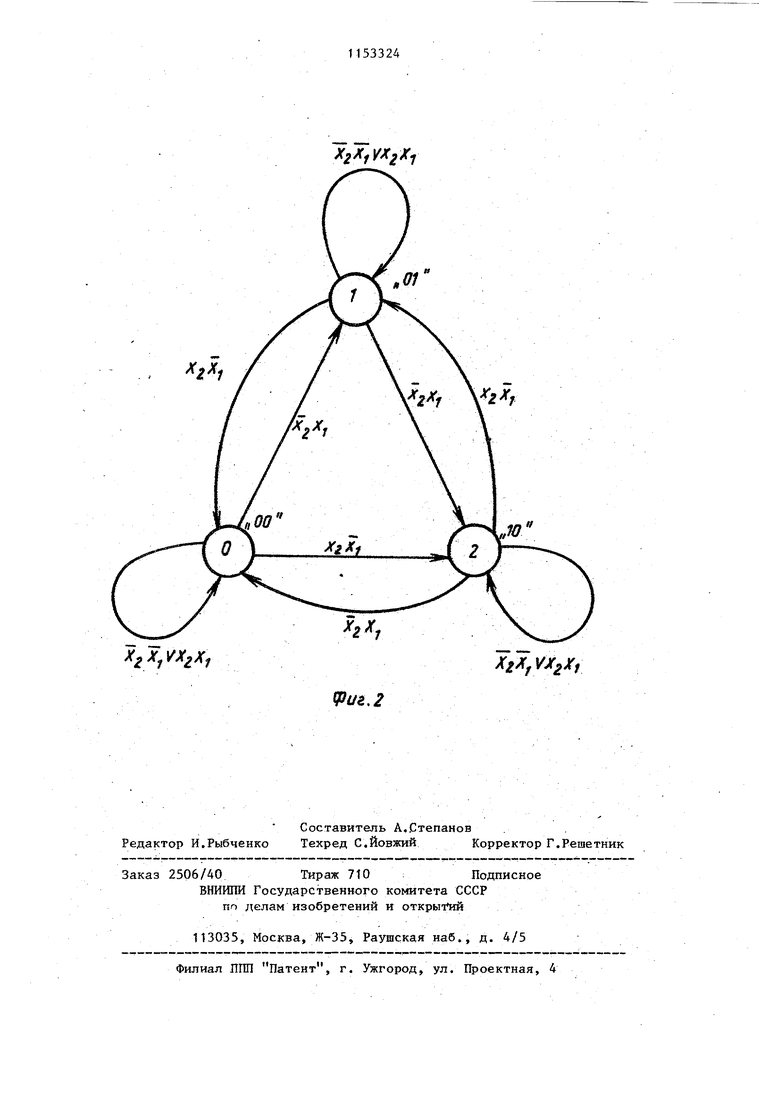

На фиг.1 приведена структурная схема предлагаемого сумматора по 3 модулю три, на фиг,2 - граф переходов сумматора по модулю три. Сумматор по модулю три содержит первый 1 ,и второй 2 триггеры, элементы ИСКЛЮЧА10ЩЕЕ ИЛИ 3-5, первый 6 и второй 7 входы, первый 8 и второй 9 выходы. Работа сумматора по модулю три иллюстрируется графом переходов, приведенньм на фиг.2. На графе номе ра вершин 0,1,2 соответствует значе ниям суммы по модулю три. Дугами показаны направления переходов при поступлении на входы сумматора по модулю три входной комбинации Х2Х которая может принимать значения 00, 01, 10, И (Х - старший с весом 2, а Х - младший с весом 1 разряды комбинации). Сумма по модулю три кодируется состояниями второго и первого триггеров следу1ог им образом: , , . Состояния триггеров обозначены соответственно символами а,а, (л2 - старший с весом 2, а;, - млад ший с весом 1 разряды суммы). Б каждом такте работы триггеры находятся в определенном текущем состоянии , соответствующем сумме по модулю три всех поступивших ранее входных комбинаций XjX, . Затем на первый 6 и. второй 7 входы пос;тупайт срртветственно значения старшего Xj и Ь1ладшего Х разрядов входной комбинации . Под действием этих сигналов триггеры п реходят в очередное состояние, которое определяет сумму по модулю т всех входньпс комбинаций, в том числе и поступивших в данном такте. 244 Из графа переходов видно, что при поступлении на входы комбинации , значения разрядов в которой совпадают (00 или 11) сумма по модулю три не изменяется и триггеры не изменяют своих состоянр|й. В этом случае тактовый сигнал на С-входах обоих триггеров равен нулю. В осталь ных случаях тактовый сигнал на С-входах триггеров равен 1 и триггеры могут изменять свои состояния при поступлении входных комбинаций. Для устойчивой работы сумматора по модулю три необходимо, чтобы длительность сигналов входных комбинаций не превьш1ала суммы времен срабатывания одного триггера и одного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. Условимся считать, что время задержки сигнала в одном элементе И и одном элементе ИЛИ примерно одинаково и равно Т , а время срабатывания триггера равно 21,. Элемент ИСКЛОЧМОДЕБ ИЛИ реализует функцию и может быть реализован на двух элементах И и одном элементе КИИ. При этом время задержки сигнала в элементе ИСКПГОЧАКЯЦЕЕ ИЛИ равно . Быстродействие данкого сумматора по модулю три определяется временем задержки сигнала в одном элементе ИСКЛЮЧАЮОЩЕ ИЛИ и временем срабатывания триггера и равно Т 2Тдэ+2Тдэ АТлЭ Как определено ранее, время срабатывания известного сумматора по модулю три равно Т 6Тдэ+2Ттг ЮТдэ. Тогда быстродействие предлагаемого сумматора по модулю три по сравнению с прототипом увеличивается в 2,5 раза.

Z 1

Vu&,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор по модулю три | 1985 |

|

SU1264163A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 1990 |

|

RU2022453C1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Накапливающий сумматор | 1982 |

|

SU1104506A1 |

| Вычислительный узел цифровой сетки | 1983 |

|

SU1132295A2 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1137541A1 |

СУММАТОР ПО МОДУЛЮ ТРИ, содержащий первый и второй триггеры, прямые выходы которых соединены с соответстнзторр ми выходами сумматора, отличающийся тем, что, .с целью повышения быстродействия, сумматор содержит первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем К-входы и тактовые входы первого и второго триггеров соединены с выходом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, Э-входы первого и второго триггеров соединены с выходами соответственно второго и третьего элементов ИСКЛЮЧАЮиЩЕ ИЛИ, первый вход первого элемента ИСКШЧАКМЦЕЕ ИЛИ соединен с первым входом сумматора и с первым входом третьего Элемента ИСКЛ10ЧАЮ1ЧЕЕ ШШ, второй вхрД которо- го соединен с прямьм выходом первого триггера, второй вход первого элемента ИСКЛЮЧАЮ1ЦЕЕ ИЛИ соединен с вторым входом сумматора и с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом второго триггера. О1 ОЭ СО 1C и

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля двоичных кодов по модулю три | 1971 |

|

SU541175A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сумматор по модулю три | 1980 |

|

SU890393A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-30—Публикация

1983-11-03—Подача