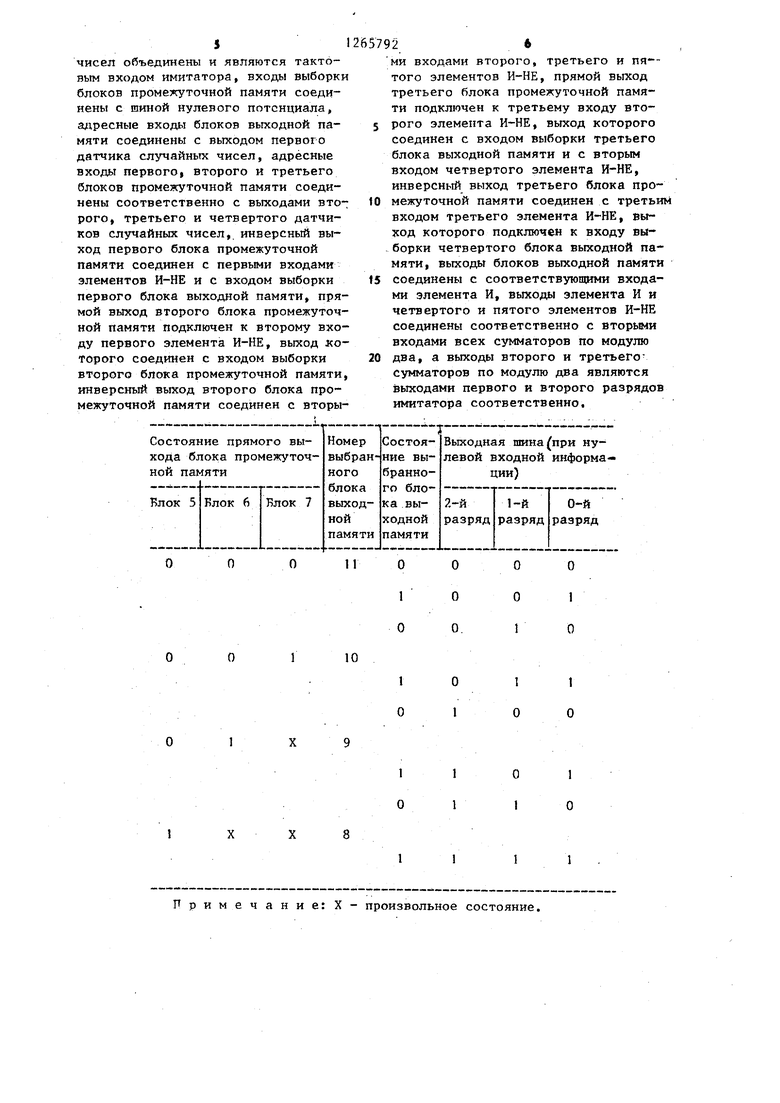

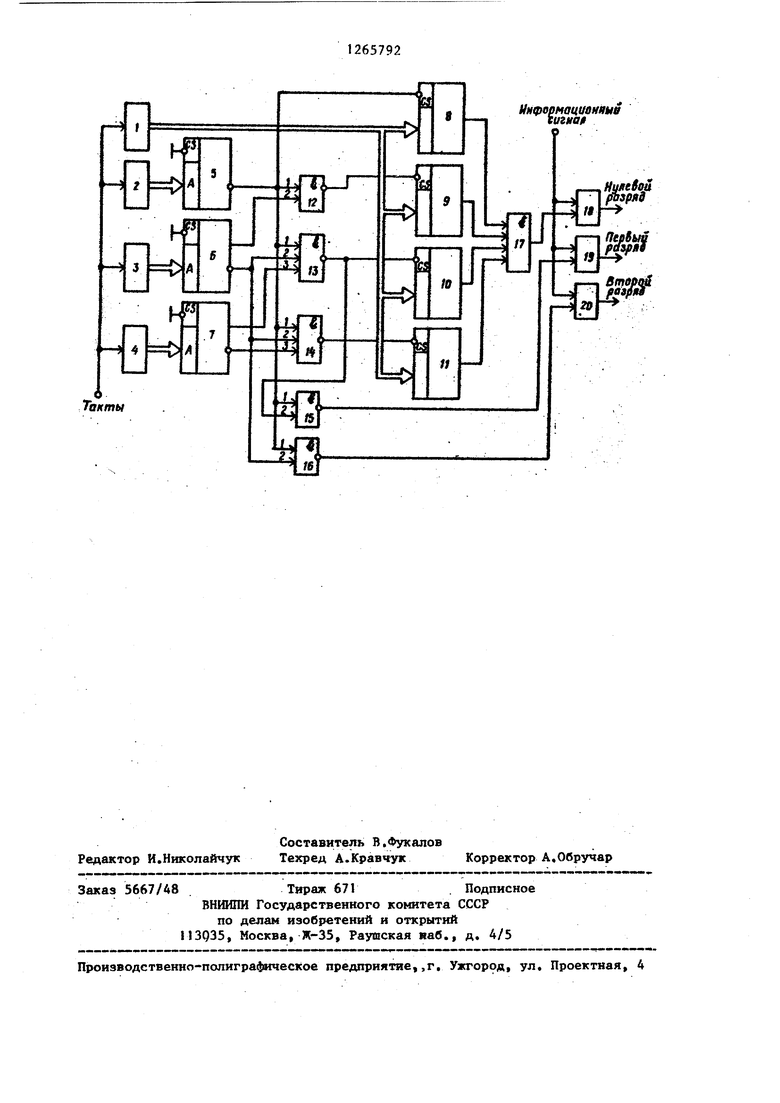

Изобретение относится к вычислительной технике и может быть применено для статистического моделирования систем передачи дискретных сообщений, использующих демодуляторы с многоуровневым квантованием вы ходных сигналов. Цель изобретения - расширение функциональных возможностей имитатора дискретного канала связи за сч реализации многоуровневого квантова ния выходных сигналов. На чертеже приведена функциональ ная схема имитатора. Имитатор содер7«сит четыре датчика 1-4 случайных чисел, три блока 5-7 промежуточной памяти, четыре бл ка 8-11 выходной памяти, пять элементов И-НЕ 12-16, элемент И 17 и три сумматора 18-20 по модулю два. Имитатор работает следующим образом. Предварительно в каждую ячейку блоков 5-11 промежуточной и выходно памяти записываются О или 1, причем количество нулей и единиц в каждом из блоков памяти задается ап риорно в зависимости от принятого закона распределения шума в имитируемом дискретном канале связи. Объ ем памяти каждого из блоков 5-11 со тавляет 2 бит. Блок памяти является выбранным, если на его вход выбо ки подан нулевой потенциал. Таким образом, поскольку входы выборки блоков 5-7 промежуточной па мяти соединены с общей шиной нулево го потенциала, эти блоки оказываются выбранными постоянно. Подаваемые на тактовый вход имитатора тактовью импульсы информационного сигнала поступают на входы всех датчиков 1-4 случайных чисел, которые в соответствии с частотой тактов независимо друг от друга ген рируют случайные числа, равномерно распределенные в интервале от О до (), С выходов датчиков -4 случайные числа по N-разрядным шинам поступают на адресные входы соответствующих блоков 5-11 памяти. Случайное число, поступающее на адресный вход блока памяти, определяет адрес одной из 2 ячеек блока памяти. Если блок памяти оказывается вы бранным, то записанный в данной ячейке бит (О или 1) снимается с прямого выхода блока памяти, а с его инверсного выхода снимается ин- ; вертированный бит (1 или О). С выходов блоков 5-7 промежуточной памяти случайная комбинация нулей и единиц через элементы И-НЕ 1214 поступает на входы выборки соответствующих блоков 8-11 выходной памяти. Если с инверсного выхода блока 5 промежуточной памяти снимается О, то на вход выборки блока 8 выходной памяти и на первые входы всех элементов И-НЕ подается сигнал низкого (нулевого) уровня. В этом случае с выходов элементов И-НЕ 1254 снимается сигнал высокого уровня, который подается соответственно на входы выборки блоков 9-11 выходной памяти. Таким образом, выбранным оказывается только блок 8 выходной памяти. Если с ;йнверсного выхода блока 5 промежуточной памяти снимается . 1, то блок 8 выходной памяти является невыбранным. Если одновременно с прямого выхода блока 6 промежуточной памяти снимается 1, то с выхода элемента И-НЕ 12 снимается О, который поступает на вход выборки блока 9 промежуточной памяти. Сигнал нулевого уровня с HHBjtpcHoro выхода блока 6 промежуточной памяти поступает на вторые входы элементов И-НЕ I3 и 14, с выходов которых в этом слзгчае снимается 1, и сигнал высокого уровня поступает иа входы выборки блоков 10 и 11 выходной памяти, В этом случае оказывается выбранным только блок 9 выходной памя-. ти. Полная информация о выборе блока выходной памяти в зависимости от комбинации иулей и единиц на выходах блоков промежуточной памяти представлена в таблице истинности, причем в каждый момент времени оказывается выбранным только один из блоков 8-11 вькодной памяти. С выхода выбранного блока выход- ной памяти бит О или 1, записанный в той ячейке памяти этого блока, адрес которой определяется случайным числом, поступающим с выхода датчика 1 случайных чисел на адресный вход выбранного блока выходной памяти, поступает на один из входов элемента И 17j на остальные входь которого с выходов невыбранных бло ков выходной памяти поступают биты 1, Таким образом, на каждом такт с выхода элемента И 17 на второй ; вход сумматора 18 поступает бит О или 1, представляющий собой младший (нулевой) разряд цифрового шум Сумматор 18 осуществляет сложение п модулю два информационного сигнала (о или 1), поступающего на первый вход сумматора, с битом О или } нулевого разряда шума, поступающим с выхода элемента И 17 на второй вход сумматора 18. Аналогично работают сумматоры 19 и 20, осуществляющие сложение по мо дулю два информационного сигнала с битами первого и второго разрядов шума соответственно. С выходов сумматоров 18-20 на каждом такте снимается трехбитовая комбинация, определяющая число О до 7, соответствующее однсжу из вос ми уровней квантования сигнала на выходе демодулятора. № итатор должен формировать на выходе трехбитовые числа ,7 с определенными вероятностями QO). Пусть эти вероятности заданы в соот ветствии с характеристиками сигнала и шума в канале связи. Исходя из таблицы истинности, ве роятности fl(i) могут быть вьфажены через вероятности Р: появления бита О на прямом выходе j-ro блока памяти: OAO)P,.. Р,. Р„; QU)P5-Pfi-P7(l-R,,); 0(2)Р, р(1-Р,).р.; о.13)р,-PS (i-P7)(i-P«); а(А)ру.Ч1-Рб)-р9; а(5)р, -(i-pfi) -d-p); Q(6) (1-PfbP8; a{7)(i-p5)-(i-pg). Отсюда нетрудно получить выражения для PJ: (6)-a(7); Р. Si hSlslчРу) Р .1- . р.. Р Р -SI).., . 92 Р „0(2; 1Т:р;У р. Рб Р .0(01. PfPfifr Вероятность определяется соотношением числа нулей и единиц, записанных в J-M блоке памяти: р.- Ki 1 . где Ki- число нулей в j-м блоке памяти. Отсюда необходимое число нулей в J-M блоке памяти может быть определено по формуле Кг 2 Р.. где символ {.. .J означает округление до ближайшего целого числа. Следовательно, если по приведенной методике рассчитать необходимое число нулей в каждом блоке памяти и соответственно эти блоки заполнить, то при нулевом информационном сигнале на выходе имитатора формируются трехбитовые числа от О до 7 . с вероятностями, близкими к заданным Q(i)« Погрешность воспроизведения вероятностей П(|) обусловливается округлением К; до ближайшего целого числа, причем увеличение N эта погрешность может быть сделана сколь угодно малой. Формула изобретения Имитатор дискретного канала связи, содержащий первый датчик случайных чисел, первый блок промежуточной памяти, элемент И и первый сумматор по модулю два, первый вход которого является информационным входом имитатора, а выход - выходом нулевого разряда имитатора, отличающийся тем, что, с целью расширения функциональных возможностей имитатора за счет реализации многоуровневого квантования выходных сигналов, он дополнительно содержит второй, третий и четвертый датчики случайных чисел, второй и третий блоки промежуточной памяти, четыре блока ыходной памяти, пять элементов И-НЕ и второй и третий сумматоры по модую два, первые входы которых объедиены с информационным входом имитатора, входы всех датчиков случайных

чисел объединены и являются тактовым входом имитатора, входы выборки блоков промежуточной памяти соединены с шиной нулевого потенциала, адресные входы блоков выходной памяти соединены с выходом первого датчика случайных чисел, адресные входы первого, второго и третьего блоков промежуточной памяти соединены соответственно с выходами второго, третьего и четвертого датчиков случайных чисел,, инверсный выход первого блока промежуточной памяти соединен с первыми входами элементов И-НЕ и с входом выборки первого блока выходной памяти, прямой выход второго блока промежуточной памяти подключен к второму входу первого элемента И-НЕ, выход которого соединен с входом выборки второго блока промежуточной памяти, инверсный выход второго блока промежуточной памяти соединен с вторы657926

ми входами второго, третьего и пя-того элементов И-НЕ, прямой выход третьего блока промежуточной памяти подключен к третьему входу вто5 рого элемента И-НЕ, выход которого соединен с входом выборки третьего блока выходной памяти и с вторым входом четвертого элемента И-НЕ, инверсный выход третьего блока про10 межуточной памяти соединен с третьим входом третьего элемента И-НЕ, выход которого подключен к входу выборки четвертого блока выходной памяти, выходы блоков выходной памяти

ts соединены с соответствуюпдами входами элемента И, выхода элемента И и четвертого и пятого элементов И-НЕ соединены соответственно с вторыми входами всех сумматоров по модулю

20 два, а выходы второго и третьегосумматоров по модулю два являются выходами первого к второго разрядов имитатора соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1989 |

|

SU1651293A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Цифровой фильтр | 1988 |

|

SU1617635A1 |

| Цифровой имитатор случайных сигналов | 2019 |

|

RU2722001C1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Датчик случайных чисел | 1983 |

|

SU1200285A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| УСТРОЙСТВО МОДЕЛИРОВАНИЯ НЕПРЕРЫВНОЙ СЛУЧАЙНОЙ ВЕЛИЧИНЫ ПО ГИСТОГРАММЕ | 2004 |

|

RU2287177C2 |

| Устройство для многоуровневой дельта - модуляции | 1988 |

|

SU1674377A1 |

Изобретение относится к вычислительной технике и может быть применено для статистического моделирования систем передачи дискретных сообщений, использующих демодуляторы с многоуровневым квантованием выходных сигналов. Цель изобретения - расширение функциональных возможностей имитатора дискретного канала связи за счет реализации многоуровневого квантования выходных сигналов. Цель достигается введени§ ем в устройство датчиков случайных чисел, блоков промежуточной памяти, (Л блоков выходной памяти, элементов И-HE сумматоров по модулю два. 1 ил, 1 табл.

О

Примечание: х- произвольное состояние.

о

о

1 о

0.

1

о 1

1 о

1 о

1 о

о 1

о

Ннфоомацивмаыу

tUZKOf

Нияейоа

Авторы

Даты

1986-10-23—Публикация

1985-01-03—Подача