Изобретение относится к вычислительной технике и может быть использовано для статистического моделирования дискретных каналов связи.

Цель изобретения - расширение функциональных возможностей путем моделирования канала связи с квантованием выходного сигнала.

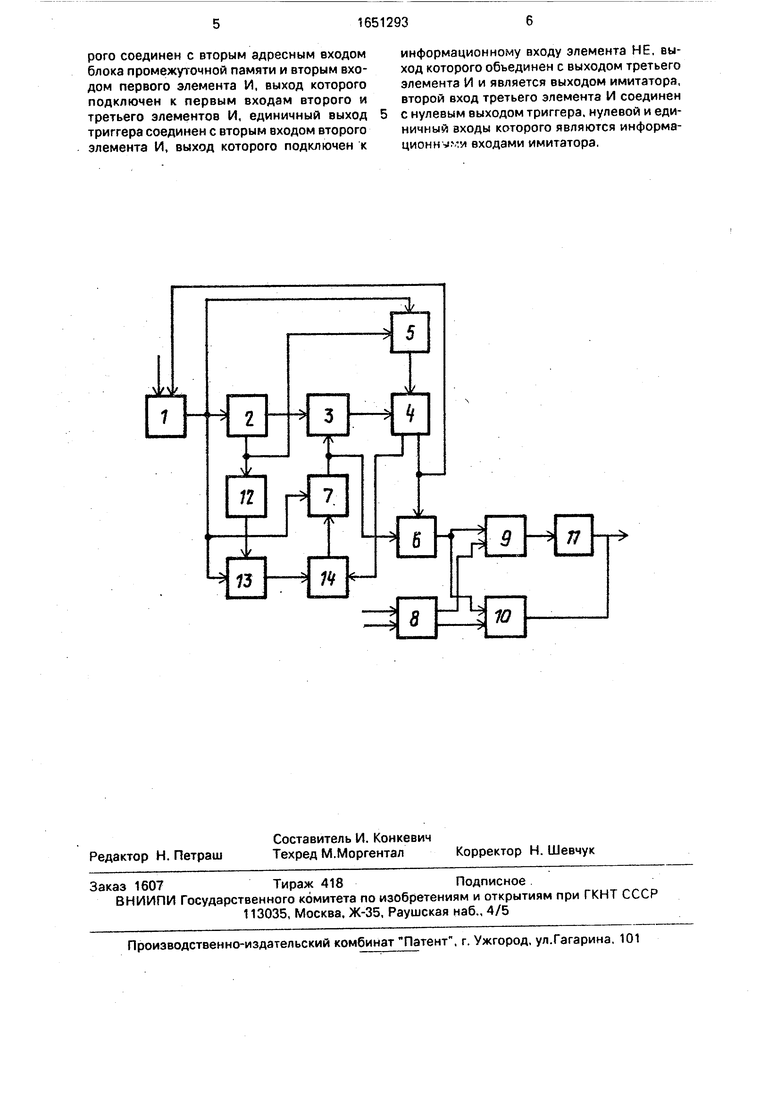

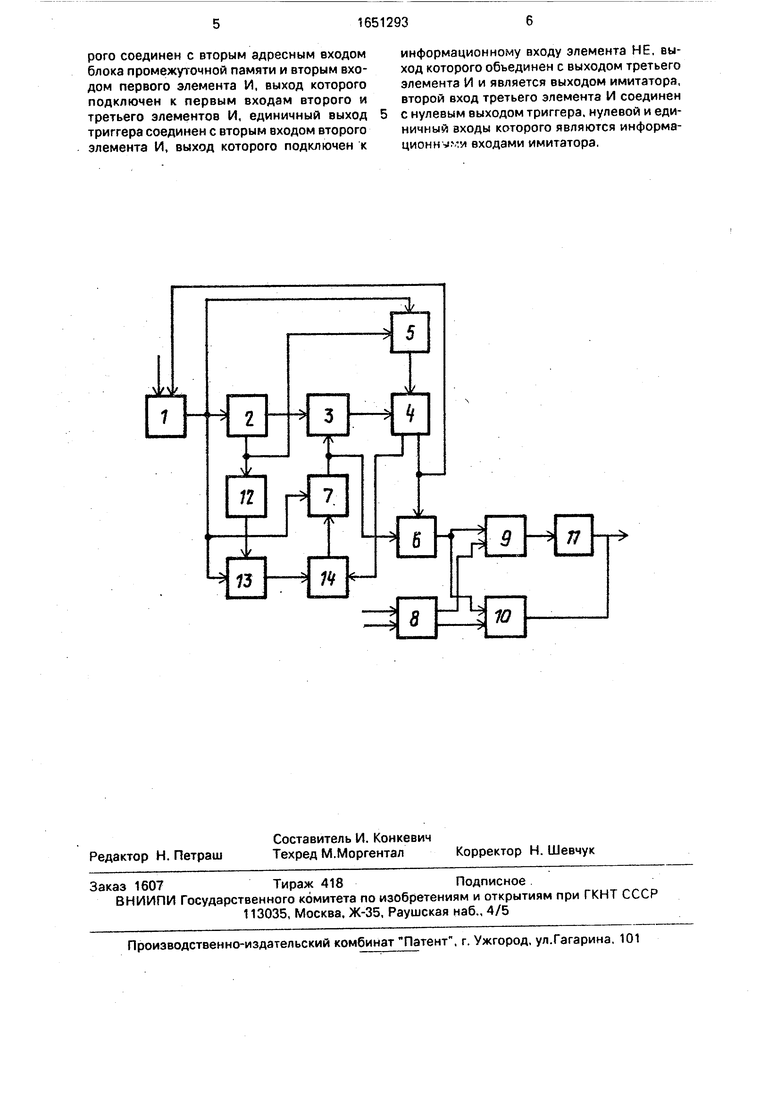

На чертеже приведена схема имитатора дискретного канала связи.

Имитатор дискретного канала связи содержит блок 1 синхронизации,генератор 2 марковской последовательности, блок 3 промежуточной памяти, пороговый сумматор 4, генератор 5 случайных чисел, первый элемент И 6, счетчик 7 тактов, триггер 8, второй элемент И 9, третий элемент И 10, элемент НЕ 11, линию 12 задержки, генератор 13 тактовых импульсов и четвертый элемент И 14.

Имитатор дискретного канала связи работает следующим образом.

На первый вход блока 1 синхронизации поступают внешние синхроимпульсы, сопровождающие информационные символы, поступающие на первый и второй входы триггера 8. Блок 1 вырабатывает сигнал, поступающий на вход синхроимпульса имитатора и запускающий генератор 5 случайных чисел, обнуляющий счетчик 7 тактов, останавливающий генератор 13 тактовых импульсов и запускающий генератор 2 марковской последовательности. После окончания поиска состояния цепи Маркова на втором выходе генератора 2 появляется сигнал, останавливающий генератор 5 случайных чисел и поступающий на вход линии 12 задержки, а с выхода генератора 5 случайных чисел на второй вход сумматора 4 поступает случайное, равномерно расоре- деленое в интервале от 0 до 1 число.

Блок 3 промежуточной памяти представляет собой матрицу вероятностей размеров 1x8, где I - число состояний цепи

«

Ё

Os

сл

N Ю 00

Маркова, а в каждой ячейке i-й строки, где ,l, хранится вероятность Pik, где - номер столбца, и

P (/о)

есть сумма вероятностей перехода символа О в символы 0,1..k. С первого выхода генератора 2 марковской последовательности на первый адресный вход блока 3 поступает код I, соответствующий номеру состояния цепи Маркова и номеру строки матрицы вероятностей блока 3, а на второй адресный вход блока 3 со счетчика 7 поступает код k номера столбца матрицы вероятностей. На первом такте , и из блока 3 промежуточной памяти на первый вход сумматора 4 поступает значение вероятности , равное вероятности перехода символа О в символ

0для 1-го состояния цепи Маркова.

Пороговый сумматор 4 представляет собой сумматор, первый выход которого является сигналом переноса старшего разряда, а второй выход - его инверсией. На первом выходе сумматора 4 появляется сигнал в том случае, если сумма чисел на входах сумматора не меньше единицы. В противном случае с второго выхода порогового сумматора на первый вход элемента И 14 поступает потенциал, разрешающий прохождение тактовых импульсов с выхода генератора 13 на вход счетчика 7 тактов. Генератор 13 тактовых импульсов запускается сигналом с второго выхода генератора 3 марковской последовательности и задержанным на один такт в линии задержки. Период следования тактовых импульсов равен времени выбора значения вероятности из блока 3 и суммирования его с значением случайного числа из генератора 5.

Таким образом, на каждом такте происходит увеличение содержимого счетчика тактов на единицу, выбор следующего значения вероятности в блоке 3. суммирование его со случайным числом в блоке 4. Этот процесс продолжается до тех пор, пока их сумма станет не меньше единицы, а счетчик 7 при этом будет хранить код числа k. С второго выхода сумматора 4 перестает поступать разрешающий потенциал на элемент И А, а на первом выходе сумматора 4 появляется сигнал, подготавливающий блок

1синхронизации к следующему циклу работы имитатора и разрешающий прохождение кода k с выхода счетчика 7 тактов через элемент И 6 на первые входы элементов И 9 и 10.

Если на вход имитатора поступает символ О, го с второго выхода триггера 8 на второй вход элемента И 10 поступает разрешающий потенциал и код k проходит через элемент t/l 10 на выход имитатора. Если на информационный вход имитатора поступает символ 1, то с первого выхода триггера 8

разрешающий потенциал поступает на второй вход элемента И 9 и код k через элемент И 9 поступает на элемент Н Е 11, где каждый разряд кода инвертируется и поступает на выход имитатора. Таким образом, каждому

0 информационному символу 0 или 1 в зависимости от состояния цепи Маркова, переходных вероятностей, соответствующих данному состоянию, и значению случайного числа становится в соответствие число k или

5 k, соответствующее числу тактов поиска вероятности из строки матрицы вероятностей такой, что сумма этой вероятности и случайного числа не меньше единицы. При этом k и k принимают целые значения от 0 до 7.

0

Формула изобретения Имитатор дискретного канала связи, содержащий генератор марковской последовательности, блок промежуточной памяти,

5 пороговый сумматор, генератор случайных чисел, первый элемент И, причем вход синхроимпульса имитатора соединен с входом запуска генератора марковской последовательности, первый выход которого подклю0 чен к первому адресному входу блока промежуточной памяти, выход которого соединен с входом первого слагаемого порогового сумматора, первый выход которого подключен к первому входу первого элемен5 та И, а вход второго слагаемого порогового сумматора соединен с выходом генератора случайных чисел, вход останова которого подключен к второму выходу генератора марковской последовательности, о т л и ч а0 ю щ и и с я тем, что. с целью расширения функциональных возможностей путем моделирования канала связи с квантованием выходного сигнала, в него введены счетчик тактов, триггер, второй, третий и четвертый

5 элементы И, линия задержки, генератортак- - товых импульсов и элемент НЕ, причем вход обнуления счетчика тактов и вход останова генератора тактовых импульсов объединены с входом запуска генератора

0 случайных чисел и подключены к входу синхроимпульса имитатора, второй выход порогового сумматора подключен к первому входу четвертого элемента И, второй вход которого соединен с выходом генератора

5 тактовых импульсов, вход запуска которого подключен к выходу линии задержки, вход которой соединен с вторым выходом генератора марковской последовательности, выход четвертого элемента И подключен к счетному входу счетчика тактов, выход которого соединен с вторым адресным входом блока промежуточной памяти и вторым входом первого элемента И, выход которого подключен к первым входам второго и третьего элементов И, единичный выход триггера соединен с вторым входом второго элемента И, выход которого подключен к

информационному входу элемента НЕ, выход которого обьединен с выходом третьего элемента И и является выходом имитатора, второй вход третьего элемента И соединен с нулевым выходом триггера, нулевой и единичный входы которого являются информационными входами имитатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1989 |

|

SU1661788A1 |

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Имитатор дискретного канала связи | 1980 |

|

SU951318A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| Имитатор дискретного канала связи с ошибками синхронизации | 1980 |

|

SU934479A2 |

| Имитатор дискретного канала связи | 1986 |

|

SU1425702A1 |

| Имитатор дискретного канала связи | 1988 |

|

SU1562926A1 |

| Имитатор дискретного канала связи | 1982 |

|

SU1075267A2 |

Изобретение относится к вычислительной технике и может быть использовано для статистического моделирования дискретных каналов связи. Цель изобретения - расширение функциональных возможностей за счет моделирования канала связи с квантованием выходного сигнала. Для этого в имитатор введены счетчик тактов, триггер, три элемента И, элемент НЕ, генератор тактовых импульсов и линия задержки. Эти элементы позволяют при подаче на вход имитатора символов 0 или 1 реализовать методом статистических испытаний появление на выходе имитатора символов 07 в зависимости от значений переходных вероятностей, хранящихся в блоке промежуточной памяти. 1 ил.

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Имитатор дискретного канала связи | 1978 |

|

SU807312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-23—Публикация

1989-06-19—Подача