Изобретение относится к радиотехнике и может быть использовано для анализа помехоустойчивости систем обработки дискретных данных.

По основному авт.св. 807312 известен имитатор дискретного канала связи, содержащий сумматор по модулю два, выход и первый вход которого являются соответственно выходом и первым входом имитатора, блок синхронизации, первый вход которого является вторллм входом имитатора, а выход блока синхронизации соединен с входе генератора марковской последовательности , первый выход которого соединен с вторым входсм блока синхронизации и с входом датчика случайных чисел, блок промежуточной памяти, пороговый сумматор и элемент И, выход которого соединен с вторым входом сумматора по модулю два, а первый и второй входы элемента И подключены соответственно к выходу порогового сумматора и к второму выходу генератора марковской последовательности, третий выход которого через блок промежуточной памяти соединен с первым входом порогового сумматора, второй вход которого подключен к выходу датчика случайных чисел (1.

Недостатком данного имитатора является то, что он моделирует только ошибки трансформации и не учитывает ошибки дробления, которыр проявляются в разбиении переданного символа на ряд более коротких импульсов, что снижает достоверность моделирования дискретного канала.

Цель изобретения - повышение достоверности моделирования дискретного канала связи.

Это достигается тем, что в имитатор дискретного канала связи дополнительно введены два триггера, генератор случайного числа, дополнительный генератор марковской последовательности, генератор тактовых импульсов, элемент запрета, сдвигающий регистр, дешифратор, элемент ИЛИ, элемент задержки, ключ и коммутатор, один информационный вход которого непосредственно, а другой через дополнительный генератор марковской последовательности соединен с выходом генератора случайного числа, а выход с входом дешифратора и управляющим входом элемента запрета, информационный вход которого

подключен к выходу генератора тактов импульсов, а выход элемента запрета соединен с управляющим входом сдвигающего регистра, выход которого соединен с первЕлм входом элемента ИЛИ, а также через последовательно соединенные элемент задержки , ключ и триггер подключен к одному иэ входов сумматора по модулю два, нулевой выход дешифратора соединен с управляющим входом ключа и вторым входсм эл емента ИЛИ, а остальные выходы дешифратора подключены к разрядным входам сдвигающего регистра соответственно, выход элемента ИЛИ соединен со счетным выходом второго триггера, единичный и нулевой выходы которого подключены соответственно к управляющему входу коммутатора и входу генератора случайного числа.

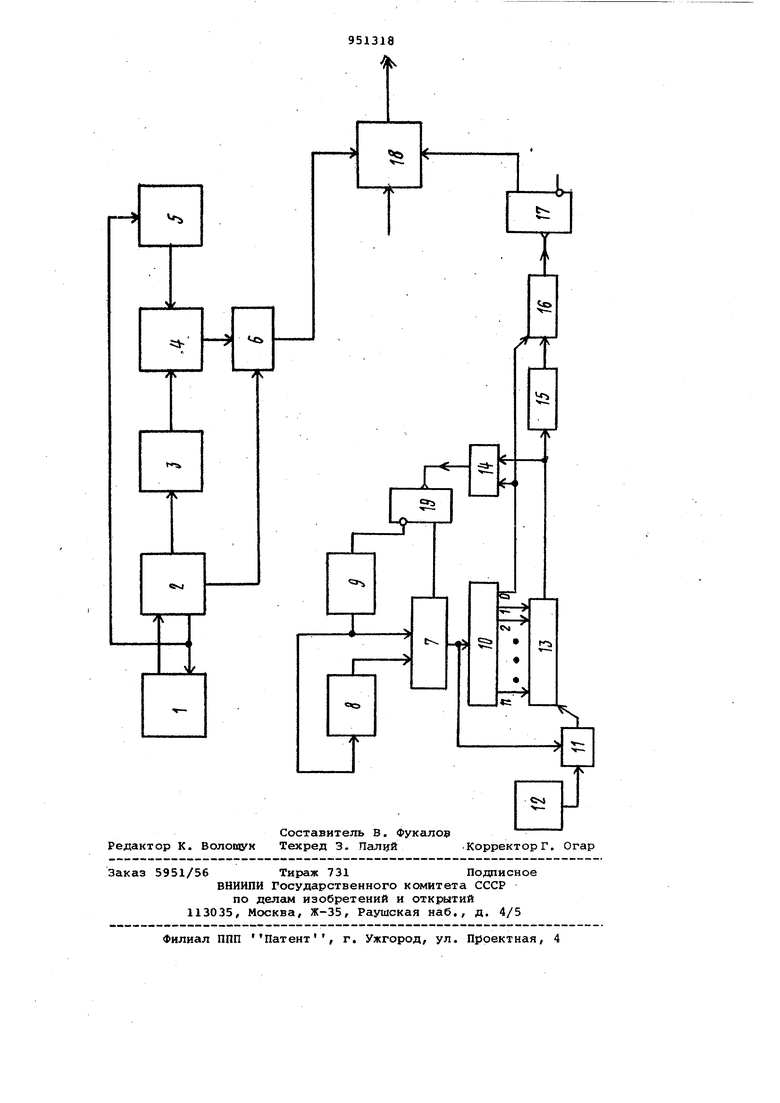

На чертеже п иведена структурная схема устройства.

Имитатор дискретного канала связи содержит блок 1 синхронизации, генератор 2 марковской последовательности, блок 3 промежуточной памяти, пороговый сумматор 4, датчик 5 случайных чисел, элемент И 6, коммутатор 7, дополнительный генератор 8 марковской последовательности, генератор 9 случайного числа, дешифратор 10, элемент 11 запрета, генератор 12 тактовых импульсов, сдвигающий регистр 13, элемент ИЛИ 14,элемент 15 задержки, ключ 16, первый триггер 17, сумматор 18 по модулю два, второй триггер 19.

Устройство работает следующим образом.

При включении питания триггеры 17 и 19 устанавливаются в нулевое состояние. Тогда сигналом с нулевого выхода триггера 19 запускается генератор 9 случайного числа, с выхода которого код равнораспределенного случайного числа, которое опредсгляет время между дроблениями, поступает на вход коммутатора 7,а также запускает генератор 8 марковской последовательности, который вырабатывает код числа, определяющего время дробления и распределенного по логарифмически нормальному закону. Поскольку триггер 19 находится в нулевом состоянии, то код числа с генератора 9 поступает через коммутатор 7 на вход дешифратора 10, а также на вход элемента 11 запрета, запрещающего подачу тактовых импульсов с генератора 12 на сдвигающий вход регистра 13 на время записи в него информации с дешифратора 10. Когда в сдвигающем регистре 13 продвигаемая единица достигает выхода, она поступает на вход элемента 15 задержки и через элемент ИЛИ 14 по счетному входу перебраснвает триггер 19 в единичное состояние. В этом состоянии триггера 19 ксаи1мутатор 7 пропускает код числл с генератора 9. Если окажется, что код числа соответствует времени дробления равного нулю, то на нулевом выходе дешифратора 10 появляется сигнал, который через элемент ИЛИ 1 перебрасывает триггер 15 в нулевое состояние, который снова запускает генератор 9 случайной последовательности, и процесс Повторяется. Кроме того, сигнал с нулевого выхода дешифратора 10 поступает на ключ 16, который запрещает подачу задержанной единицы с выхода элемента задержки 1 на счетный вход триггера 17, и он не изменяет своего состояния. Если же время дробления не равно нулю, то через время задержки, равное суммарному времени переключения элемент.а ИЛИ 14, триггера 19, коммутатора 7, дешифратора 10, задержанная единица предыдущего цикла перебрасывает триггер 17 в единичное состояние. Таким образсм, на выходе триггера 17 - последовательность единиц и нулей с определенной длительностью, которая поступает на вход сумматора 18, где происходит сложение ее с инфО ационными сигналами и сигналами трансформации, которое вырабатывается следующим образом. Блок 1 синхронизации вырабатывает сигнал, запускающий генератор 2 марковской последовательности. На первом такте работы генератора 2 на втором его выходе появляется сигнал, который опрашивает элемент И 6. Поскольку на входы порогового сумматора ничего не подавалось, то на выходе элемента И 6 - низкий уровень и на вход сумматора 18 по модулю два сигнал не поступает. После окончания цикла поиска на выходе генератора 2 появляется код состояния цепи Маркова, который задает адрес ячейки блока 3 памяти, в котором хранитс соответствующая условная вероятность ошибки. Одновременно на третьем выходе генератора 2 марковской последовательности появляется сигнал, который подготавливает блок 1 к новому циклу и опрашивает датчик 5 случайных чисел, который вырабатывает случайное равнораспределенное число. Это число поступает на первый вход порогового сумматора 4, на второй вход которого поступает из блока 3 памяти соответствующая условная вероятность ошибки. Сигнал на выходе порогового сумматора 4 появляется в том случае, если сумма слагаемых больше единицы. Таким образом, если выполняются все условия, то на входе элемента И 6 появляется единица. В следующем такте снова запускается генератор 2 и на втором такте его работы опрашивает элемент И 6. В результате на выходе элемента И 6 появ ляется сигнал ошибки, которыЯ поступает на вход сумматора 18 по модулю два, на выходе которого получается смесь информационных символов, сшибо трансформации и ошибок дробления. Устройство позволяет моделировать как сшибки трансформации, так и ошибки дробления, что приводит к повышению достоверности моделирования дискретного канала связи. Формула изобретения I . Имитатор дискретного канала связи по авт.св. № 807312, отличающийся тем, что, с целью повышения достоверности моделирования дискретного канала связи, в него дополнительно введены два триггера, генератор случайного числа, дополнительный генератор марковской последовательности , генератор тактовых импульсов, элемент запрета, сдвигаю щий регистр, дешифратор, элемент ИЛИ элемент задержки, ключ и коммутатор, один информационный вход которого непосредственно, а другой чере дополнительный генератор марковской последовательности соединены с выходом генератора случайного числа, а выход - с входом дешифратора н управляющим входом элемента запрета, информационный вход которого подключен к выходу генератора тактовых импульсов, а выход элемента запрета соединен с управляющим входом сдвигающего регистра, выход которого соединен с первым входом элемента ИЛИ, а также через последовательно соединенные элемент задержки, ключ и триггер подключен к одному из входов сумматора по модулю два, нулевой выход дешифратора соединен с управляющим входом ключа и вторым входом элемента ИЛИ, а остальные выходы дешифратора подключены к разрядным входам сдвигающего регистра соответственно, выход элемента ИЛИ соединен со счетным входом второго триггера, единичный и нулевой выходы которого подключены соответственно к управляющему входу коммутатора и входу генератора случайного числа. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 807312, кл, G 06 F 15/20, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Имитатор дискретного канала связи | 1981 |

|

SU964651A2 |

| Имитатор дискретного канала связи с ошибками синхронизации | 1980 |

|

SU934479A2 |

| Имитатор дискретного канала связи | 1984 |

|

SU1223246A2 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755293A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СИСТЕМЫ СВЯЗИ | 2005 |

|

RU2286597C1 |

| Устройство для моделирования систем передачи данных | 1983 |

|

SU1151983A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1755292A1 |

| Имитатор дискретного канала связи | 1982 |

|

SU1075267A2 |

| Имитатор дискретных каналов связи | 1979 |

|

SU842827A1 |

| Имитатор дискретного канала связи | 1989 |

|

SU1651293A1 |

Авторы

Даты

1982-08-15—Публикация

1980-12-15—Подача