ческой сумме фазовых ошибок всех измерений. Мультиплексор 13, связанный со счетчиками 7-12, формирует сигналы постоянных частот на выходах, под действием которых устройство выраба- тывает управляющее воздействие, соотйествующее пропорционально-интегрально-дифференциальному закону по фазе. При изменении значений частот

65844

на выходах мультиплексора 13 в зависимости от значений кода в первом блоке 15 памяти коэффициенты усиления пропорциональной и дифференциаль. ной составляющих меняются при различной фазовой ошибке, т.е. устройство может использоваться как регу лятор с переменными коэффициентами. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоканального аппарата магнитной записи | 1987 |

|

SU1432602A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Двухступенчатый параллельно-последовательный регенератор | 1985 |

|

SU1246394A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для моделирования процесса синхронизации коротковолновой радиолинии | 1982 |

|

SU1073892A1 |

| Адаптивное устройство для сжатия цветовых сигналов телевизионных изображений | 1988 |

|

SU1631752A1 |

| Устройство для декодирования данных | 1988 |

|

SU1629912A1 |

| Цифровой трехфазный генератор | 1988 |

|

SU1667219A1 |

Изобретение относится к области накопления информации и может быть использовано в прецизионных электроприводах аппаратов точной магнитной записи. Для повьшения точности поддержания скорости и фазы магнитного носителя в устройство дополнительно введены четыре счетчика, триггер, второй делитель частоты, мультиплексор, два блока памяти, четыре элемента И, два элемента ИЛИ, формирователь. В соответствующих счетчиках накапливаются коды, пропорциональные фазовой ошибке, первой разности фазовой ошибки и алгебраи(Л to Ot) ел 00 4 4

Изобретение относится к приборостроению, а именно к устройствам управления скоростью движения носителя магнитной записи, и может быть использовано в прецизионных электроприводах аппаратов точной магнитной записи.

Цель изобретения - повыщение точности стабилизации скорости движения носителя магнитной записи.

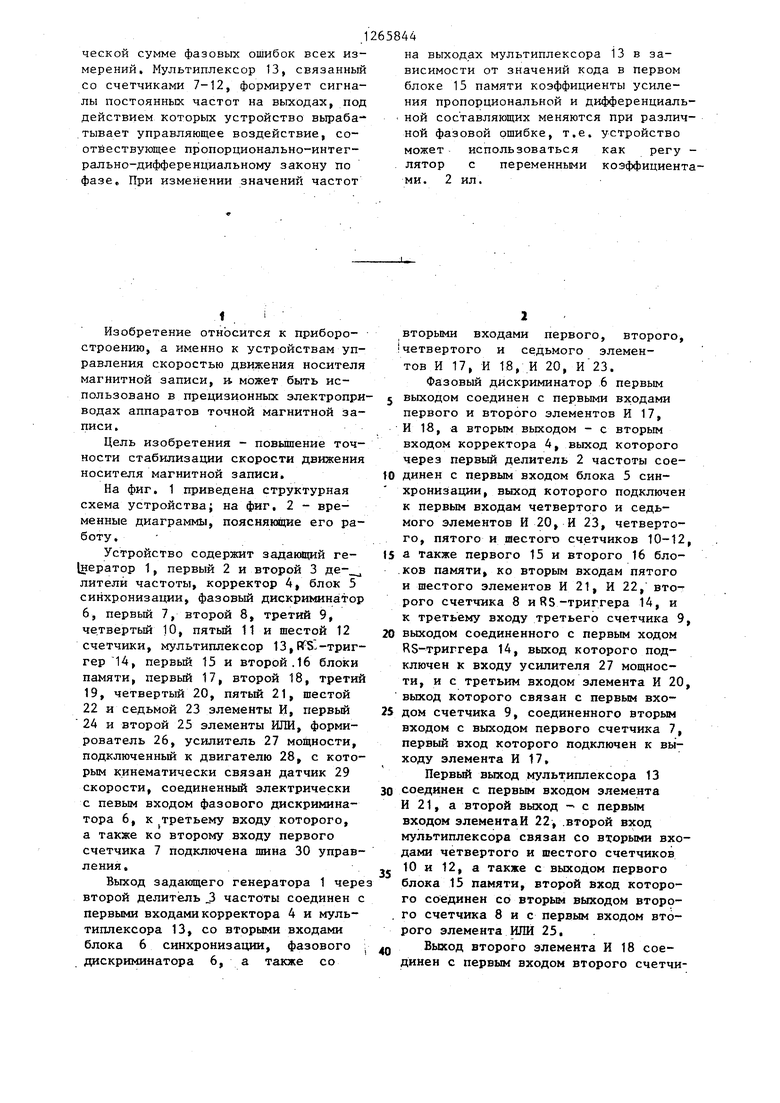

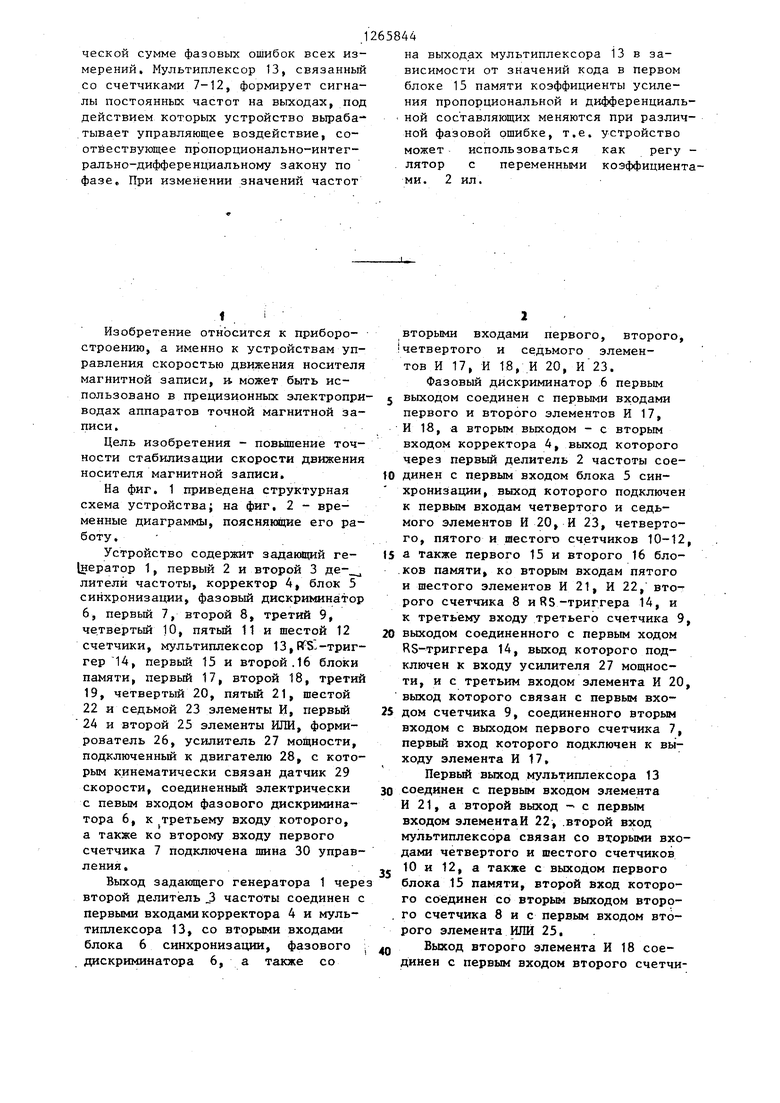

На фиг. 1 приведена структурная схема устройства; на фиг, 2 - временные диаграммы, поясняющие его работу,

Устройство содержит задакяций ге нератор 1, первый 2 и второй 3 де-, лители частоты, корректор 4, блок 5 синхронизации, фазовый дискриминатор 6, первый 7, второй 8, третий 9, четвертый 10, пятый 11 и шестой 12 счетчики, мультиплексор 13, RfS -триггер14, первый 15 и второй.16 блоки памяти, первый 17, второй 18, третий 19, четвертый 20, пятый 21, шестой 22 и седьмой 23 элементы И, первый 24 и второй 25 элементы ИЛИ, формирователь 26, усилитель 27 мощности, подключенный к двигателю 28 с которым кинематически связан датчик 29 скорости, соединенный электрически с певым входом фазового дискриминатора 6, к третьему входу которого, а также ко второму входу первого счетчика 7 подключена шина 30 управления.

Выход задающего генератора 1 чере второй делит апь 3 частоты соединен с первыми входами корректора 4 и мультиплексора 13, со вторыми входами блока 6 синхронизации, фазового дискриминатора 6, а также со

вторыми входами первого, второго, четвертого и седьмого элементов И 17, И 18, И 20, И23,

Фазовый дискриминатор 6 первым выходом соединен с первыми входами первого и второго элементов И 17, И 18, а вторым выходом - с вторым входом корректора 4, выход которого через первый делитель 2 частоты соединен с первым входом блока 5 синхронизации, выход которого подключен к первым входам четвертого и седьмого элементов И 20, И 23, четвертого, пятого и шестого счетчиков 10-12,

а также первого 15 и второго 16 блоков памяти, ко вторым входам пятого и шестого элементов И 21, И 22, вто рого счетчика 8 и RS-триггера 14, и к третьему входу третьего счетчика 9,

выходом соединенного с первым ходом RS-триггера 14, выход которого подключен к входу усилителя 27 мощности, и с третьим входом элемента И 20, выход которого связан с первым входом счетчика 9, соединенного вторым входом с выходом первого счетчика 7, первый вход которого подключен к выходу элемента И 17,

Первый выход мультиплексора 13

соединен с первым входом элемента И 21, а второй выход - с первым входом элементам 22, .второй вход мультиплексора связан со вторыми входами четвертого и шестого счетчиков

10 и 12, а также с выходом первого блока 15 памяти, второй вход которого соединен со вторым выходом второго счетчика 8 и с первым входом второго элемента ИЛИ 25,

Выход второго элемента И 18 соединен с первым входом второго счетчика 8, первый выход которого через третий элемент И 19 подключен к тре тьему входу элемента И 18, Выход шестого элемента И 22 подключен к третьему входу шестого сче чика 12, выходом соединенного с тре тьим входом И 22 и с четвертым вход элемента И 22, Выход четвертого счетчика 10 сое динен с третьим входом седьмого эле мента И 23 и, через формирователь 26 с третьим входом второго блока 16 памяти, выходом связанного со вторым входом второго элемента ИЛИ 25, выход которого подключен к второму входу пятого счетчика 11, своим первым выходом соединенного с третьим входом пятого, четвертым входом шестого и пятым входом четвертого элементов И 21, И 22 и И 20, а своим вторым выходом - со вторым входом второго блока 16 памяти. Выход седьмого элемента И 23 .соединен с третьим входом четвертого счетчика 10, а также со вторым входом первого элемента ИЛИ 24, первый вход которого связан с выходом пятого элемента И 21, а выход - с третьим входом пятого счетчика 11, Устройство работает следующим образом, Б исходном состоянии на шине упра ления 30 присутствует сигнал логического О, при этом на обоих выходах дискриминатора 6 будут сигналы логической 1, а в счетчике 7 будет установлен начальный код. При поступлении . на шину управления сигна ла логической 1 (фиг, 2и) на, усилитель 27 .мощности подается питания (на фиг, 1 цепи питания не показаны) и двигатель 28 начинает вращаться, однако, пока его скорость не достигнет номинальной, состояние выходов фазового дискриминатора 6 не изменя- 45 во ется и информация о фазовой ошибке будет отсутствовать, чтобы устранить возможные сбои в работе устройства на этапе разгона двигателя. Второй делитель 3 частоты формирует ряд частот: f , f, , ij , высокую тактовую частоту заполнения также эталонную частоту | (фиг,2а) поступающую на фазовый дискриминатор Влок 5 синхронизации также формирует ряд синхрочастот: СС1, СС2 и ССЗ (фиг, 26,в,г). На структурной сЗсеме (фиг, 1) выходы различных частот с 444 выходов дискриминатора и блока синхронизации условно показаны одной линией связи, Широтно-импульсньш сигнал, пропор; циональный фазовой ошибке, появляетгся на выходе дискриминатора 6 в промежутке времени , с частотой Этот сигнал заполняется частотой на элементах И 17 и И 18, на выходах которых будут пачки импульсов, июдсчйтываемых счетчиками 7 и 8, Счет импульсов в счетчике 8 прекращается либо при прекращении поступ ления сигнала фазовой ошибки, либо при установке этого счетчика в одно из граничных состояний, причем в этом последнем случае элемент И 18 закрывается сигналом с выхода И 19. Начальный вход во второй счетчик 8 устанавливается импульсом (на фиг. 2д обозначен цифрой 3), формируемым блоком 5 синхронизации по срезу сиг-. нала СС1, этим же импульсом код, соответсТвукяцей фазовой ошибке предыдущего измерения, переписывается в четвертый счетчик 10, По концу счета код счетчика В, пропорциональный фазовой ошибке текущего измерения, переписывается в первый блок 15 памяти и в пятый счетчик 11 импульсом, формируемый по первому срезу сигнала ССЗ после фронта сигнала СС1 (момент времени t,, фиг, 2е) , По первому фронту СС2 после фронта СС1 (момент t , фиг, 2в) открывается элемент со второго делитеи частота ля частоты 3 поступает на четвертый и пятый счетчики 10 и 11, При установке счетчика 10 в нулевое состояние закрывается элемент И 23 и в счетчике 11 будет записан код, пропорциональный первой разности ошибки по фазе, Этот код переписывается второй блок 16 памяти импульсом. формируемым формирователем 26 при установке счетчика 10 в нулевое состояние, причем если код предьщущего измерения в этом счетчике бьш равен нулю, запись во второй блок 16 памяти производится импульсом 1 (фиг, 2д, моментt ) а импульсом 2 (фиг, 2д, момент 15 ), коды из первого и второго блоков памяти 15 и 16 переписываются в шестой 12 и пятый Т1 счетчики соответственно, а код первого счетчика 7 переписывается в третий счетчик 9, Формирование широтно-модулированHoro сигнала, по заднему фронту кото рого срабатывают ключи усилителя 27 мощности, изменяя при этом фазу пи-, тающего напряжения, тем самым стабилизируя фазу и скорость вращения Дви гателя 28, происходит следующим обра зом. По фронту CG3 открывается пятый элемент И 21 и частота с первого выхода мультиплексора 13 через элемент ИЛИ 24 проходит на вычитающий вход пятого счетчика 11, при установке которого в нулевое состояние закрывается элемент И 21 и открывается элемент И 22, при этом частота со второго выхода мультиплексора поступает на вычитающий вход шестого счет чика 12, При установке этого счетчика в нулевое состояние закрывается элемент И 22 и открывается элемент И 20, при этом разрещается прохождение частоты на вычитающий вход третьего счетчика 9, и в момент установки этого счетчика в нулевое сое тояние, в нулевое состояние установи ся такжеRS -триггер 14 (момент времени t , фиг. 2ж), по которому и срабатывают силовые ключи усилителя 27 мощности. Таким образом, код в пятом счетчике 11 (фиг. 2к) пропорционален пер вой разности фазовой ошибки, код. в шестом Счетчике 12 (фиг. 2л) фазовой ошибке, а код в третьем счет чике 9 (фиг. 2м) равен алгебраической сумме фазовых ошибок всех измерений. При постоянных частотах с выходов мультиплексора 13 данное устройство вырабатывает управляющее воздействие, соответствующее ПИДзакону по фазе. Так как частоты сигналов с выходов мультиплексора 13 могут изменяться в зависимости от значения кода в первом блоке 15 памяти и при изменении частот на выходе делителя 3, а от этих частот зависят коэффициенты усиления П- и Д-регуляторов, которые будут изменяться в зависимости от значения фазовой ошибки, предлагаемое устройство является регулятором с переменными коэффициентами, и оно обеспечивает, в зависимости от схемы уси лителя мощности, управление и стабилизацию скорости и фазы двигателя, а следовательно, и стабилизации скорости движения носителя изменения частоты и фазы питающего напряжения 44 либо изменение его дер 1ствующего зна-. чения. Формула изобретения Устройство стабилизации,скорости движения носителя магнитной записи, содержащее задающ й генератор, корректор, выходом связанный со входом первого делителя частоты, фазовый дискриминатор, первым входом подключенный к датчику скорости, кинематически связанному с двигателем, включенным на выходе усилителя мощности, причем первый выход фазового дискриминатора соединен с первыми входами первого и второго элементов И, вторым входом связанного с выходом третьего элемента И, вход которого соединен с первым выходом второго счетчика, а выход первого элемента И подключен к первому входу первого счетчика, отличающееся .тем, что, с целью повышения точности стабилизации скорости движения носителя, в него введены второй делитель частоты, подключенный к выходу задающего генератора, блок синхронизации, мультиплексор, третий, четвертый, пятый и шестой счетчики, четвертый, пятый, шестой и седьмой элеу менты И, первьм и второй элементы ИЛИ, первый и второй блоки памяти, формирователь и ftS-триггер, выходом подключенный ко входу усилителя мощности, при этом второй делитель частоты выходом соединен с первыми входами мультиплексора и корректора и со вторьгми входами первого, второго, четвертого и седьмого элементов И, фазового дискриминатора и блока синхронизации, который своим первым входом соединен с выходом пер-вого делителя частоты, а выходом - с первыми входами четвертого и седьмого элементов И, второго, четвертого, пятого и шестого счетчиков, первого и второго блоков памяти, со вторыми входами пятого и шестого элементов И -триггера, а также с третьим входом Третьего счетчика, выходом соединенного с первым входом RS -триггера и с третьим входом четвертого элемента И, а первым И вторым входами - с выходом первого счетчика и с выходом четвертого элемента И соответственно, ко второму входу корректора подключен второй выход фазового дискриминатора, к третьему

7

входу которого и ко второму входу первого счетчика подключена шина управления, второй вход мультиплексора соединен со вторыми входами четвертого и шестого счетчиков и с выходом первого блока памяти, второй вход которого связан с первым входом второго элемента ИЖ и со вторым входом второго счетчика, первым входом соединенного с выходом второго элемента И, первый и второй выходы мультиплексора соединены соответственно с первыми входами шестого и пятого элементов И, которые выходами подключены соответственно к третьему входу шестого счетчика и к первому входу первого элемента ИЛИ, выход шестого счетчика соединен с четвер658448

тым входом четвертого и с третьим входом шестого элементов И, а выход четвертого счетчика связан через формирователь с третьим входом второго , блока памяти и непосредственно - с третьим входом седьмого элемента И, который своим выходом подключен к третьему входу четвертого счетчика и ко второму входу первого элемента 10 ИЛИ, выходом соединенного с третьим входом пятого счетчика, первый выход Которого связан с третьим, четвертым и пятым входами соответственно пятого, шестого и четвертого эле15 ментов И, а второй выход - со вторым входом второго блока памяти, связанкЪго через второй элемент ИЛИ со вторым входом пятого счетчика.

| Устройство для управления скоростьюпЕРЕМЕщЕНия лЕНТОчНОгО НОСиТЕля зАпиСи | 1979 |

|

SU830552A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для установки и стабилизации фазового положения магнитного носителя | 1982 |

|

SU1059619A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-23—Публикация

1985-01-02—Подача